Universidad Distrital ‘’Francisco José de Caldas”

Ingenierı́a Electrónica

Parcial 1 - junio 10 de 2022

Asignatura: Comunicaciones Digitales

Profesor: Ivan Ladino

Observaciones:

El Parcial es individual, no se acepta plagio de ningı́n tipo (ver reglamento estudiantil)

El parcial inicia a las 8: 00 am de hoy junio 10 y finaliza a las 10:00 am de hoy mismo, sin embargo,

tienen 20 minutos adicionales para escanearlo y subirlo a la plataforma Moodle institucional.

Se evalúa cada punto, a partir de las explicaciones de cada paso en el desarrollo matemático y en el

desarrollo del hardware y los modelos funcionales. Es decir, que si en el desarrollo de algún punto,

solo se construyen gráficos o diagramas sin la explicación analı́tica suficiente que de fe del diseño de la

solución, la nota es 0.

El desarrollo del parcial debe ser perfectamente legible y con letra clara, se sube escaneado (NO

FOTOS), para ello usen cualquier aplicación libre (como CamScan).

Bajo ningún pretexto, se recibe el parcial por otro medio distinto al de la plataforma Moodle institucional o fuera del plazo establecido.

Enunciado del parcial

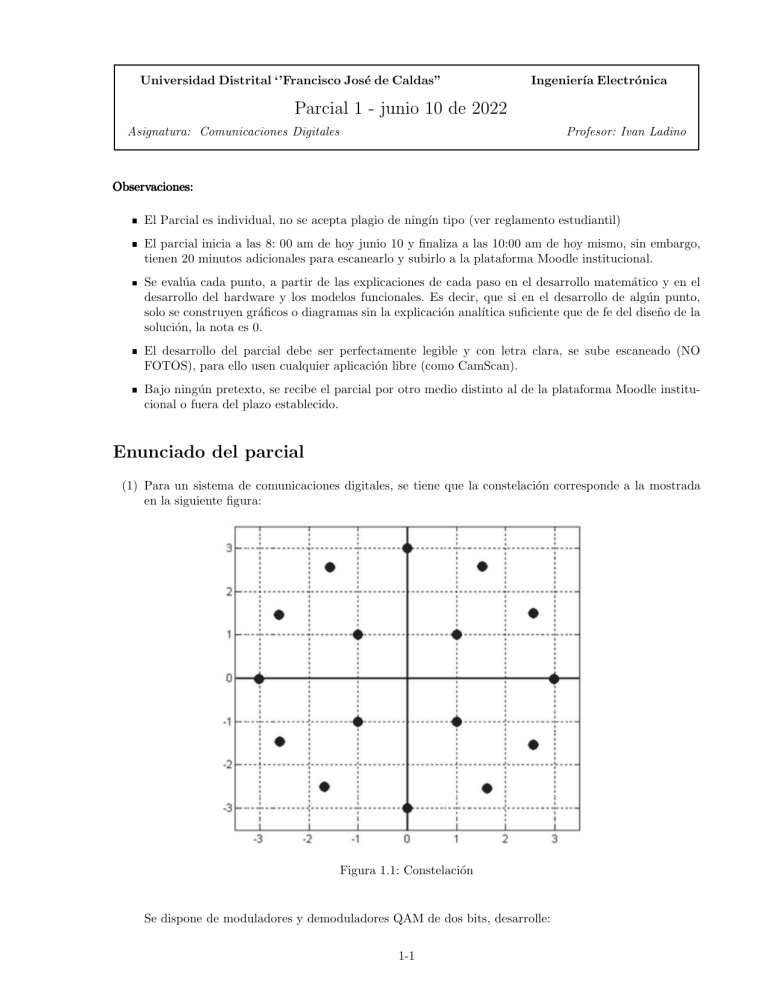

(1) Para un sistema de comunicaciones digitales, se tiene que la constelación corresponde a la mostrada

en la siguiente figura:

Figura 1.1: Constelación

Se dispone de moduladores y demoduladores QAM de dos bits, desarrolle:

1-1

(a) Diseñe con todo el detalle argumentativo, matemático y funcional el modulador para la constelación de la figura (1.1), empleando moduladores QAM de dos bits.

(b) Diseñe con todo el detalle argumentativo, matemático y funcional el demodulador para la constelación de la figura (1.1), empleando demoduladores de dos bits.

(2) Se dispone de tres señales base {ϕ1 (t), ϕ2 (t), ϕ3 (t)} para el diseño de un esquema de modulación

tridimensional. Diseñe:

(a) El modulador para una constelación de 3 bits, garantizando para todos los sı́mbolos la máxima

resistencia al ruido para una energı́a maxima de sı́mbolo de valor E.

(b) Diseñe el demodulador correspondiente al modulador del item (a).

(3) Con base en un amplificador Norton diseñe un integrador definido, donde el tiempo de integración, el

tiempo de reset y el tiempo de lectura, sean múltiplos enteros del periodo de la portadora. Se dispone

de un par de fuentes de −7v y +7v y una portadora de frecuencia de 100Khz.