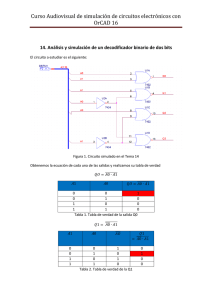

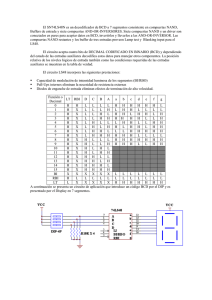

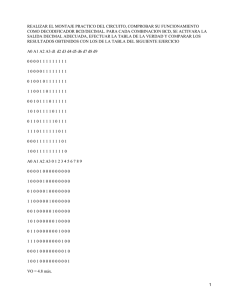

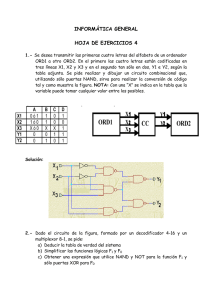

3.3.1 Diseño y aplicación de circuitos de circuitos combinacionales SSI PUERTAS LOGICAS: • Las puertas lógicas se corresponden con una relación de 1s y 0s: su tabla de verdad o su función lógica. • Los circuitos digitales se corresponden con una relación de valores altos y valores bajos. Por defecto se ha tomado la convención H # 1, L # 0, pero esta convención no tiene que ser necesariamente cierta. La conversión H # 0, L # 1 también es posible. • Todos los circuitos electrónicos estudiados utilizan como puerta básica una puerta inversora: NAND ó NOR, ya que son más pequeñas y producen mejores prestaciones. Es lógico diseñar circuitos en base a estar puertas, en lugar de utilizar puertas OR y AND. • Circuitos digitales AND y NAND. 74’08 X Y Z X Y Z L L H H L L L H L H L H 74’00 74’08 XX Y Y ZZ XX YY LL L LL HH HH LL HH HH ZZ LH LH LH L H 74’00 X Z Y Los dos circuitos hacen la misma Los dos circuitos X Y Zhacen la misma operación lógica si se considera que operación lógica si se considera que 0 0 0 en la salida del circuito 74’08: L #en 0 la salida del circuito 74’08: L # 0 0 1 0 y H # 1, y en la salida del circuito y H # 1, y en la salida del circuito 1 0 0 74’00: L # 1 y H # 0. 74’00: L # 1 y H # 0. 1 1 1 X Y 0 0 1 1 0 1 0 1 • Circuito digital NAND. También se puede conseguir que un circuito digital que realiza una operación (por ejemplo AND) lógica realice la otra (OR) en función de cómo se considera la equivalencia de L, H con 1, 0 en las entradas y salidas. 74’00 X Y Z X Y Z L L H H H H H L L H L H X Y Entradas: L # 0 y H # 1 Salida: L # 1 y H # 0. AND Entradas: L # 1 y H # 0 Salida: 0 # 1 y H # 1. OR X Y Z Z 1 1 0 0 1 0 1 0 1 1 1 0 • Se puede usar un criterio para denotar la equivalencia entre valores de tensión y valores lógicos mediante la burbuja de inversión: las líneas que no tienen burbuja de inversión tienen “polaridad” positiva (o criterio de aserción alto): L # 0 y H # 1, las líneas que tiene burbuja de inversión tienen polaridad negativa (o criterio de aserción bajo): L # 1 y H # 0. 74’00 Desde el punto de vista de operaciones lógicas esto también puede verse como una aplicación del teorema de DeMorgan, donde la burbuja de inversión representa la complementación • AB =A + B • Todas las puertas lógicas básicas pueden implementar la función AND ó la función OR en función de la polaridad que se asigne a sus entradas y salidas. • Al igual que se puede asignar una polaridad las entradas y las salidas de las puertas lógicas también se puede asignar polaridad a las entradas y salidas de un circuito, y a sus señales internas. Por lo general las entradas tienen un nombre, que indica que función hace (por ejemplo En de Enable) y a ese nombre se les puede añadir una indicación de que su polaridad es positiva: EN.H (habilita con valor de tensión H, deshabilita con valor de tensión L) o negativa EN.L (habilita con valor de tensión L, deshabilita con valor de tensión H). • • Cuando se comparan los valores de una señal como .H con de la señal como.de L una se produce una .H con Cuando se los comparan los valores señal como inversión señal como .L lógica. se produce una inversión lógica. EN.H 0 L 1 H EN.L 1 0 EN.H = EN.L • Las operaciones en una puerta lógica donde las señales tiene definida una polaridad se realiza mediante las siguientes reglas: La salida de la puerta es .L si tiene burbuja de inversión, .H en caso contrario. La puerta lógica realiza la operación AND ú OR según su símbolo. La función lógica de cada entrada pasa a la la salida tal cual si la polaridad de la entrada coincide con la indicada por la burbuja de inversión y complementada si no coincide. los de la • Se pueden utilizar estos conceptos para extraer fácilmente la función lógica que realiza un circuito digital, especialmente si está realizado con puertas lógicas NAND ú NOR. Lo que hay que intentar preferentemente es que en los nudos internos coincidan la polaridad de las lineas que generan y reciben el valor, aunque sea realizando la transformación de las puertas. IMPLEMENTACION EN DOS NIVELES: Las implementaciones en dos niveles pueden realizarse utilizando sólo puertas NAND, sólo puertas NOR o algunas combinaciones de puertas en primer nivel/segundo nivel que se pueden comportar como AND/OR (SOP) ú OR/AND (POS). Las combinaciones NAND/NAND y NOR/NOR generan circuitos SOP y POS. Para comprobar si una relación concreta de puertas en primer nivel/segundo nivel se puede usar para implementar formas SOP ó POS hay que representar las puertas de forma que entre el primer y el segundo nivel coincida la polaridad. Si al hacerlo en un nivel las puertas son OR y en el otro AND si se puede, si los dos niveles son AND ú OR no se puede. • Una vez que el circuito lógico se sitúa circuito POS ó SOP según la ecuación que se quedan establecidas también las polaridades líneas de entrada del primer nivel y de las de salida del segundo nivel. como un tenga de las líneas • Para finalizar el circuito hay que conectar las entradas del circuito a las entradas del primer nivel, por ello es conveniente expresar las entradas del circuito en la misma polaridad .H ó .L de las entradas del primer nivel, independientemente de su polaridad real. • La polaridad de la salida del segundo nivel puede coincidir o no con la polaridad de una salida, en el primer caso la conexión es directa, en el segundo caso hay que usar un inversor. IMPLEMENTACION MULTINIVEL: • Las expresiones factorizadas están formadas por un conjunto de niveles AND/OR/AND/OR/…. Las puertas NAND pueden realizar las operaciones AND y OR, de tal forma que entre nivel y nivel las polaridades de las señales coinciden por lo que las operaciones se realizan de forma natural. Lo mismo ocurre con las puertas NOR. Una vez realizadas las operaciones lógicas con las puertas lógicas adecuadas se finaliza el circuito aplicando las entradas (complementadas o no) a las líneas correspondientes, y obteniendo la salida con la polaridad correcta. 3.3.2 Diseño y aplicación de circuitos de circuitos combinacionales MSI Los sistemas combinacionales son aquellos en los que las salidas dependen exclusivamente de las entradas, luego para una misma entrada siempre se tiene la misma salida. Hasta ahora el diseño de funciones lógicas, o de circuitos lógicos, se ha realizado mediante el uso exclusivo de puertas básicas. Los circuitos que contienen estas puertas básicas son conocidos como SSI (Small Scale of Integration) por que contienen un número pequeño de transistores. El diseño que se realiza con estos dispositivos se denomina CUSTOM. Un paso más profundo en el diseño HARDWARE es realizar un diseño SEMI- CUSTOM, basado en el uso de bloques constructores más complejos. Esto se puede hecer mediante el uso de sistemas o circuitos MSI (Medium Scale of Integration) dónde el número de puertas básicas puede llegar a 100. Más avanzados son los sistemas LSI (Large Scale of Integration ~1000), VLSI (Very Large Scale of Integration >1000), y ULSI (Ultra Large Scale of Integration >100000). En un computador se realizan principalmente operaciones de codificación y decodificación de datos usando codificadores y decodificadores; transmisión y control de datos usando líneas de bus, multiplexadores y demultiplexadores; y procesado de datos mediante circuitería aritmética. En nuestro computador podemos encontrarnos los siguientes sistemas MSI: • CODIFICADORES Y DECODIFICADORES • MULTIPLEXORES Y DEMULTIPLEXORES • SUMADORES, COMPARADORES ... Además estos dispositivos pueden usarse también para la realización de funciones complejas con un considerable ahorro de área frente al uso de puertas básicas (circuitos SSI). DECODIFICADORES Un decodificador es un circuito lógico con n entradas y 2n salidas, tal que para cada combinación de entradas se activa al menos una salida. Si sólo se activa una salida se denomina decodificador completo. Por ejemplo este es un circuito decodificador completo de 3 a 8 líneas, permitiría la activación de un dispositivo al proporcionarle la dirección de dicho dispositivo. Dispone de una entrada de HABILITACIÓN (enable) que conecta o desconecta el dispositivo, en este caso dicha entrada es activa a NIVEL BAJO, ya que el dispositivo se activa cuando D0 /EN A B C D0 recibe D1 D2 D3 D5 lógico. D6 D7 A dicha entrada unD4‘0’ Bin/Oct 1 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 0 0 0 1 1 0 0 1 1 0 0 1 0 1 0 1 0 1 X 1 0 0 0 0 0 0 0 X 0 1 0 0 0 0 0 0 X 0 0 1 0 0 0 0 0 X 0 0 0 1 0 0 0 0 X 0 0 0 0 1 0 0 0 X 0 0 0 0 0 1 0 0 X 0 0 0 0 0 0 1 0 X 0 0 0 0 0 0 0 1 B C /EN Los decodificadores pueden dividirse en diferentes tipos: • EXCITADORES (DRIVERS) que controlan algún dispositivo. D1 D2 D3 D4 D5 D6 D7 • NO EXCITADORES, los que no se usan para dicho fin. Tanto las entradas como las salidas, principalmente estas últimas, pueden ser: • ACTIVAS A NIVEL ALTO: la salida activa es 1 y la no activa 0. • ACTIVAS A NIVEL BAJO: la salida activa es 0 y la no activa 1. Además el número de entradas de Habilitación puede ser de una o más, y pueden estar activas a nivel alto o bajo. Podemos encontrar decodificadores de muy diversos “tamaños”: De 2 a 4 líneas De 3 a 8 líneas (bin a oct) De 4 a 16 líneas (bin a hex) Convertidores de códigos: BCD/decimal y BCD/7-seg Ejemplo de Decodificador completo de 3 a 8 líneas: CIRCUITO 74X138 Simbolos Lógico del Decodificador, según el Standard IEEE y tradicional. REALIZACIÓN DE FUNCIONES CON DECODIFICADORES Un circuito decodificador completo genera todos los productos fundamentales (mintérminos) de las variables de entrada. Cuándo las salidas del decodificador son activas a nivel bajo, para realizar la función en suma de productos basta con conectar las salidas correspondientes a los mintérminos de la función usando puertas NAND: Z Y X VCC A B C 3/8 D0 D1 D2 D3 D4 D5 D6 D7 F G1 G2A GND G2B A veces puede ocurrir que necesitemos decodificar más líneas de las que nos permite nuestro circuito, se bebe entonces construir un decodificador de mayor tamaño usando decodificadores de menor tamaño: Por ejemplo para 4 bits (X,Y,Z,W) A B C W Z Y X 3/8 VCC G1 G2A G2B A B C G1 G2A G2B 3/8 D0 D1 D2 D3 D4 D5 D6 D7 D0 D1 D2 D3 D4 D5 D6 D7 X=0 X=1 GND CONVERTIDORES DE CÓDIGOS Son circuitos Codificadores/Decodificadores que convierten los datos de un código a otro. El circuito 74X42 es un convertidor de BCD a Decimal (de 4 a 10 líneas). El circuito 74X47 es un convertidor de BCD a 7segmentos (de 4 a 7 líneas). Permite visualizar en un display de 7-segmentos el dígito decimal correspondiente al BCD. Son circuitos drivers. Los visualizadores están formados por siete LEDs (Light Emitter Diode), que son dispositivos que emiten luz cuando la corriente que los atraviesa excede de un cierto valor (al igual que un diodo normal conduce cuando se supera una determinada tensión entre sus bornes), de ahí que para su excitación se necesiten dispositivos que proporcionen corriente suficiente. Existen dos tipos de visualizadores con LEDs principalmente. Los de ánodo común y los de cátodo común. Los primeros se usan cuando el decodificador tiene salidas activas a nivel bajo, mientras que los segundos son para los decodificadores con salidas activas a nivel alto. Otros visualizadores muy usados son los LCD (Liquid Crystal Display) que no están formados por diodos sino por una serie de plaquitas conductoras capaces de excitar un líquido que hay entre ellas. Símbolo lógico y explicación de los terminales de I/O: ENTRADAS Habil/control ENTRADAS BCD SALIDAS a display 7-seg ánodo común (conexión mediante R=150) Asignación numérica de las entradas y resultado de la visualización CODIFICADORES Son los dispositivos MSI que realizan la operación inversa a la realizada por los decodificadores. Generalmente, poseen 2n entradas y n salidas. Cuando solo una de las entradas está activa para cada combinación de salida, se le denomina codificador completo. Por ejemplo, el siguiente circuito proporciona a la salida la combinación binaria de la entrada que se encuentra activada. En este caso se trata de un codificador completo de 8 bits, o también llamado codificador de 8 a 3 líneas: I1 0 1 0 0 0 0 0 0 0 0 I2 0 0 1 0 0 0 0 0 0 0 I3 0 0 0 1 0 0 0 0 0 0 I4 0 0 0 0 1 0 0 0 0 0 I5 0 0 0 0 0 1 0 0 0 0 I6 0 0 0 0 0 0 1 0 0 0 I7 0 0 0 0 0 0 0 1 0 0 I8 0 0 0 0 0 0 0 0 1 0 I9 0 0 0 0 0 0 0 0 0 1 A 0 0 0 0 0 0 0 0 1 1 B 0 0 0 0 1 1 1 1 0 0 C 0 0 1 1 0 0 1 1 0 0 D 0 1 0 1 0 1 0 1 0 1 I1 I2 I3 I4 I5 I6 I7 I8 I9 Dec/BCD A B C D Las salidas codificadas, generalmente se usan para controlar un conjunto de 2n dispositivos, suponiendo claro está que sólo uno de ellos está activo en cualquier momento. Sin embargo, cuando nos encontremos con que se deben controlar dispositivos que pueden estar activos al mismo tiempo, problema que se suelen encontrar los sistemas microprocesadores, es preciso usar un dispositivo que nos proporcione a la salida el código del dispositivo que tenga más alta prioridad. En la siguiente página podemos ver una sencilla comparación. En la siguiente figura se representa el diagrama lógico de un codificador completo de Decimal a BCD natural, junto a su tabla de funcionamiento. /EN I0 I1 1 X X 0 1 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0otro 0 Por 0 0 0 diagrama I2 I3 I4 I5 I6 I7 O1 O2 O3 I0 Oct/Bin X X X X X X 0 0 0 I1 0 0 0 0 0 0 0 0 0 I2 O1 0 0 0 0 0 0 0 0 1 I3 O2 1 0 0 0 0 0 0 1 0 I4 O3 0 1 0 0 0 0 0 1 1 I5 0 0 1 0 0 0 1 0 0 I6 0 0 0 1 0 0 1 0 1 I7 0 0 la 0 figura 0 1 0 siguiente 1 1 0 lado representa el 0 0 0 del 0 0circuito 1 1 1 74147, 1 /ENque es un lógico codificador de prioridad de Decimal a BCD natural; en la tabla de funcionamiento adjunta se puede notar la diferencia con el anterior. /I1 /I2 /I3 /I4 /I5 /I6 /I7 /I8 /I9 /A /B /C /D Dec/BCD /I1 X X X X X X X X 0 0 1 1 0 /I2 X X X X X X X 0 1 0 1 1 1 /I3 X X X X X X 0 1 1 1 0 0 0 /I4 X X X X X 0 1 1 1 1 0 0 1 /I5 X X X X 0 1 1 1 1 1 0 1 0 /I6 X X X 0 1 1 1 1 1 1 0 1 1 /I7 X X 0 1 1 1 1 1 1 1 1 0 0 /I8 X 0 1 1 1 1 1 1 1 1 1 0 1 /I9 0 1 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 Cuando se trata de establecer la prioridad con mayor número de bits, es preciso recurrir a la asociación de codificadores. El siguiente diagrama muestra un codificador de prioridad de 16 líneas a 4, usando codificadores de prioridad 74148, de 8 a 3 líneas. /EI: Habilitación /GS: es 0 cuando el dispositivo está habilitado y una o más de sus entradas está activa /EO: salida para habilitar otro codificador de más baja prioridad /A /B /C /D 3.3.2 TEMPORIZADORES (555) ¿Qué es el temporizador 555? El temporizador 555 es un circuito integrado que se utiliza para generar pulsos eléctricos a lo largo del tiempo, es decir, es un dispositivo que es capaz de activarse o desactivarse en diferentes periodos o intervalos de tiempo que son programados por sus diferentes configuraciones. Entre sus aplicaciones más comunes podemos encontrar; temporizadores, generadores de señales e interruptores digitales. ¿Cómo funciona un temporizador 555? Aunque su funcionamiento puede variar dependiendo de cómo este configurado este dispositivo, podemos darnos una idea de cómo funciona si conocemos sus elementos principales. A grandes rasgos este circuito está compuesto por dos compradores, un flip flop RS, un transistor y una compuerta lógica Not. Los comparadores funcionan de tal manera que cuando el voltaje (V+) es mayor al voltaje (V-) mandan una señal activa, y cuando el voltaje (V-) es mayor que el V+ mandan una señal baja. El flip flop se basa en su tabla de funcionamiento que dice que si R es activa y S está en bajo la salida manda una señal positiva, en el caso contrario la salida es baja. El transistor normalmente se conecta a un capacitor que gracias a su capacidad de carga y descarga nos generan los intervalos de tiempo, por último, la compuerta Not solo se utiliza para invertir la salida del biestable. Terminales del temporizador 555 Estos temporizadores están constituidos por 8 terminales y cada un representa una parte del diagrama anterior. GND (1): Es la terminal número 1 y es en donde se coloca la tierra. Disparo (2): Esta terminal sirve para dar inicio al ciclo del temporizador. Salida (3): Aquí se conecta el componente o circuito que queremos activar. Reinicio (4): Sirve para reiniciar el circuito desde cero, si esta terminal no se utiliza es importante conectarla a voltaje. Control de voltaje (5): Sirve para modificar el Voltaje de referencia de los comparadores, es decir si normalmente el temporizador dispara con 2.5 volts, pero modificamos el voltaje de referencia a 5 volts, el temporizador solo iniciara cuando tenga una señal mayor a 5v. Esta terminal normalmente se utiliza cuando queremos modificar el tipo de señal que arroja la salida. Si no se utiliza se coloca un capacitar de 10 nf para evitar interferencias. Umbral (6): Es la terminal que establece el tiempo de temporizado. Descarga (7): Sirve para generar el tiempo de temporizado, esto mientras se descarga el capacitor que se conecta normalmente. Voltaje de alimentación: Se coloca el voltaje con el que funcionara el circuito. Configuraciones del temporizador 555 Este circuito se caracteriza por tener la capacidad de ser configurado de diferentes formas, una en donde con un solo disparo el ciclo se repite una y otra vez indeterminadamente hasta que alguien o algo lo pare(Temporizador astable, y otra en la que el ciclo se repite una sola vez por pulso).