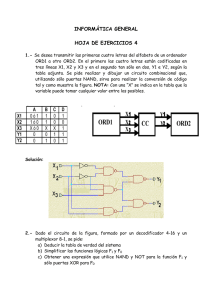

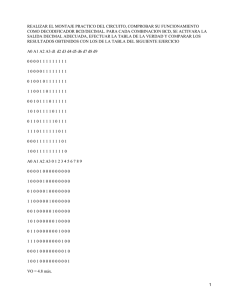

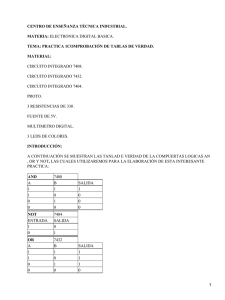

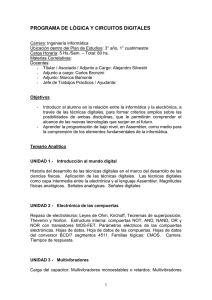

El SN74LS48N es un decodificador de BCD a 7 segmentos consistente en compuertas NAND,

Buffers de entrada y siete compuertas AND-OR-INVERSORES. Siete compuertas NAND y un driver son

conectados en pares para aceptar datos en BCD, invertirlos y llevarlos a las AND-OR-INVERSOR. Las

compuertas NAND restantes y los buffer de tres entradas proveen Lamp test y Blanking input para el

LS48.

El circuito acepta cuatro bits de DECIMAL CODIFICADO EN BINARIO (BCD) y dependiendo

del estado de las entradas auxiliares decodifica estos datos para manejar otros componentes. La posición

relativa de los niveles lógicos de entrada también como las condiciones requeridas de las entradas

auxiliares se muestran en la tabla de verdad.

El circuito LS48 incorpora las siguientes prestaciones:

Capacidad de modulación de intensidad luminosa de los segmentos (BI/RBO)

Pull-Ups internos eliminan la necesidad de resistencia externas

Diodos de enganche de entrada eliminan efectos de terminación de alta velocidad.

Función o

LT RBI D C B A

a

b

c

d

e

f

g

Decimal

0

H

H

L

L

L

L H H H H H H L

1

H

X

L

L

L H L H H L

L

L

L

2

H

X

L

L H L H H L H H L H

3

H

X

L

L H H H H

H H L

L H

4

H

X

L H L

L

L H H L

L H H

5

H

X

L H L H H L H H L H H

6

H

X

L H H L

L

L H H H H H

7

H

X

L H H H H H H L

L

L

L

8

H

X

H L

L

L H H H H H H H

9

H

X

H L

L H H H H L

L H H

10

H

X

H L H L

11

H

X

H L H H

12

H

X

H H L

L

13

H

X

H H L H

14

H

X

H H H L

15

H

X

H H H H

BI

X

X

X X X X L

L

L

L

L

L

L

RBI

H

L

L

L

L

L

L

L

L

L

L

L

L

LT

L

X

X X X X H H H H H H H

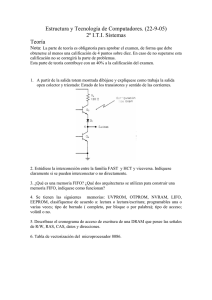

A continuación se presenta un circuito de aplicación que introduce un código BCD por el DIP y es

presentado por el Display en 7 segmentos.