146531

Anuncio

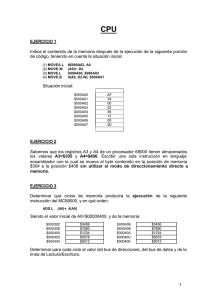

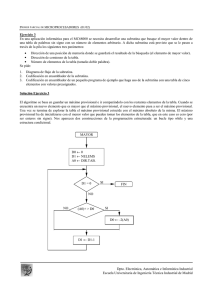

UNIVERSIDAD AUTONOMA METROPOLITANA UNIDAD IZTAPALAPA c.E', T . LICENCIATURA EM INGENIERIA ELECTRONICA .-_ Reporte d e Proyecta1 Terminal I y 1 1 . . 146531 Nombre d e l P r o y e c t o : (Diseño e I m p l a n t a c i & d e una A r q u i t e c t u r a b a s a d a en el Mi cr opr ocesador d e 1 a f ami 1 i a Motor o1 a MC68000. // Asesor d e l Proyecto: Eduardo Rodr guez F1 or es . Al umnos : 7 M i sael 1 k I ndi ce. , 1. . . Introduction General. kh 2. . -Desarrollo: 2.1. - , 2.1.1. 2.1.2. 2.2. - - Descripci4n del Hardware. Descripcion del Software. Implantación del sistema con memoria RAM. 2.2.1. 2.2.2. 2.3.- , Implantacion del sistema Minirno. - , Descripciqn del Hardware. Descripcion del Software. Irnplantacion del sistema con teclado base de teclas del t i p o Push-Button di spl ays hexadeci mal es. 2.3.1. 2.3.2. - a y 0 Descripcion del Hardware. Descripcion d e l Software. 0 2.4. - Irnplantacion del c i r c u i t o decodificador de interrupciones y detector de errores e n el bus Ccircui t o "watchdog"3 - - 2.4.1. DescripciGn del Hardware. 2.4.2. - Descripcion del Software. 2.5. - Diseño del Programa Monitor del sistema. 2.5.1 2.5.2. 3. Estrategia d e diseño. Estructura del programa Monitor - - . Resultados. 3.1. 4. - - i Problemas enfrentados en l a irnplantacion, limitaciones y deficiencias. . . Conclusiones. 5 . . -Bibliografía. INTRODUCCION QENERAL E l MC68000, es un microprocesador de 16 b i t s , siendo el diseño del mismo, l a base del d e s a r r o l l o de una s e r i e de dispositivos p e r i f e r i c o s a p a r t i r de 1979, y e3. d e s a r r o l l o de nuevas versiones como el , B8008, el 68010 y el 68020. Esta fabricado bajo l a tecnologia HMOS Chigh-density N-channel MOS, y l a circuiteria interna consta de aproximadamente 68000 transistores. Este mi~roprocesador emplea una arquitectura interna de 32 b i t s de proposito general; t i e n e 1 6 r e g i s t r o s internos d e 32 b i t s de longitud. Ocho de esos r e g i s t r o s son de datos y los otros ocho son de direcciones. E l MC68000 estuvo planeado para permitir que l a s operaciones de direcciones y datos s e ejecuten desde los r e g i s t r o s de direcciones y datos respectivamente. Ninguno de los r e g i s t r o s de datos t i e n e n funciones dedicadas, como serian para uso como acumulador o como entrada/salida. Debido a esto, l a s instrucciones pueden ser e s c r i t a s t a l que sus operandos residen en cualquiera de los registaros de datos o localidades en l a memoria. Entonces, los datos procesados pueden ser escritos en 5 diferentes tipos que son: bit, 13CDC4 b i t s > , byte, word y Long word C32 bi ts3. / Los r e g i s t r o s de direcciones estan diseñados también para uso general y no t i e n e n funciones dedicadas. La arquitectura del MC68000 incluye un poderoso numero de funciones de hardware y software: desde el punto de v i s t a del hardware, el MC68000 t i e n e un l a r g o bus de direccione? externas; e s t e proporciona yn espacio muy grande de direc+ones logicas de 1f3 Mbytes. Una funcion de software que s e ha incluido en l a arquitectura, es l a habil4dad de crear un medio ambiente usuario/supervisor. Esta caracteristica ayuda al programador a proteger el software del sistema operativo y provee soporte para aplicaciones de multiproceso y multitareas. El MC68000 puede funcionaren 7 modos de interfase: address/data bus, asynchronous bus control, processor status lines, system control bus, interrupt control bust bus arbttration control bus y asynchronous control bus. Esas l i n e a s de bus pu,eden ser conectadas a c i r c u i t o s externos t a l e s como memoria y p e r i f e r i c o s d e entrada/sal i d a . - B U S DE DATOS Y DIRBCCIONES - E l MC68000 t i e n e buses de direcciones y datos independientes. Esto s i m p l i f i c a el diseño de l a s interfases de memoria y de entrada/salida, debido a que l a s señales de ,direcciones y da$.os no necesitan ser demultiplexadas con c i r c u i t e r i a externa. Ademas, el bus de direcciones, d e datos y el espacio de direcciones de memoria, son usados para la interfase de dispositivos de entrada/salida, conjuntamente con decir , todos 1os dispositivos de memoria en el sistema MC68000. - B U S ASINCRONO DE CONTROL l a memoria del subsistema. E s entradaHsa1i da son mapeados en - E l control del bus del MC68000 es asíncrono. Esto s i g n i f i c a que una vez que un c i c l o de,bus se i n i c i a , no s e completa hasta que una señal de l a c i r c u i t e r i a externa es regresada a l 08000. Las señales que ofrecen el control de transferencia de datos y direcciones son: CAS3 address strobe, CR/YD r e a o w r i t e , C ü D S 3 upper data strobe, CLDS3 tower data strobe, y CDTACK2 data transfer acknowt e d e . - E S T A T U S DEL B U S DEL PROCESADOR Y CODIOOS DE F U N C I O N - Durante cada c i c l o del bus ejecutado por el 68000, e s t e saca 3 b i t s de codigo que indican el estatus del proce,sador. Esos codigos de estatus son conocidos como codigos d e funcio? y son s a l i d a s en l o s pines FCO-FC2. Ello? indican a l a c i r c u i t e r i a externa el t i p o de c i c l o de bus que esta presente e n el sistema, es d e c i r , el dato o el programa que estan siendo accesados y si el microprocesador esta en modo usuario o modo supervisor. - B U S DE CONTROL DEL SSSTEYA - , E l grupo de señales de control que estan etiquetadas coy0 bus de control del sistema, son usadas para controlar l a funcion del MC68000, o para indicar s u esbado de operacion. Son t r e s l a s señales de control del sistema: bus errorCBERR3, ha¿tCHALT3, y reset CRESET3. - B U S DE CONTROL DE INTERRUPCIONES - E? un sistema con, 08000, los dispositivos externos hacen l a peticion de ir+errupciop por medio de 3 b i t s que generan el codigo de interrupcion a traves de los pines de entrada IPLO-IPL2. Erte codigo se a p l i c a a l ,MC68000 desde el d i s p o s i t i v , ~ de interrupcion, el cual indica tambien el nivel de l a interrupcion e n proceso. - B U S DE CONTROL DEL B U S ARBITRARIO - Esta señal de control proporciona un mecanismo de handshake por medio del cual, el control del sistema del bus puede ser transferido entre dispositivos. El dispositivo que t i e n e control del sistema, se conoce como bus master. E s t e controla e l sistema de direcciones, datos y buses de control. -- 4 -- - BUS DE CONTROL SINCRONO 146531 - E l MC€38000 t i e n e también señales de control que pueden hacer transferencia de datos sobre e l bus del sistema ,de un modo sincrono. Hay t r e s señales de control para este proposito, e l l a s son enable CE3, valid peripheral address CWA3 y valid memory address C V M A 3 . 2. -Desarrollo. E l implementar un sistema como el que Fstamos presentando, s e hizo en varias etapas o fases de cqnstruccion, por lo cual vamos a describir brevemente cada una de esas, fases y, ayudados por los di agr amas cor r espondi entes, se i 1u s t r ar a mejor el di seso de nuestro sistema. 2 . 1 . - Implantación del sistema Animo. / 2 . 1 . 1 . - Descripcion del Hardware. E l c i r c u i t o se muestra en el diagrama #B8000-1, el cual nos muestra el sistema con el c i r c u i t o r e l o j del sistema, de reset y h a l t , de memoria ROM y para producir l a s señales de DTACK, que son generadas a partir de logica con compuertas TTL para sincronizar tanto l a s ?señales de C S Cchip select3, que en nuestro microprocesador no esta presente, por l o que hay que generarla no solamente para un dispositivo, sino para todos los que se vayan adicionando a l sistema. Esto se l o g r a a traves de un c i r c u i t o decodificador de 4 a 16, mediante €11 cual podemos seleccionar desde el bu? de direcciones CAl7-A203, y controlar los c i c l o s mediante una l o g i c a que u t i l i z a l a señal de AS Caddress strobe>, que a su vez genera l a señal MAP. Esta señal es tomada de un decodific9dor de 3 a 8; conectadas a VCC l a s entradas de seleccion, excluimos solamente a r e c i b i r l a s señales de h a l t , reset y clock; esta ultima es tomada del €38000, d e l a señal de AS, ya que el microproces?dor efectua 4 c i c l o s de AS Ccomo rutina intern? de inicializacion3, antes d e hacer un s a l t o a l a pr,imera dirycciqn de memoria donde s e encontrara l a primera instruccion que sera l e i d a . Por eso es que $ a señal de MAP esta unida a l pi,n QD del decodificador , ya que despues de cuatro c i c l o s , se activa esa s a l i d a y se sincroniza con AS para generar l a s señales ,de CS para l a s partes a l t a y baja de l a memoria ROM del sistema. A s i mismo, es generada l a señal de DTACK, que l e indic? a l CPY el estado d e l bus en el presente c i c l o , s i los datos son validos o no en el bus; en respuesta, el microprocesador lee el b i t de DTACK y hace un "latch"Cretiene3 del dato internamente y termina el c i c l o de bus. , Adicionalmente, se implanto el c i r c u i t o de refresco de memoria para conseguir que en el controlador de memoria RAM CTlG45003, haya un c i c l o de r e f r e s c o cada vez que se genere un C S d e ROM; esto asegura UT refresco de memoria cada vez que se accese a una i n m t r u c c i o n y evitar q u e haya error en l a escitura y/u en l a lectura de l o s datos. E l sistema cuenta con dos memorias d e solo lectura del t i p o Eprom 2732A, con una capacidad de :32k C 4 k x 83, teniendo un bus de datos de 16 b i t s CROM a l t o y bajo>, haciendo un total d e 64 Kbytes e n ROM. 2.1.2. - Descripción del software. Para comprobar que el c i r c u i t o funciona como s e esperaba e n el diseño, f u e necesario cargar programas de,prueba cada vez que uQa fase del sistema se terminaba; seran descritas las ma? significativas, ya que y1 software del programa monitor, ?era descrito por separado y mas completamente en otro apartado de este reporte. 2.2. - 2.2.1. Implantación del sistema con memoria RAM. - Descripción del hardware. E l c i r c u i t o se muestra en el diagraina 68000-2. E l sistema consiste de 16 chips de memoria, dispuestos en una matriz que permite l a capacidad de a l o j a r 64 KWords, siendo esta l a capacidad total de l a memoria RAM en ,nuestro sistema. E l sistema u t i l i z a un controlador de memoria dinamica d e l a f a m i l i a Texas Instruments C TMs45003 , el cual proporci ona f unci opes de acceso ef i ci e n t e , multiplexaje de direcciones, ternporizacion de los c i c l q s y refresco para todas l a s di r ecci ones de 1as memor i as di nami cas. Este controlador opera directamente desde el r e l o j del, sistema y no necesita de c r i s t a l e s o de c i r c u i t o s de ternporizacion RC, o l i n e a s de retardo. E l c i c l o de acceso-refresco esta manejado sincronamente con el r e l o j del sistema para eliminar retardos d e ,arbit,raje y pr ob1 emas de metaestabi 1i dad asoci ados con 1a oper aci on asi ncr ona de c i r c u i t o s . Un c i r c u i t o que divide l a frecuencia del r e l o j del sistema, es usado para h a b i l i t a r l a e9trada ACR y retener l a s direcciones de l a s 16 entradas que habran de direccionar tanto a l a s columnas como a l o s renglones e n l a matriz de l a memoria CCS y REN13. Si C S es seleccionado, un c i c l o de acceso a , memoria s e i n i c i a ; l a s s a l i d a s de l a s direcciones a memoria estaran presentes en los renglones de direcciones que fueron retenidos y l a señal RAS sera habilitada CRASO o RAS1 ,dependiendo del estado de RENl ; e n nuestro, caso esta señal esta en activo bajo para limitar la condicion del c i c l o de acceso3. , Una l o g i c a de t r e s compuert.as no? genera, en base a l a s señales de p,LDS y CAS, l a seleccion de l a s columnas en l a memoria y a s i e l e g i r el byte bajo o a l t o , dependiendo del formato usado a l codificar l a s instrucciones, a l a vez de generar l a señal DTACK de 1a RAM para el microprocesador , y , a par ti r del MC68000, la señal de AS, generamos ALGCaddress latch enable>, para sincronizar los c i c l o s de lectura y escritura jun$o con ACR, dado por el divisor de frecuencia del reloj. Ademas, sumamos una compuerta COR>, mas a l sistema para e l e g i r WE a p a r t i r de R/W y RASO. , 2.2.2. -Description d e l s o f t w a r e . Para l a prueba d e e s t a f a s e , se e s c r i b i e r o n dos r u t i n a s que e s c r i b e n una palabra e n .una l o c a l i d a d d e memoria, para poder comprobar l a e s c r i t u r a por m5dio d e l o s c i l o s c o p i o . Una d e l a s r u t i n a s se muestra a continuacion. ORU P R U i DIR deooo DIR FISICA O0 O2 oí O0 O0 O4 O2 O0 íñ 06 os O0 oe oe O4 20 7c OA O5 O0 O0 oc 06 OA AA 07 :, 20 O0 í2 30 3c í4 OA A5 AS 16 OB 30 80 íe oc 60 FC Stack s u p e r v i s o r . ; Direccion de inicio ;; de programa. #oAAA,AO ; LocaLidad de MOVEA. L ; RAM a e s c r i b i r . ANDi o2 7c oe o9 10 ; Diroccion d e i n i c i o de o2 O 0 O0 OE MNEMONICOS CODIUO ; Limpia status. #2OOO,SR S i g u e : MOVE. W ; PaLabra a ; escribir ; Escribe. #oASAS,DO MOVE. W DO,<AO> Sigue BRA Esta r u t i n a d e prueba e s c r i b e el d a t o ASASh e n l a l o c a l i d a d de memoria RAM OAAAh y se mantiene e s c r i b i e n d o e n l a misma. ORa PRU2 DIR deooo DIR FISICA CODIaO o2 O0 O0 o2 oí O0 O0 O4 O2 O0 16: Ob 09 00 oe oe O4 20 7c O0 OA OS O0 oc 06 06 FE MNEUONICOS ; Direccion de i n i c i o d e ; tack s u p e r v i s o r . ;: nireccion de inicio de ; programa. MOVBA. L #fOAAAAH.AO O0 OE 07 o2 7c 10 oe 20 O0 íz O9 30 3c í4 OA AS ANDX #$2000H, MOVE. W SR ; Limpia status. #$ASASH,DO AS í6 OB so eo íe oc 32 10 íA OD bo FC MOVE. W DO, (AO) Sigue: MOVE. w <AO>,D i BRA S i g u e Esta r u t i n a d e prueba e s c r i b e el d a t o A5A5H e n l a l o c a l i d a d d e memoria OAAAAH, y se mantiene l e y e n d o s u contenido. La i n s t r u c c i o n ANDI, l i m p i a el registro d e e s t a t u s d e l procesador y mantiene a l CPU e n el modo s u p e r v i s o r . I 2.3.Implantacion hexadeci mal es. del sistema con teclado y displays 2 . 3 . 1 . - Descripci An del hardware. / E l sistema cuenta con 18 displays hexadecimales con l o g i c a y 30 t e c l a s de t i p o push-button, conectados a un controlador de teclado/display C8279 de I n t e l programable3 como se muestra en el diagrama 68900-3; el controlador r e c i b e , d e l a matriz de teclas un b i t , a traves de los pines RLO-7, despues de que l a s señales de scan CSLO-23, han decodificado a l '74138 para hacer un "barrido" e n l a s t e c l a s , y de esa manera, el controlador genera l a señal d e I R Q que es p r i o r i t i z a d a en un c i r c u i t o decodificador de interrupciones. E l controlador asocia a cada t e c l a que se seleccione, un codigo deteTminado por software y entonces se efectua o t r o "barrido" a traves de l a s s a l i d a s OAO-4 y OBO-4 para el banco a l t o y bajo d e los displays respec,tivamente, decodificando el dato a e s c r i b i r a los displays a traves de un 74138 controlado por una señal de scan a los pines de bl?nking de los, displays. La señal de C S generada por el c i r c u i t o mínimo a traves del 74154, es manejada por una l o g i c a d e compuerta. para generar l a señal DTACK del controlador, i nter vi n i endo tambi en As. Para generar, l a escritura y lectura a l o s displays y del teclado, una logica desde R/W y AS del microprocesador, seleccionan la lectura y escritura sincronizando con un f l i p - f l o p y mediante l a señal de r e l o j del sistema para generar l a s señales de RD y WR que el controlador necesita para l e e r del teclado o e s c r i b i r a los displays. 2 . 3 . 2 . -Descripción del Software. Para probar esta etapa de nuestro sistema, se escribieron diversas rutinas de prueba para programar tanto el controlador dyl teclado/display, como para manipular el vector de interrupcion asociado a l a s llamadas por t e c l a del controladrr , el cual tiene que detectar cuando s/ ha hecho una interrupcion a l dispositivo desde, el teclado y asi atender esLa llamada y correr u?a subrutina especifica; el software e s c r i t o se d e t a l l a a continuacion. E l programa consta de t r e s partes: a>I n i c i a l i zaci ón b3 Pr ogr ama pr i nci pal c3Atencion de interrupción En l a parte a3, se limpia el status y s,e habilitan l a s interrupciones; se carga el vector de interrupcion, se despliega mensaje i n i c i a l y se programa el controlador 8279. La parte b3, mantiene 91 llamado continuo de subrutinas que esperan la interrupcion y despliega el dato de entrada. La rutina de obtencion $e dato, v e r i f i c a u?a bandera y espera a qu? ocurra l a interrupcio?, l a cual activara, el vector que ejecutara l a rutina que atendera a dicha interrupcion Cparte c3. 8 , E l codigo c o r r e s p q n d i e n t e muestra a c o n t i n u a c i o n : CPU 000000 "68000. TBL arriba descrito se In "MOT1 0" HOF 000000 programa al S OOlEOOOO = D I RROM: EQU OOlEOOOOH ; D i r e c c i o n d e ROM 00000600 = DIRSUP: EQU 00000600H ; D i r e c del S t a c k S u p e r v i s o r 001E0008 = INICIAL: EQU 001E0008H ; I n i c i o d e l programa 001c0002 = DRTCDSC: EQü 001C0002H ; D i r e c de comandos d e Tec/Dis oo1coooo = DATECDI: EQü OOlCOOOOH ; OOlEOlQO = CODTEC: E W OOlEOlQOH ; Tabla de codigo de teclas 1EOOOO ' ' datos de T e c / D i s p l a y ORG DIRROM ; V e c t o r de RESET DFL DIRSUP ; C a r g a d i r e c d e SSP DFL INICIAL ; D i r e c c i o n i n i c i a l de PC 000064 ORG O04H 000064 O01 EOOEC DFL INT-TEC 1EOOOO 00000000 D I RROM: 1E0004 O01 E0008 S ; A u t o v e c t o r de i n t e r r u p c i o n ; de teclado. 1E01 QA ORG 1EOlQAH l E O l 9 A CO DFB OCOH 1E019B DO DFB ODOH 1E019C EO DFB OEOH l E O l 9 D FO DFB OFOH 1E01 A2 ORG 1E01 A2H 1 E 0 1 A 2 80 DFB 80H 1E01A3 90 DFB QOH 1E01A4 A 0 DFB OAOH 1E01A5 BO DFB OBOH 1E01 AA ORG 1E01 AAH 1E01AA 40 DFB 4OH 1E01AB 50 DFB 50H 1E01AC 60 DFB QOH 1E01AD 70 DFB 70H 1E01 B2 ORG 1E01 B2H 1E01B2 O0 DFB O0 1E01B3 10 DFB 1OH 1E01B4 20 DFB 20H 1E01B5 30 DFB 30H 9 ; Tabla de codigo d e t e c l a s 146531 0004Do 0004DO BUFFER: ORG OQDOH DFS 2 * ; L o c a l i d a d para datos 1 ; de 0004EO ORG 04EOH 0004EO FLAG: DFS 2 0004E4 CONT: DFS 2 * * entrada 2 2 ’ 1E0008 INICIAL ORG ; R u t i n a de i n i c i a l i z a c i o n AND1 #2000H, SR ; Limpia S t a t u s 1EOOOC 227COOOOOOf34 MOVEA. L RrOdQH ,A l ; Carga autovector 1EOOl 2 22BC001 EOOEC MOVE. L # NT-TEC, i C Al 3 ; d e interrupcion 1EOOl 8 207C00000000 MOVEA. L #OO. A0 1EOOl E 227C00000000 MOVEA. L #OO,Al 1E0024 4EBQ001 EOOAO JSR INICIATEC. L 1E008A 4E71 NO€’ 1E002C 207C001COO02 MOVEA. L #DRTCDSC,A0 1E0032 227C001COO00 MOVEA. L dDATECD1. Al 1E0038 3OBCOOQO MOVE. 1E003C 4E71 NO€‘ 1E003E 30BCOOAA MOVE. W 1EOO42 4E71 NO€’ 1E0044 12BCOOOB MOVE. B 1 E 0 0 4 8 4E71 NO€‘ 1E004A 12BCOOOE MOW. 1E004E 4E71 NO€’ 1E0050 12BCOOOC MOVE. B 1EOO54 4E71 NO€’ 1E0056 12BCOOOA MOVE. B 1E005A 4E71 NO€’ 1E005C 30BCOOA5 MOVE. W #OASH, C A03 ; Inhibe puerto 1E0060 30BC0098 Mow.w #OQBH, C A03 ; E s c r i t u r a en RAM/Dis 1E0064 &E71 NOF‘ 1E0066 12BC0000 MOIrE.. B 1E00BA 4E71 NOF’ 1E0008 027C2000 I N I C I AL: 10 w RrOQOH ,C A03 ; Escritura en l a dir ; de R A W D i s p l a y #OAAH ,C A03 ; Inhibe puerto A #OBH,CAl3, ; Mensaje i n i c i a l ’ B RrOEH, C A l 3 ’B E C A’ ; e n display’s d e l ; puerto B #OCH,CAl3 #OAH,CAl3, ; en d i r 08 #OOH, C A l 3 B 1E006C 32BCOOFO MOW. W 1 E 0 0 7 0 4E71 NO€' 1E0072 32BCOOAO MOVE. W 1 E 0 0 7 6 4E71 NOP 1E0078 32BCOOCO MOVE. W 1E007C 4E71 NO€' 1E007E 32BCOOEO MOVE. w 1 E 0 0 8 2 4E71 NO€' 1E0084 12BC001 O MOVE. B 1 E 0 0 8 8 4E71 NOP 1E008A 12BC0020 MOVE. B 1E008E 4E71 NOP 1E0090 12BC0050 MOVE. B 1E0094 4E71 NOP 1E0090 30BC00Q8 MOVE. 1E009A 4EF9001 EOOCO JW MONI TOR. L 1EOOAO ORG I N I C I ATEC MOVEA. L #DRTCDSC ,A0 1EOOA6 1OBC0034 MOVE. B #34H, C A03 1EOOAA 4E71 NOP 1EOOAC 1OBC0008 MOVE. B 1EOOBO 4E71 NOP 1EOOB2 30BCOOD7 MOVE. W lEOOB6 4E71 NOP 1EOOB8 207C00000000 MOVEA. L 1EOOBE 4E75 R E 1EOOCO ORG 1EOOAO 207C001 COO02 J 4 1EOOCO 4E71 I N I C I ATEC: MONITOR: #OFOH ? C A l 3 ' #OAOH,CAl> ' F A C E l 2 5 ' ; en d i s p l a y ' s d e l ; puerto A w AvOCOH. C Al 3 #OEOH C Al 3 #lOH,CAl3 #20H, C A l 3 BOH'CAl3 #OQ8H, C A03 #08HpC A03 ; 10 d i s p l a y s / e n t #OD7H, C A03 ; L i m p i a Di s p l a y ' s izq ; y el S t a t u s #OO. A0 MONITOR ; Rutina p r i n c i p a l NOP JSIZ 1EOOC8 4E71 NOP 1EOOCA 4EB9001 E01 2B Jslz DESENTR. L 1EOODO 6000FFEE BRA MONI TOR 1EOOD4 ORG OBTENDATO OBTENDATO: CLR. W ; Prog. r e l o j i n t e r n o ; a 100 KHz. 1EOOCB 4EBQ001 EOOD4 1EOOD4 4240 ; Mensaje i n i c i a l OBTENDATO. L ; Llama a r u t i n a q u e ; o b t i e n e dato de t e c l a Do ; Despliega d a t o ; Rutina que se encarga 11 - . . , A . 1EOOD6 33COOOOOO4EO MOVE. W DO,FLAG. L ; de esperar una i n t e r r 1EOOMC: 46FC2000 MO’a. W #2000H, SR ; c i o n del teclado Tsr. w FLAG. L 1EOOE6 6700FFF8 BEQ ESPERA 1EOOEA 4E75 RTS 1EOOEC ORG I NT-TEC MOVEA. L #DRTCDSC,AO ; R u t i n a de 1EOOF2 227C001 COOOO MOVEA. L #DATECDI ,Al ; de i n t e r r u p c i o n 1EOOF8 30BC0040 MOVE. W #40H, C A03 ; L e c t u r a de R W F I F O 1EOOFC 1410 MOVE. B CAO3 ,D2 ; Lee el STATUS 1EOOFE 02020007 ANDI. B m7,D2 1E0102 13C2000004E4 MOVE. B D2,CONT. L 1E0108 B43C0000 CMP. B #OO.= ; Si e s t a v a d o s a l e 1E01 OC €36000008 BNE SIGUE 1E01 1O 4EFQ001E01 24 JW . SALIDA. L 1E01 16 33FCO001000004EO SIGUE: MOVE. W # FLAG. l. L 1EO1 1E 13Dl000004DO MOVE. B C A l 3 ,BUFFER. L 1EOOEO 4A79000004EO 1EOOEC 207C001 COO02 1 E 0 1 2 4 4E73 ESPERA: I NTLTEC: SAL1 DA: atencion ; R e g r e s a de i n t e r r u p - R E ; cion ORG DESENTR CLR. W Dl ; R u t i n a encargada de 1E01 28 227C001COOOO MOVEA. L #DATECDI ,Al ; desplegar el d a t o 1E01 2E 247C001 E0190 MOVEA. L #CODTEC,A2 ; de e n t r a d a , 1E01 34 1639000004E4 MOVE. B CONT. L , D3 ; decodi f i caci on del MOVE. B BUFFER. L,Dl ; codigo c o r r e s p o n d i e n t 1 E 0 1 4 0 D5C1 ADDA. L m.A2 ; a la 1EOl42 l 2 Q 2 MOW. B C A 2 3 ,CAl3 1 E 0 1 4 4 4241 CLR. 1E01 26 1 E 0 1 2 6 4241 1E01 3 A 1238000004DO DESENTR: Si GDES: 1EO146 4243 w CLR. w 1 E 0 1 4 8 4E75 RES 12 Dl D3 tecla. por la I 2 . 4 . - Implantacion del c i r c u i t o decodificador de interrupciones y detector de errores en el bus Cwatchdog3. , Este circuit,o nos proporciona l a opcion de asignar niveles de prioridad a traves de un c i r c u i t o que nos decodifi,ca hasta s i e t e diferentes señales provenientes de diversos p e r i f e r i c o s como se desee. 2.4.1. - Descripción del Hardware. E l c i r c u i t o respectivo s e encuentra e n el diagrama 88000-4,,el cual nos muestra l a s entradas de los niveles de interrupcion, conectadas a los pines 1-7D dq un 74273 Ccircuito octal de f l i p - f l o p s t i p o D3. Este c i r c u i t o se sincroniza, Junto con el 74175 a l a frecuencia del sistema C4 MHz3; despues se conectan l a s salidas Q a las entradas del circuito 74348, , que es un codificador de 8 a 3, el cual a l a s a l i d a envía 3 l i n e a s qu. son recibidas por el 74175 Cf l i p - f l o p c,uadruple> , y mediante l a l o g i c a interna y l a señal de sincronizacion del sistema, el c i r c u i t o nos proporciona las señales de, IPLO-2 que son conectadas al microprocesador , obteniendo ?si el código del nivel de prioridad de l a s interrupciones; este codigo es comparado con el valor d e l enmascaramiento de interrupciones y con el r e g i s t r o de status. E l nivel de, interrupción quq s e conectó a l c i r c u i t o , es señal de peticion de interrupcion del c i r c u i t o controlador tecl ado/di spl ay C 82793. la del Adicionalmente, se conecta ofro c i r c u i t o que, v e r i f i c a si un c i c l o de bus en proceso F e h'a completado con e x i t o o no. E l circuito, que se implanto con un 74175, se sincroniza con AS Caddress strobe3 y E Cenable3, para producir l a señal de BERR Cbus error3; esta señal, nos indica que se ha detectado una condicion d e error en el bys. Cuando se i n i c i a un c i c l o de bus, l a s a l i d a AS es mantenida a logi,ca 9 a l o l a r g o de todo el ciclo; AS s e i n v i e r t e por el 7404 y envia l o g i c a 1 a l a s entradas D y CLR; el contador es liberado y comienza l a cuenta a traves de una secuencia binaria dada por y1 pulso de r e l o j a l a s a l i d a de l a señal de enable. Si l a duracion de DTACK activa dura hasta antes d e 10002, no ocurre un error de bus; s i n embargo, si DTACK no se r e c i b e , l a entrada BERR es switcheada a O y una excepcion de error d e bus ocurre. Por l o tanto, vemos que el c i r c u i t o watchdog observa todas l a s actividades y asegura que todos los c i c l o s de bus que s e i n i c i a n se terminen. , , Las señales de FCO-2, pasa a traves de una l o g i c a de compuertas AND y NAND, que junto con AS y Al-A3 a l a entrada de un 74138, nos entrega l a señal de W,ACvalid peripheral ?ddress> l a cual reconoce que el sistema esta trabajando en algun modo de operacion dado por FCO72. A s u vez, a l a s a l i d a de l a compuerta NAND, se toma tambien la señal para el C S con modo de inteTrupcion que es incluida a l a entrada del , c i r c u i t o 74154 a traves de una compuerta OR y junto con MAP a traves d e 2 inversores a l a entrada de G1 y G2 sincronizando con AS Cdiagrama 68000-1>. 2 . 4 . 2 . - Descripción del software. Las rutinas de, prueba ,para l a parte de l a decodificación d? interrupciones, esta incluida en el apartado 2 . 3 . 2 , ya que f u e necesario sumar est. software para lograr que el teclado t r a b a j e en modo por interrupcion. 2.5. - Diseño del programa monitor. Este ,programa fué diseñado inicialmente tqmando en consideracion direcciones v i r t u a l e s para un sistema minimo; las modificaciones pertinentes fueron hechas conforme l a acquitectura desarrollada se implantaba. El resultado no fue probado completamente por l a escasa cantidad de recursos con los que contamos para l a prueba del hardware y software, entre l o s que podemos c i tar ensambl ador es y emu1 ador es. 2 . 5 . 1 . - Estrategia de diseño. Este programa es basicamente un programa de depuración, con caracterist i c a s propias del sistema hardware del microkit basado e n f a m i l i a MC68000 de motorola. E s r e f e r i d o como un programa monitor y provee t r e s capacidades fundamentales: a> Cargar un programa en memoria RAM. b3 Ejecutar un programa. c3 A u x i l i o en l a depuración. En esta primera f a s e se ha diseñado en programa fuente, tomando e n consideración como hemos mncionado l a s c a r a c t e r i s t i c a s propias d e l sistema en donde sera implantado finalmente en memoria ROM, en codigo objeto de lenguaje ensamblador MC68000. La dirección de i n i c i o del monitor es $7C0008 E l sistema monitor estará operando en modo supervisor. Los programas de usuario serán cargados en codigo objeto desde el teclado del sistema, y estos pueden ser ejecutados por t r e s modos de ejecución: en corrida l i b r e , por puntos de ruptura y en paso a paso, logrando con esto una e f i c a z ayuda e n l a depuración de los programas. En general, el monitor permi t.e i n i c i a l i z a r localidades de memoria y r e g i s t r o s del procesador, incluyendo el r e g i s t r o contador de programa, asi como tambien permite desplegar el contenido de localidades d e memoria y r e g i s t r o s p o r el usuario. En corrida por puntos de ruptura y en paso a paso s e activan rutinas que despliegan el contenido actual de los r e g i s t r o s del procesador , lo que crea un a u x i l i o primario en l a depuración y prueba de programas d e usuar i o. Los comandos del Monitor son dados por t e c l a s asignadas para r e a l i z a r funciones especi f i cas. Todas 1as di.recci ónes y conteni dos estan dadas en hexadecimal a menos que se indique otra cosa. Los r e g i s t r o s del procesador son designados por s u s nombres simbol i c o s ostandar : Do, Di, . . ,D;, para l o s registros d e datos, A o , ~ ,. .. ,A;. para l o s reyistrcs d e direccidnes, SR para . 14 _--"I u - - w - ~ - P el registro d e estados y PC para el contador d e programa. Tabla d e teclas y su función: Tecla Codigo Función '0': '1': '2' : OAh OBh ' A ' : 'B' : 'F' : 'Sig' : ' RegDat ' : 'RegDir ': ' RegCCR' : ' RegPC ' : ' DirMem' : 'Mod': ' Li mp' : ' Pasopaso' 'CorLib' : ' Enter ' : : OFh 1Oh 11h 12h 13h 14h 1s h 1o h 17h 18h 1Qh 20h Siguiente registro Datos Direcciónes '9 9' CCR 9' Pc Memor i a Modificación inicializa contenido Corrida paso a paso Corrida Libre En t er * Programa fuente del sistema nmnitor MONMAC del microkit MK-68-00. DirRom: Iniciak EQU EQU Stksup: StkUser: EQU EQU KbDiCom: EQU EQU EW KbDiDatos: RegMdSup: BRKPNT: PasoBK: * Direccion de memoria ROM Dirección inicial del sistema monitor. Dirección de stack supervisor. Dirección de stack usuario. Direccion Teclado/DispLay comando. Direccion TecLcrdo/DispLay datos. Rutina de regreso a modo supervisor. Rutina de atención a BKPT. Rutina de paso a paso. EQU EQU Define vectores de trampa. $014H ORG Dc. L IntDivZ ORG $0241-1 Dc. L ORG Dc.L ORG Dc. L ORG Dc. L PQIOBK SO64n Inter- tec ' Vector de división por cero. Vector interrupción de Paso-Paso Valor de interrupcihn del tecl- $080~ BRKPNT Vector O de trampu en Breakpoint $OBCn RegNdsup Vector de trampa a modo Supervisor. * Asignación de c o d i g o ORG TabTec: L)c=.B Q $0450~ $00 E . B $08 $11 ORG $458 Dc. B $08 E . B E. B $01 E . B $12 ORG $460 $02 m.B DC.B DC.B ORG X . B $OA $13 $488 $03 D ~ . B $OB E . B $14 =.E $18 ORG DC.e $470 $04 E. B $OC K . B x . B ORG $480 $06 E . B $OE E . B $17 ORG $488 $07 E . B Dc.B Dc.B ORG * $15 $19 X . B 146531 teclas. $OF $20 Codigo t e c l a : ' O ' tecla: '8' tecla: RegDat ' tecla: tecla: tecla: 'f' tecla: tecla: tecla: '2' tecla: tecla: tecla: tec l a : '3' tecla: tecla: tec l a : tecla: '4' 'C' ' DirMem' 'Coriib' tecla: tecla: tecla: tecla: '5' tecla: tecla: tecla: '6' 'E' '9' 'RegDir' 'A' ' RegCCR' 'B' 'RegPC' ' Paso-Puso' 'D' 'Mod' 'Siga 'Limp' tecla: ' 7 ' 'F' tecla: tecla: 'Enter' f7C0000 Rutina de i n i c i a l i z a c i ó n de pa.rametros del sistema. Dc.L E. L ORG StkSup XniciaL IniciaL i n i c i a l i z a d i r e c c i ó n de SSP D i r e c c i ó n i n i c i a l d e l PC JSR JSR IniRegUa Monitor JMP END ORG * * Inicializa tec lado/display IniTec/Dis Fin de Inicial inineguo Inicializa contenido de l o c a l i u d e s asignadas a los regis ros de datos, direcciónes, CCR y PC para el usuario. IniRegUa: RopitíP. MOVEM. L A o , -C S s p 3 MOVEA. L #0400x, Ao Preserva contenido de registros. Carga dirección de registros. CLR. L MOVE. L CMP. w %LE Palabra inicial a registros. Escribe I& incrementa a l sig. Continua inicializando hasta terminar. Reestablece ambiente. Do Do ,C A03 + #0444n, A0 Repitie MOVEM. L CSSP>+,Ao RTS END ORG * * * RESET JSR DocMenln JSR ObtenDato TocLa,ih MOW. B MOW. B JSR * Monitor R u t i n a principal que se encarga de recibir y asignar el comrrndo seleccionado por el usuario. A l terminar La opción deseada el programa regresa a esta parte del monitor. Monitor: * Finaliza IniRegUs Inicializa perifericos. li&m a rutina de Mensaje inicial. D0.k AfaigCorn Monitor BRA END Comando- Princ ORG AoigCorn R u t i n a que atiende L a petición de comollsdo asignando l a correspondiente por llamada. $11X,Dí Si tecla = 'RegDat' SaLta atención comando Si tecla = 'RegDir' Salta atencibn comrrndo Si tecla = 'RegCCR' Rutcorn- í $12x.Dr Rutcorn- 2 $13w,Dí Rutcorn- 3 $14x,Dí Si tecla = 'RegPC' Rutcorn- 4 Si tecla = 'DirMem' $15X,DL Rutcorn- O $16X'Dí Si tecla = 'Mod' Rutcorn- 6 Si tecla = 'Limp' $17n,DL Rutcorn- 7 1'7 I I i 1 CMP. B $18w,Di BEQ Rutcorn- 8 C W .B $1QH,h BEQ Rutcorn- P JSR TerAoig RegPatom Tor Aoig RogDiroc Ter Aoig JSR Rutcorn- 2: JMP JSR JMP JSR Rutcorn- 3: Rutcorn- 4: RegCCR TorAsig Reg- PC TorArig JMP JSR Rutcorn- 5: DirocYern Tor Aoig iwodifica TorAoig JMP JSR Rutcorn- 6: JMP JSR Rutcom- 7: Rutcorn-8: Rutcorn- p: T e r Asig: . Limpia JMP JSR JMP JSR RTS END TerAsig PcuOPamO TerAmig CorLibro FinaLiza A s i g n a comrrndo. DoeYonIn ORG * Si tecla = ’CorLib’ Error JMP JSR JMP Rutcorn- 1I Si tecla = ‘ P a s o P a s o ’ Despliega mensaje inicial. DeoMonIn MOVEA. L Meno-Ini.-C A73 @OH, -C A73 MOW. B MOW. #MAH, -C A73 Mensajes JSR #8, A7 SUB. L Dirección de mensa3‘e Q ser Escritura en la dir O0 de R A M d i s p inhibe puerto A desplegado inicialmente. V a c i a el SSP RTC ORG *t * Rutinu que espera de entrada. ObtonDato: QbtenDato CLR. w MOVE. w MOVE. w EoporQ: TST.W BEQ JSR interrupcion del teclado para obtener un &to UM Do Do’FLcrg #2000x* SR FLag Espera TabTocLae RTS END ORG Finaliza ObtenDato Intor- Tec * Rutina que atiende interrupcion de teclado, y obtiene un d a t o del m i s m o ComocnaO de lectura de R A M FiFO Lee el S t a t u s del 8279 Verifica que hay datos a Leer Si FIFO vacio no lee Leer: Regresa de atencion de interrupcion. Final i z a Inter-Tec ORG * TabTecLaa Rutina que obtiene el codigo asignado a cada tecla pulsada. TabTedas: mVEA. L MOVE. LEA Carsa direccion de tabla de teclas Obtiene direccion de tecla OCAi,Do. ~3 ,A4 Obtiene codigo correspondiente. TabLaTgbcLCr0,h B TecLa,h RTS ORG * RegDatoo Rutina que atiende operación sobre registro de datos de usuario. RegDatoo: MOWM.L MOVE. MOVE. JSI? B MOVEM RTS END ORG * Preserva contenido actual de reg. D i , A i Di &DAW, -C A73 Carga mensaje a desplegar. #1 ,BanDatDi Pone bandera de registro de d a t o s . Oper- Regiotroo Llama rutina que opera en registro. C A73 + ,&/Ai Restablece contenido de reg. Di, A i Di/Ai,-CA73 CLR. v Final i z a Regktos. Reg- Direc Rutina que atiende operaciónes sobre registros de direccidnes de usuclrio. RogDirec: MOVEM CLR. w MOVE. B MOVE. B JSR MOWM RTS END ORG D í / A í , -C A73 Preserva contenido actual. Di &e, -C A7> #í? ,BanDatDi Oper- Regiotri>a C A73 + ,Di/Ai Carga mensaje a desplegar. Pone bandera de reg. de direcciónes Llama rutina que opera en registro. Reestablece contenido. Final i z a RegDirec Reg- CCR 19 * R u t i n a de operaci6n sobre registro CCR de usuario. Do-Dz/Ao-Az/CCR, -C A73 P r e s e r v a contenido de registros. KbDioCom.AO KbDioDatoo,Aí r;toD7w,C Ao3 #OAAH,<Ad &OH, C A03 #OCCH, o< Aí3 . #OA~H,(:AO~ #OQIAi, C A03 # 4 4 0 ~ Az , <A23,Dí Limpia el statzls/RAM display Inhibe puerto A Escritura en direc O0 de R A M Inhibe puerto B Escritura en dir OD de R A M dis D i r memoria CCR Obtiene contenido actual de CCR y Lo despliega. Byte atto Corre 4 b i t s a La izquierda Byte b a j o Obtiene comando de teclado &,CAL) #4,Dí h,CAí3 ObionDaio Toda,& ah, C A03 #16H.h Si es z = i entonces modifica contenido ac tuaL Otro si es igua~ Limpia contenido YodRgCCR 11$17,m #ctwrL. otro, termina operación. LimpCCR Term- CCR a BandErr &DH, C A03 Obtiene nuevo dato d.e tecLado ObienDaio TecLa,b #20H,Do Si es 'Enter' termina Term- CCR VeDa: H e x #1 ,BandErr Otro verifica que sea dato hexdec si IZO termina operacidn Term- CCR D0,h Dí,CAí> #4,h D0,h Dí,CA2:, Repiií7 #O, CCR DespLiega dato nuevo de entrada Corre a ¿a izq. en cuatro bits. Inserta nuevo dato en medios byte Con t i nua Leyendo . Limpia registro con O 0 #o,cAz3 C A73 + ,D~-&/AO-AZ/CCR Res tab Lece Finaliza Reg C€R * * Rutina para modificar el contenido d e una direccion de memoria Compl: Comp2: EQU EQU ORG SOOFFFFFFH ~OOOOFFFFH DtreoMem regis t ros. DirecYem: Ropitii MOVEM. L MOVEA. L MOVEA. L CLR.L CLR. L B ME.B MOVE. w MOVE. B LSR. w MOVE. B MOVE. B RopitiO JSR mVE. B DO-D5/Ao-A2,-C A73 Preserva registros en stack KbDinCom,AO KbDinDatoo,Ai Dz Band- Err #OD7x, C A03 # O m C A03 #OEODx, Do DO'CAi3 @,DO DO'CAi3 &Ox, C A02 ObtenDato Limpia status/RAM display Inhibe puerto A Despliega 'DE' Despl i ega by te bajo Corre 8 bits a La derecha Despliega byte alto Escritura en dir 00 de R A M dispLay Lee dato de entrada TocLa,ib #1SX,Do Si tecla = 'DirMem' entonces saLta con dirección inicial Otro verifica que sea ?xexa.decimaZ Si hay error regresa a leer Dir- I n i VoDaiWox #I 'BandErr Repitií DO'Di Di'CAi3 Despliega entrada Corre a la izquierda cuatro bits corre a la izquierda un byte Carga nuevo byte Obtiene solo medio byte Actualiza nuevo contenido regresa a seguir leyendo Carga dirección iniciaL #4'Di Di'Dz #4,Dz #cornp2,Dz RopitiO -.A2 Dz,Ds @8n, C A03 #OASIS, C A03 CAZ2,ck #4' D5 ck'CAi3 Escritura en dir 08 RAM display ínhibe puerto B Despliega contenido actual DespL iega Corre 4 bits a la derecha #4,& # 'Ds l #oo,Ds Continua& Carea contenido de memoria CAZ3 'Dz Repiti2 Band- Err ObtonDaio Lee nuevo dato Tecla,% DO'Di # 2 0 W ' Di Si tecla = 'Enter' entonces termina de modificar Otro si tecla = 'DirMem' entonces obtiene siguiente direc Otro si tecla = 'Limp' entonces 1 impia contenido Otro verifica que sea hexadecimal 5i b y error de entrada reSresa a Leer TorDirlle #lSH*Di SigLocYo #17x,Di LimpDir VoDatHex #1 BandErr RopitlZ & 8 ~C A03 21 MOVE. B La.B LSL. L DA,CAd #4,h #8,h MOVE. B h,D2 #4,Di? LSF?.L AND. L SigLocMo: Continue: BRA MOVE. w MOVE. L #1 ,Ik BNE BRA Continua MOVE. L MOVE. B MOVE. B * MOVEM. L RTS END Desp l ie g a m,m Repitis #OO,CA23 rrcOA51-1,< A03 #OiSi"i, C A03 C A73 + ,Do-Ds/Ao-A2 Limpia contenido de memoria Inhibe puerto B Limpia puerto A, status/RAM dispLa Rest abLece registros. FinaL iza modifica memoria Rutina de atención a ej'ecución de programa de usuario en corrida Libre. ORG CorLibro: MOVE. w JSR MOVE. w CorLibro SR, - C s P 3 SaLtciPc CSP3+,SR RTS END * * Inhibe puerto A #4,b SUB. B c m .B TerDirMo: D2,<A23+ h,Ds &OH, < A d B MOVE. B &AA€€, < A03 MOVE. B #4, Ik Ds,<Al3 MOVE. B LSR. L LimpDir #~ornp~,L);L Repiti2 otro despLiega entrada Corre a La izq. cuutro bits. Corre a La izq. un byte Inserta nuevo byte y corre cuatro bits a La derecha actuaLiza nuevo contenido Regresa a seguir Leyendo G u a r d a nuevo contenido y obtiene Preserva contenido actuaL del status Llama a conceder La dirección de2 PC ReestabLece registro de status. Finaliza CorLibre Rutina que concede La dirección de inicio de programa usuario aL registro PC para su ejecuci6n. S aLt crpc: MOVE. L MOVE. L JMP TRAP RTS END d< pc3 ,-< -3 &O,SI? C DirMomPC> #1 b Preserva PC en s t a c k supervisor. Concede 01 estado usuario <bit S=O> Salta a programa usuario. Regreso a estado supervisor. Finaliza saLto a usuario. , I i I1 I * * Rutina de atención a comLTnd0 de ejecución de Paso-Paso, vector' de interrupción por Trazo. ORG PaaoPaoo: MOVE. w JSR MOVE. w MOVE. w JW TRAP RTS Concede ejeczrc i6n RoootubLoce e t a t w Csp>+,SR Finaliza Paso a Paso EjecPaeo ¿C PC> -c usP3 #8000, SR C DirMemPC3 # 5I END * * Preserva dlreccidn de retorno Bit de status T = 1 , S = O A programa de usuario Trampa de regreso o supervisor Finaliza ejecucidn de paso Rutina que opera en cualquiera de los registros de uso general <Registro de datos o direcciones) ORG Oper- Rogintro: MOVE. L Oper- Rogiotroo C A73 +, Di KbDioDatoo,b Obtiene mensaje a desplegur Dirección de tec Lado/display. BandErr h'CAí3 Despl iega mensaj'e Lee numero de registro. Llama a verifica entrada Verifica si hay error de entrada. si error regresa a leer ObtenDato Vernato BandErr Repiti Tecta, ih D0.h Preserva registro de entrada Despliega nwnero de registro. Di* c A í 3 ObtenDato - 2 0 , D0 Si tecla = 'Enter' continua otro lee nuevo registro Despliega registro seleccionado Lee comLLnd0 de operacidn. Sf 'Enter' termina operación. Repit4 R e p i t í :i Repit6 I Preserva status en stack supervisor Ejecpaao ORG MOVE. L I t I SR. - C s P > Rutina que concede le ej'ecucibn de Paso a Paso EjecPumo: i PcLo0Pcro0 RTS END * que utiliza el DeoConRg ObtenDato #CR'DO Term- Opera #$16*Do YodConRg #$17*h L i m p i a - Cont #$lO,r)Q Satis #1 *Di #@,Di 23 Si tecla = 'Mod' entonces salta a modificar otro si tecla = 'Limp' entonces salta a limpiar registro otro si no t e c l a = 'Sig' entonces salta a regreso otro obtiene siguiente reg. I 1 4 I 1 cw. B BNE MOVE. B -at&* Scrtt3 Term- Opera -* BRA &'Di l r p L C 0 . 1. BRA RTS END Repit3 Finaliza operacibn en registros. MOVE. B Teda, m.B JSR TerVer TerVer Error Otro error Dz BEQ . . '7'. Carga dato de entrada en 02. Corre medio byte a la derecha. Compara c o n cero 02 Si igual, dato es de * O ' . . . '7' & #3,Dz LSR. B RTS Rutina q u e verifica que el dato de entrada sea un digito hexadecimul. VeDcrtHsx ma.B BEQ TerVoDh Error JSR TerVoDh Carga dato de entrcrda en D2 Corre medio byte a La derecha. Compara c o n cero O2 Si igual, dato es hexadecimal Otro error Do*#4,Dz Dz L s .B TST.B * saM4 Rutina que verif ica que el dato de entrada este entre ' O ' . VerDato * 146531 # 8 ,Di RTS Rutina que envia mensaje de error Error Carga direccibn del mensaje de error Carga comando de limpiado n de inhibir puerto A L l a m a a desplegar 'EFF' = ERROR P o n e bandera de error. 9, * Rut ina que despl iega mensajes. Yeniajos ORG Wonrajor L-Dz/Ao-A2, --C A73 MOVEM. L MOVEA. L A7,Ao MUVEA. L #1 Axc sp> +, A2 MOVE. B Csp3+,Dí @VE. B MOVEA. L MOVEA. L MOVEA. L MOVE. B MOVE. B MOVEQ. B MoWQ. Sig- Des C m .B BEQ MOW. Csp3+,Dz Ao ,As, KbDinCom,Ao KbDisDator,h Envia primer cOmQnd0 Envia segundo comando Carga codigo de f i n de mensuje. &,A0 Dz,Ao e o n , Dz #o,& Si TLO es f i n de mensaje continua otro CQSO termina Despliega por byte CA23 ,Dz Term- Mons B Salva registros en stack superv. Salva direccion actual de SSP Carga direccibn de mensa3.e Obtiene comando de escritura Obtiene comando de inhibicion Regresa direccion & SSP CA23+,Di 24 Term- Meno * * MOVE. B BRA MOVEM. L RTS END Sig- D e s CA73+,Dí-B/Ao-h Envia mensa3'e Continua desplegando Restablece registros. Fi na li z a mensaj'es Rutina que despliega el contenido de un registro general de uso en modo usuario. ORG DeoConRg: DeoConRg MOVEA. L MOVEA. L MOVEA. L ma.B MOVE. B ASL. B cw. B Dir- Adr BNE MOVEA. L JMP MOVEA. L MOVEA. L MOVE. B ma.B Sigue Ai, -C A73 KbDioCom,AO T a b T e d , A2 Carga dirección de registros Despliega en l a dir 08 de R A M disp ínhibe puerto B Mu1tiplica operando por cuatro. Verifica si es a reg. de &tos. C A03 #ASH * C A03 -8, #2* Dí #i ,BandDtDr Dir- Adr OCh,Dí.B>,& Si cierto obtiene direc. reg. sigue 2 0 C h . h . B3 A?, KbDiaCom,AO #98~ C A03 , #ASH, C A03 CAS3+,Dí Dí,CAí3 MOVE. w CAS3+,Dí MOVE. w Dí,CAd MOVEA. L C A73 +, Ai RTS END MOVE. w mwp. w ORG * Di,CAi3 Otro obtiene registro de direc. Despliega dir 8 R A M display ínhibe puerto B Carga contenido de registro. Finaliza despliega registro ModconRog Modificación al contenido actual de un registro de &tos ModConReg Repitis MOVE. L -CA23 ,Ds MOVE. L CLR. B h,Db JSR cm. B BEC! JSR cm. B BNE JSR saltal. TerModRo USUCIX~Q o direcciónes. Qbtiene contenido actual de registro BandErr ObtenDato Lee nuevo &to Si 'Enter' termina modificación #SOH, Do TerModRe VeDatHex # ,BandErr l SaLtaí DoepConReg RepitíS Verifica nuevo &to hexadecimal. Si es correcto s a l t a otro sigue desplegando el mismo y regresa. BRA MOVE. B Do,CAI3 LSL. L #4,b ADD. L D0.h BRA Repiti5 MOVE. L b, MOVE. L DS,CA23 Corre contenido actual para nuevo dato, por medios byte. regresa o leer siguiente &to. Actualiza nuevo contenido. 25 RTS END * * Termina modifica contenido registro Rutina que Limpia el contenido de un registro de datos o direccio es especificado, desde l a r u t i m que 10 esta solicitando. ORG Limpia MOVEA. L ASL. E cm. B BNE MOVEA. L LimRegA TermLimp JMP MOVEA. L MOVE.L M0vE.L MOVE. w Limpia C a r g a dirección de registros vsvario #Q~QOH, A*. e* Di Multiplica operando por cuatro. # ,BcrnDcrtDi I Verifica si es referencia a registro de datos si cierto obtiene registro LimRogA OCAi,Di. n3 ,Az TermLimp 20CAí,Di. s3 ,Az #OO,CAz3 otro es referencia a reg. direc. L i m p i a contenido del registro. cA23,Ds C h 3 ,CAo3 RTS * END ORG * * Finaliza rutina de limpia. Reg- PC direccio'n inicial del progruma de usuario. L a modificacio'n sera cargada en l a localidad de memoria O4OOh asi#mxda al registro PC. Reg- PC MOVEM. L MOVEA. L CLR. L MOVE.L Repitie JSR MOW. B -cw. B Term- PC Do -Dz/Aí, -C A73 #O444H, Ai Dz CAí3,Dz TecLa,ih #2Q, DO BEQ Term- PC JSR VeDaiHex TST.e BNE Ban¿Err Repiti0 M0VE.B Do,& LS1. L OR. e BRA MOW.L * QbtenDcrto Repitie Carga localidad del registro PC Obtiene contenido actual del registro PC usuario. Obtiene nuevo dato. * Si 'Enter' entonces finaliza * modificacio'n del PC. * Verifica que el dato de entrada * sea correcto. #4,Dz Di,& * * * * Dz,CAí3 * MOVEM. L C A73 +, Do-Dz/Ai RTS END * * Corre a La izquierda contenido actual para introducir el nuevo dato Guarda nuevo contenido del PC * Finaliza Registro PC * * Rutina de atención a comando de corrido por bloque, generada por U M instracción de BKPT CBreakpoint>, y atendida por vector de interrupción No.0 ORG MOVE. B MOVE. B MOVE. B Monoajoo ObionDaio Toda, MOVEA. L MoVEA. L MOEA. L JSR JSR EopCom: cm. B BEQ MOVEQ MOVE. B M0VE.e contenido de registros usuario Si tecla = 'TecDat* despliega solo registros de datos. #11H,Do DerDaiBK #6,h otro despliega registros dirección #QOx,CAo3 #OAAx,CAo3 MOw.B #Oh,c&> M0VE.e CAí3 #OFFw,Da NOP DBRA DBRA LoopReií: cw. B BEQ CW. B DooDaCBK: dsspl iega 'AD' despliega numero de registro. contenido de registro Espera a despLegar siguiente regis tro 11 Da,Loopneií , I)r LoopDir Obtiene siguiente registro. Si tecla = 'Tecüir' solo despliega registros de direcciónes Otro despliega registros de direcciónes y datos. #12H,Do TermBK #llX,Do BNE ObiDai ADD1 #lC,CAz> MOVEQ #7.& MOVE. B #QOx,CAo3 MOVE. B #OAAW,CAo> MOVE. a #ODAn,CAí3 MOVE.B W,CAí> MOVE. B &8w, C A03 MOVE. B #OA5x,CAo3 ObtDai: LoopDai: LOOpRet2: TormBK: * * en display Espera comando para desplegar MOVE.B &,CAí> M0VE.t CAZ>+, LoopDir: MOVE. L MOVE.B NOP CAz>+,CAí> #OFFx,Da DBRA DBRA MOVEM. L RTE END DS,LoopRoiZ Despliega ' D A ' *s numero de registro despliega contenido de registro , I)r LoopDai C A?> + ,Do-ih/Ao -A6 Obtiene siguiente registro rees tab l ece regis t ros Finaliza BUPT Rutina de servicio de interrupcibn por trampa para el regreso a modo supervisor y guarda registros de w u a r i o en memoria. ORG InTrmpíS => MOVE. L A6, -c Preserva información de usuario. MOVEA. L #RogUo,A6 Direccidn de registros de usuario MOVEM. L D ~ - D ~ / A o - A ~ , C A ~ > + G u a r d a registros de WU-¿O InTrmpi5: - 27 - I BRKPNT Do-D;I/Ao-Ao, --CA73 Salva registros en stack supervisor A7,Az A 2 c o w apuntador de stack local KbDisCom.AO Mensaje a desplegar de BKPT MonBKPT,-c A72 Limpia display #OD7x,CAo3 Inhibe p e r t o A #OAAW,CAo3 MOVEM. L BRKPNT: ' _L I I MOVE. L ADDA.w MOVE. w AND1 M0vE.w cP>+,cA6>+ #04,A6 CSP3+,CA6>+ #S7FFF,SR SR,-csP> RTE END * &tina InTDivl;: ORG MOWZ. L INLDiv5 SFFFF ,Do Di Bid: MOVE. L TerDiv5 #7FFFx, Do RTE Tablas d& mensajes de despliegue ORG Wens- Ini: E.B Yen.- E.B E. B Dc. B Dc.B END ORG Mono- Err: ini #OFn Dc. B E. B Dc. B Dc. B Dc. B ORG * * * * * Pone Do en Negativo Si Di < O entonces Termina Otro pone Do como positivo Finaliza vector division por cero. END * Inserta modo supervisor Reestablece el sistema en modo supervisor' y carga en PC dirección de regreso. Finaliza servicio de interrupción. vector de interrupción de división por cero. TST.L TorDiv5: Guarda registro CCR usuario #oh nOCn #~EH #O1w #20W Mensaje inicial al encendido y en regreso a Monitor: F A C E 1 ' Codigo de fin de mensaje Finaliza t a b l a de mensaje inicial nene- Lrr #OEH #OFw Mensaj'e de error ' E F F ' #OFw #SOH IniToc/Dio Rutina que inicializa el controlador de Teclado/Display para operar en los siguientes modos en forma normal: - Frecuencia interna de tiempo de "scan" de teclado: í O O W z . - í 6 display's de caracteres a 8 bits. entrada pur l a izquierda. - Codigo de blanqueo en "todus ceros", limpia R A M display, FIFO s t a t u s . IniToclDie: MoVEA. L MOVE. B MOVE. e - MOVE. e MOVEA.L END #XbDicom,Ao #34n,C Ao3 #08n, C Ao3 #OD7n,íA d #OO,Ao Programa reloj* interno a 100 KHz. 16 d i s p l a y s , entrada izquierda Limpia display/Statzts/ Fin de IniTecjDis 146531 3. . . Resultados. E l d e s a r r o l l o ,de un ,sistema como el que hemos presentado, implica l a depuracion continua del software e s c r i t o , y hacer prueba y error de cada una de l a s partes para asegurarse que el softwaTe escrito haga funcionar el diseño del hardware; esto seria inmediato contando con l a s herramientas adecuadas para t a l f i n , lo que no sucede e l es$e caso. E s necesario contar con buenos ensambladores y mas aun, de un emulador para probar el software directamente sobre el hardware y n o hacer de un t r a b a j o interesante uno totalmente tedioso. 3.1. - Problemas enfrentados def i c i enci as. en la , implantacion, limitaciones y Como c a r a c t e r í s t i c a corn&, hubo que ajustar l a s señales d e acceso y sincronizacion de casi todos los c i r c u i t o s , ya que el diseño presentaba el iTplementar dichos ajustes cada vez que alguna rutina no funcionaba o alguna señal c o , ) CS o AS o IACK no se presentaba, debido a los tiempos c r i t i c o s de acceso de los dispositivos. La f a l t a de herramienta, l l e v ó a hacer m;ltiples pruebas del software y por tanto a d i f i c u l t a r mas el d e s a r r o l l o del sistema. Cabe señalar la importancia inclusive de un buen presupuesto para cualquier desarrollo, ya qye en algunos casos s e usaron partes ya Ysadas, lo que proyoco problemas de f a l s o s contactos, y el encontrarlos d i f i c : u l t o mas el trabajo. 4. . . Concl u s i ones. Como f i n a nuestra exposicion del t r a b a j o efectuado, podemos decir que l a vision de un sistema basad? en dispositivos i ntegr ados , el desar r o1 1o y 1a combi nací on de di fer entes dispositivos para 1,ograr un buen dis/eño, se obtienen con una perfecta documentacion y familiariazacion con cada uno de ellos; el aplicar ips conceptos de cursos anteriores sumados a una buena comprension del sistema y herramientas adecuadas, hacen del diseño del hardware y software de sistemas un buen objetivo a seguir. 5...Bibliografía. MC68000, Advance I n f or mati on The TTL Databook for desi g n Engi n e e r s Second E d i t i o n . C r o s s 16 U s e r s Manual P . O . B o x 384, B e d f o r d Nova Scottia Canada. The Motorola MC88000, Microprocessor Family, Assembly Language, I n t e r f a c e Design and System D e s i g n . School of S c i e n c e s and T e c h n o l o g i e s U n i v e r s i t y of Houston, C h a r l a k e P r e n t i c e - H a l l I n c . , New J e r s e y . TMS4500A Dynamic RAM c o n t r o l l e r User ’ s Manual , Memor y S u p p o r t , Component Data Cata1 og, 30