CPU

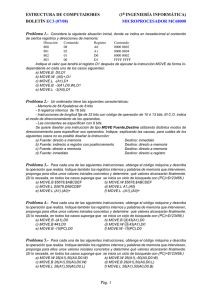

EJERCICIO 1

Indica el contenido de la memoria después de la ejecución de la siguiente porción

de código, teniendo en cuenta la situación inicial:

(1) MOVEA.L

(2) MOVE.W

(3) MOVE.L

(4) MOVE.B

#$000A02, A0

(A0)+, D2

$000A00, $000A02

0(A0, D2.W), $000A01

Situación inicial:

$000A00

$000A01

$000A02

$000A03

$000A04

$000A05

$000A06

$000A07

AF

34

00

02

56

12

00

3D

EJERCICIO 2

Sabemos que los registros A3 y A4 de un procesador 68000 tienen almacenados

los valores A3=$305 y A4=$400. Escribir una sola instrucción en lenguaje

ensamblador con la cual se mueva el byte contenido en la posición de memoria

$304 a la posición $408 sin utilizar el modo de direccionamiento directo a

memoria.

EJERCICIO 3

Determinar qué ciclos de memoria producirá la ejecución de la siguiente

instrucción del MC68000, y en qué orden:

ADD.L

(A0)+, 4(A0)

Siendo el valor inicial de A0=$00000400, y de la memoria:

$00030C

$00030E

$000400

$000402

$000404

$3456

$7890

$1234

$5678

$9012

$000406

$000408

$00040A

$00040C

$00040E

$3456

$7890

$1234

$5678

$9012

Determinar para cada ciclo el valor del bus de direcciones, del bus de datos y de la

línea de Lectura/Escritura.

1

EJERCICIO 4

Determinar el contenido de los octetos de memoria comprendidos entre las

direcciones $4000 y $4007, suponiendo que inicialmente todos ellos valen $55,

después de ejecutar las siguientes instrucciones:

(1) MOVE.L

(2) MOVE.W

(3) MOVE.L

(4) MOVE.B

(5) MOVE.B

#$33, $4002

#$4444, $4000

#$6666, $4004

#$11, $4002

#$22, $4001

EJERCICIO 5

Se dispone de un procesador con un bus de datos de 16 bits, capaz de direccionar

64 Mbytes de memoria y cuyas instrucciones tienen un tamaño de 64 bits. Indicar

cuántos accesos a memoria realiza este procesador y con qué propósito se

realizan al ejecutar las siguientes instrucciones:

(1) MOVE.L

(2) ADD.W

(3) JMP

#$A0000, $F0AA00

$00FF, $0200

$FFFF

Nota: La nomenclatura, la semántica y los modos de direccionamiento de estas

instrucciones son similares a las del MC68000.

EJERCICIO 6

Tenemos un procesador MC68000 trabajando con un reloj de 12.5 MHz. A dicha

frecuencia el procesador tarda en realizar un ciclo de bus (lectura o escritura) 320

ns. Suponiendo que el procesador ha tardado 960 ns en ejecutar la instrucción

MOVE.L (A7), D0. Indica cuál es el número de palabras que ocupa el código

máquina de la instrucción.

EJERCICIO 7

Considera el siguiente conjunto de instrucciones:

I1 : MOVE #10,D1

I2 : ADD D1,D2,D3

I3 : SUB D3,D2, D4

I4 : ADD D3,D5,D6

;

;

;

;

D1 := 10

D3 := D1 + D2

D4 := D3 - D2

D6 := D3 + D5

a) Indica las dependencias de datos existentes entre las instrucciones.

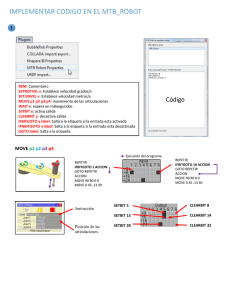

b) Vamos a considerar una segmentación (pipeline) de 5 etapas (F:

extracción, D: decodificación, O: obtención de operandos, E: ejecución, W:

escritura de resultado). Completa el siguiente gráfico de los ciclos

necesarios para ejecutar dicha secuencia de instrucciones, de forma que se

2

obtenga el resultado correcto. Para ello deberán indicarse los retardos

necesarios según las dependencias de datos existentes, manteniendo una

instrucción en la misma etapa del pipeline durante los ciclos que se

considere necesario. Debe suponerse que todas las etapas del pipeline

duran 1 ciclo y que no se utiliza anticipación (data forwarding).

Ciclo/Inst.

I1

1

F

2

D

3

O

4

E

5

W

→D1

6

7

8

9

10

11

12

13

I2

I3

I4

3

14

0

0