Sistemas Electrónicos Digitales Práctica 1 Multiplicador de 8 bits

Anuncio

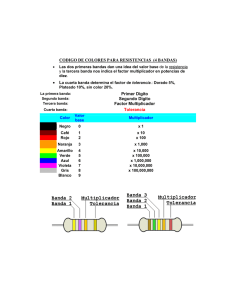

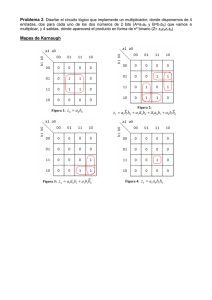

Sistemas Electrónicos Digitales Práctica 1 Multiplicador de 8 bits secuencial con desplazamiento hacia la derecha Javier Toledo Moreo Dpto. Electrónica, Tecnologı́a de Computadoras y Proyectos Universidad Politécnica de Cartagena 9 de abril de 2006 Descripción de la práctica El objetivo de la práctica es la implementación de un multiplicador secuencial basado en el algoritmo de desplazamiento hacia la derecha sobre una FPGA XC4010EPC84 de Xilinx, utilizando las herramientas del software Foundation. Las entradas a la FPGA son dos números enteros sin signo codificados con 8 bits cada uno de ellos, y la salida los 16 bits del resultado de la multiplicación. Los pasos a seguir en el desarrollo de la práctica son: Elaboración del esquemático del diseño Simulación funcional Realización de los procesos Map, Place y Route orientados a la FPGA elegida Análisis de la información contenida en los informes de implementación Simulación temporal Configuración de la FPGA en la placa XS40 y depuración del diseño. Algoritmo de multiplicación con desplazamiento a la derecha Tal y como se puede observar en el esquema de la Figura 1, la idea básica del algoritmo a implementar es calcular la suma acumulada de los sucesivos productos parciales. Un multiplexor realiza el producto parcial del multiplicando por un bit del multiplicador: la salida del multiplexor es el multiplicando si el bit del multiplicador vale ‘1’y 0 si tal bit vale ‘0’. Desplazando el multiplicador hacia la derecha y considerando en cada instante su bit menos significativo se realizan de manera sucesiva todos los productos parciales. Para acumular los 1 Diseño de un multiplicador de números de 8 bits productos parciales se emplea un sumador y un registro de desplazamiento, cuya salida constituye una de las entradas al sumador; la otra entrada al sumador es el producto parcial del multiplicando por cada bit del multiplicador, es decir, la salida del multiplexor. Para respetar el peso de los bits del multiplicador en el resultado, el registro de desplazamiento que contiene el resultado parcial debe desplazarse hacia la derecha cuando lo haga el multiplicador. Una vez realizadas las sumas y los desplazamientos para todos los bits del multiplicador, el registro del resultado contiene el producto de multiplicando y multiplicador. Multiplicando Cero Q D Multiplicador D Q Registro de datos LSB Multiplexor Registro desplazamiento hacia la derecha + Sumador Resultado D Q Registro desplazamiento hacia la derecha Figura 1: Estructura del multiplicador. Las Figuras 2, 3, 4, 5 y 6 muestran la evolución de los valores de los registros para la multiplicación de 6 (multiplicando) por 11 (multiplicador), codificados con 4 bits. Funcionamiento del diseño Inicialmente, todos los biestables tienen el valor por defecto 0, por lo que el primer paso debe ser cargar multiplicador y multiplicando con los valores deseados. Éstos son dos entradas a la FPGA, cada una de ellas un dato de 8 bits. A continuación debe empezar el algoritmo de multiplicación, realizándose los pasos comentados en el apartado anterior. Una vez ha terminado el proceso de multiplicación, el valor correspondiente está presente en el registro resultado. Éste no debe modificarse, permaneciendo constante hasta que se active una señal de reset, también entrada a la FPGA. Cuando esta señal vuelva al valor ‘0’ después de valer ‘1’, debe comenzar una nueva operación de multiplicación, para lo cual tanto los registros multiplicador y multiplicando como el registro resultado deben tomar el valor 0. 2 Diseño de un multiplicador de números de 8 bits Multiplicando Cero Q D Multiplicador 0110 D Q LSB 1 0110 1011 + Resultado D Q 0000 0000 Figura 2: Estado inicial. Multiplicando y multiplicador con sus respectivos valores, y resultado a 0. Multiplicando Multiplicando Cero Q Cero D Q Multiplicador Multiplicador 0110 0110 D D Q LSB 1011 D Q LSB 1 0110 0101 1 0110 + + Resultado D Resultado Q D 0110 0000 Q 0011 0000 Paso 1 Paso 2 Figura 3: Paso 1: Actualización registro Resultado con la salida del sumador. Paso 2: Desplazamiento hacia la derecha de Resultado y de Multiplicador. 3 Diseño de un multiplicador de números de 8 bits Multiplicando Cero Q Multiplicando D Cero Multiplicador 0110 Q LSB D Q LSB 1 0 0110 0101 D Multiplicador 0110 D Q 0000 0010 + + Resultado D Resultado Q D 1001 0000 Q 0100 1000 Paso 3 Paso 4 Figura 4: Paso 3: Actualización registro Resultado con la salida del sumador. Paso 4: Desplazamiento hacia la derecha de Resultado y de Multiplicador. Multiplicando Multiplicando Cero Q Cero D 0110 0110 D Q LSB 0010 D Multiplicador Multiplicador D Q Q LSB 0 0000 0001 1 0110 + + Resultado Resultado D D Q Q 0010 0100 0100 1000 Paso 5 Paso 6 Figura 5: Paso 5: Actualización registro Resultado con la salida del sumador. Paso 6: Desplazamiento hacia la derecha de Resultado y de Multiplicador. 4 Diseño de un multiplicador de números de 8 bits Multiplicando Multiplicando Cero Q Cero D 0110 0110 D Q LSB 0001 D Multiplicador Multiplicador D Q Q LSB 1 0110 0000 0 0000 + + Resultado Resultado D D Q Q 0100 0010 1000 0100 Paso 7 Paso 8 Figura 6: Paso 7: Actualización registro Resultado con la salida del sumador. Paso 8: Desplazamiento hacia la derecha de Resultado y de Multiplicador. Consideraciones de diseño Para la realización del diseño deben tenerse en cuenta las siguientes consideraciones: La señal de reloj debe ser la misma para todo el circuito, y el flanco de reloj activo es el de subida. El reset puede ser sı́ncrono a ası́ncrono. Una vez terminado el proceso de multiplicación, el valor del registro resultado debe permanecer constante hasta que se active el reset, independientemente del número de ciclos de reloj que tengan lugar después de completado el proceso. Deben diseñarse los componentes del circuito con el tamaño adecuado para realizar la funcionalidad deseada. Bibliografı́a J.F. Wakerly, “Digital design: principles and practices”, 3a ed. actualizada, Prentice Hall. 2001. B. Parhami, “Computer arithmetic. Algorithms and hardware designs”, Oxford University Press. 2000. 5