Organización y Arquitectura - Universidad de Buenos Aires

Anuncio

Organización y Arquitectura

Diego Garverbetsky1 , Marcelo Risk1 ,

Diego Fernández Slezak1 , Juan Pablo Galeotti1 ,

Fernando Schapachnik1

1 Departamento de Computación, FCEyN,

Universidad de Buenos Aires, Buenos Aires, Argentina

Organización del Computador I,

verano de 2013

Varios y Schapachnik

Organización y Arquitectura

(2) Niveles de abstracción de una computadora

Varios y Schapachnik

Organización y Arquitectura

(3) Organización de una computadora moderna

Unidad Central de Procesamiento (CPU)

Registros

Unidad Aritmético-Lógica (ALU)

Interconexión interna de la CPU

Unidad de Control

Lógica secuencial

Unidad de control de registros y decodificadores

Memoria de control

Memoria principal

Subsistema de Interconexión (Bus)

Subsistema de Entrada/Salida (I/O)

Varios y Schapachnik

Organización y Arquitectura

(4) Von Neumann

Esto es lo que se conoce como el Modelo...

...Von Neumann (/Fon Noiman/)

Varios y Schapachnik

Organización y Arquitectura

(5) Organización del Modelo Von Neumann

Varios y Schapachnik

Organización y Arquitectura

(6) Microarquitectura del Modelo Von Neumann

Varios y Schapachnik

Organización y Arquitectura

(7) Ciclo de instrucción

FETCH 1) UC obtiene la próxima instrucción de memoria (usando el registro

PC).

2) Se incrementa el PC.

DECODE 3) La UC decodifica la instrucción.

EXECUTE 4) La UC ejecuta la instrucción (puede usar o no la ALU).

5) Vuelve al paso 1.

Varios y Schapachnik

Organización y Arquitectura

(8) Listo

Con esto ya puedo construir una computadora.

?

¿Sólo una?

De alguna manera tengo cierta idea del flujo de información,

pero falta saber algunas cosas.

Es decir, conozco la organización, pero no aún la arquitectura.

Varios y Schapachnik

Organización y Arquitectura

(9) Arquitectura de una computadora

¿Qué tipos de datos puede manejar “nativamente”?

¿Cómo se almacenan?

¿Cómo se acceden?

¿Qué operaciones (instrucciones) puede ejecutar?

¿Cómo se codifican estas operaciones?

Un conjunto de respuestas a estas preguntas se llama

Instruction Set Architectura.

También conocida como ISA.

Cuando estamos estudiando una ISA, la organización se vuelve

un detalle que sólo interesa para endenter el comportamiento.

Varios y Schapachnik

Organización y Arquitectura

(10) Métricas de una ISA

Cantidad total de instrucciones disponibles (“largo”).

Complejidad del conjunto de instrucciones:

RISC: Reduced Instruction Set Computer

CISC: Complex Instruction Set Computer

Longitud de las instrucciones (“ancho”).

Cantidad de memoria que un programa requiere (“largo x

ancho”).

Varios y Schapachnik

Organización y Arquitectura

(11) ¿Qué tipos de datos soporta?

Tipos de datos

Enteros (8, 16, 32 bis; complemento a 2)

Punto flotante

Punto fijo

¿BCD, ASCII?

Almacenamiento

Big Endian

Little Endian

Varios y Schapachnik

Organización y Arquitectura

(12) Little Endian vs Big Endian

Endianness se refiere a la forma en que la computadora

guarda datos multibyte.

Little endian: el byte en una posición de memoria menor, es

menos significativo. En general, Intel y computadoras CISC.

Big endian: el byte en una posición de memoria menor, es el

más significativo. En general, Motorola, computadoras RISC y

redes.

Ejemplo para 0x1234

Little endian: M[0] = 0x34 M[1] = 0x12

Big endian: M[0] = 0x12 M[1] = 0x34

Ejemplo para 0x12345678

Little endian:

M[0] = 0x78 M[1] = 0x56 M[2] = 0x34 M[3] = 0x12

Big endian:

M[0] = 0x12 M[1] = 0x34 M[2] = 0x56 M[3] = 0x78

Varios y Schapachnik

Organización y Arquitectura

(13) Endianness

Fuente: “Los viajes de Gúliver”, de Jonathan Swift

Leerlo para aprender

Sobre Lı́liput.

Qué es un Yahoo!

“Una modesta proposición: Para prevenir que los niños de los

pobres de Irlanda sean una carga para sus padres o el paı́s, y

para hacerlos útiles al público”.

Varios y Schapachnik

Organización y Arquitectura

(14) Acceso a los datos

¿Dónde se almacenan los datos?

Registros

Memoria

Stack

Espacio de E/S

¿Cómo se acceden a los datos?

Modos de direccionamiento válidos de las instrucciones.

Directo (memoria), indirecto (puntero en memoria), indexado

a registro.

Varios y Schapachnik

Organización y Arquitectura

(15) Operaciones

¿Qué operaciones (instrucciones) puede ejecutar?

Movimiento de datos (eg, Move, Load, Store, ...).

Aritméticas (eg, ADD, SUB, ...).

Lógicas (eg, AND, XOR, ....).

E/S (eg, IN, OUT).

Transferencia de control (eg, Jump, Call, Ret).

Especı́ficas (eg, MMX).

Varios y Schapachnik

Organización y Arquitectura

(16) ¿Cómo se codifican las operaciones?

CódOp

|

Fuente/s

Destino/s

{z

Ref. próx instr

Longitud de la instrucción

}

CódOp: Representa la operación a realizar.

Fuente/s: Provee información sufiente para obtener operandos

de origen.

Destino/s: Provee información sufiente para obtener la

ubicación del resultado de la operación

Ref. próx instr: Provee información suficiente para determinar

el próximo PC.

Varios y Schapachnik

Organización y Arquitectura

(17) Arquitectura ejemplo: MARIE

Representación binaria, complemento a 2.

Memoria de 4K direcciones.

Cada dirección contiene 16 bits de datos.

Direcciones de memoria de 12 bits (212 =4K).

Máquina de Acumulador:

Registro Acumulador (AC) de 16 bits.

Es el operando implı́cito en casi todas las operaciones.

Varios y Schapachnik

Organización y Arquitectura

(18) MARIE: instrucciones

Instrucción

JnS X

Load X

Store X

Add X

Subt X

Input

Output

Halt

Skip COND

Jump X

Clear

Addi X

Jumpi X

Comportamiento

Almacena PC en X y salta a X+1

AC = [X]

[X]= AC

AC = AC + [X]

AC = AC - [X]

AC = Entrada de periférico

Enviar a un periférico contenido AC

Detiene la ejecución

Saltea una instrucción si se cumple

Si COND=00 → AC<0

Si COND=01 → AC=0

Si COND=10 → AC>0

PC = X

AC = 0

AC = AC + [ [ X ] ]

PC = [X] Organización y Arquitectura

Varios y Schapachnik

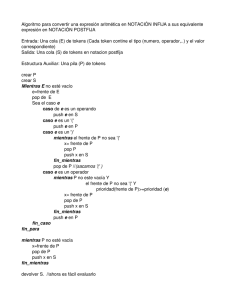

(19) MARIE: Formato de instrucción

Formato de instrucción fijo:

15

12 11

OpCode

Varios y Schapachnik

0

Dirección

Organización y Arquitectura

(20) MARIE: Codificación instrucciones

OpCode

0000

0001

0010

0011

0100

0101

0110

0111

1000

Instrucción

JnS X

Load X

Store X

Add X

Subt X

Input

Output

Halt

Skip COND

1001

1010

1011

1100

Jump X

Clear

Addi X

Jumpi X

Comportamiento

Almacena PC en X y salta a X+1

AC = [X]

[X]= AC

AC = AC + [X]

AC = AC - [X]

AC = Entrada de periférico

Enviar a un periférico contenido AC

Detiene la ejecución

Salta una instrucción si se cumple la condición

(00 → AC<0; 01 → AC=0; 10 → AC>0)

PC = X

AC = 0

AC = AC + [ [ X ] ]

PC = [X]

Varios y Schapachnik

Organización y Arquitectura

(21) MARIE: Ejemplo en ensamblador

Tarea:

Sumar el contenido de 0xFF0 y 0xFF1.

Almacenar el resultado en 0xFF2.

Load 0xFF0

Add 0xFF1

Store 0xFF2

# AC=[0xFF0]

# AC=[0xFF0]+[0xFF1]

# [0xFF2]=[0xFF0]+[0xFF1]

Varios y Schapachnik

Organización y Arquitectura

(22) MARIE: Ejemplo ya ensamblado

0001 1111 1111 0000

0011 1111 1111 0001

0010 1111 1111 0010

# Load 0xFF0

# Add 0xFF1

# Store 0xFF2

Varios y Schapachnik

Organización y Arquitectura

(23) Estructuras de control

Las instrucciones que vimos hasta ahora son las equivalentes a

las asignaciones.

¿Cómo alteramos el flujo de control de un programa?

Ie, ¿cómo implementamos los IF, WHILE, llamadas a

procedimientos?

En ensamblador tenemos las instrucciones de control:

Saltos condicionales (debe cumplirse alguna condición).

Saltos incondicionales (se cambia el flujo siempre que se

ejecuta la instrucción).

Varios y Schapachnik

Organización y Arquitectura

(24) Ejemplo de estructuras de control

¿Cómo podemos escribir este programa con instrucciones de

MARIE?

If (AC!=0)

AC=0

EndIf

Varios y Schapachnik

SkipCond 01

Clear

Organización y Arquitectura

(25) La pila

Varios y Schapachnik

Organización y Arquitectura

(26) La pila

Es una estructura de datos.

Puedo solamente:

Agregar un dato al tope de la pila (PUSH).

Retirar el dato que está al tope de la pila (POP).

Se implementa en memoria.

Varios y Schapachnik

Organización y Arquitectura

(27) Arquitecturas basadas en pila

Se implementa con un registro que apunta solamente al tope

de la pila.

Las stack machines

Pueblan y despueblan la pila usando:

PUSH operando

POP operando

Las operaciones aritmético/lógicas

obtienen los operandos de la pila y

almacenan los resultados allı́.

Varios y Schapachnik

Organización y Arquitectura

(28) Ejemplo: StackMARIE

Tiene la arquitectura de

OpCode Instrucción

0000

PUSH X

0001

POP X

0010

ADD

0011

SUB

0100

AND

0101

OR

0110

NOT

0111

LE

1000

GE

1001

EQ

1010

JUMP X

1011

JumpT X

1100

JumpF X

MARIE pero orientada a pila.

Comportamiento

push([x])

[x]=pop()

push(pop()+pop())

push(pop()-pop())

push(pop() & pop())

push(pop() | pop())

push ( pop())

push(pop()<=pop())

push(pop()>=pop())

push(pop()==pop())

PC=X

Si pop()==T entonces PC=X

Si pop()==F entonces PC=X

Varios y Schapachnik

Organización y Arquitectura

(29) Arquitecturas GPR

GPR: General Purpose Register.

Arquitecturas de registros de propósito general.

Podemos utilizar varios registros.

Caso tı́pico: arquitecturas RISC.

...y la mayor parte de las arquitecturas actuales.

Varios y Schapachnik

Organización y Arquitectura

(30) Arquitectura de la Máquina Orga1

Memoria:

Direcciones de 16 bits (de 0x0000 a 0xFFFF).

Palabras de 16 bits.

Direccionamiento a palabra (65535 palabras).

Registros

8 registros de propósito general de 16 bits (R0 a R7).

3 registros de propósito especı́fico de 16 bits:

PC (Program Counter)

IR (Instruction Register)

SP (Stack Pointer)

4 flags: Z, N, C y V

Varios y Schapachnik

Organización y Arquitectura

(31) Flags

Son registros de 1 bit que nos dan información de control.

En la arquitectura Orga1:

(Z)ero

(N)egative

(C)arry

o(V)erflow

Se modifican con todas las operaciones aritmético-lógicas

(ie, todas salvo MOV, CALL, RET, JMP y Jxx).

Varios y Schapachnik

Organización y Arquitectura

(32) Flags: Ejemplo

ADD R0, R1

# R0 := R0+R1 (suma bit a bit)

Z==1 ssi el resultado es 0x0000.

N==1 ssi el resultado es negativo complemento a 2 de 16 bits.

C==1 ssi la suma bit a bit produjo acarreo.

V==1 ssi el resultado no es representable en complemento a

2 de 16 bits.

NEG + NEG = POS

POS + POS = NEG

Varios y Schapachnik

Organización y Arquitectura

(33) Flags y control de flujo

Los flags

Salto

JE

JNE

JLE

JG

JL

JGE

JLEU

JGU

JCS

JNEG

JVS

se utilizan para realizar saltos condicionales.

Descripción

Condición

Igual / Cero

Z

Distinto

Not Z

Menor o igual

Z or ( N xor V)

Mayor

Not (Z or ( N xor V ) )

Menor

N xor V

Mayor o igual

Not ( N xor V )

Menor o igual sin signo C or Z

Mayor sin signo

Not ( C or Z )

Carry / Menor sin signo C

Negativo

N

Overflow

V

Varios y Schapachnik

Organización y Arquitectura

(34) Flags: Preguntas

¿Por qué usar flags y no preguntar por el valor de los registros

o la memoria?

¿Por qué hay un “Menor” y un “Menor sin signo”?

Varios y Schapachnik

Organización y Arquitectura

(35) Subrutinas

Son alteraciones del flujo secuencial que permiten “retornar” al

lugar desde donde fueron invocadas.

CALL dir_subrutina # PC = dir_subrutina

Problema: ¿cómo guardamos la dirección de retorno?

a) En registros.

b) En una dirección de memoria (ejemplo: al inicio de la rutina).

c) Ninguna de las anteriores...

El que dijo...

a) Si la subrutina usa los registros perdemos el valor de retorno.

¿Cómo manejamos la recursión?

b) ¿Cómo soportamos recursión/varios llamados a la misma

subrutina?

c) ¡La pila!

Varios y Schapachnik

Organización y Arquitectura

(36) Subrutinas en la pila

CALL dir subrutina

Sirve para comenzar a ejecutar una subrutina.

La CPU hace push(PC), y luego PC:=dir subrutina

RET

Sirve para terminar de ejecutar una subrutina.

La CPU hace PC:=pop()

Adicionalmente, con PUSH/POP podrı́amos almacenar los

argumentos y el retorno de la subrutina (se ve en Orga2).

Varios y Schapachnik

Organización y Arquitectura

(37) Tarea

Sean A, B, C y D direcciones de memoria.

Escribir un programa que realice D:=(A-B)+C en

MARIE (acumulador)

StackMARIE (pila)

Orga1 (GPR)

Varios y Schapachnik

Organización y Arquitectura

(38) Bibliografı́a

Capı́tulos 4 y 5 del Null.

Van a servir para más temas...

Ie, léanlos de verdad.

Varios y Schapachnik

Organización y Arquitectura