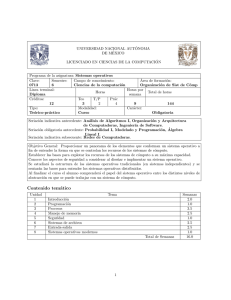

Programa y bibliografía

Anuncio

ESTRUCTURA DE COMPUTADORES II II, ITIS - Curso 2008-2009 Dpto. de Electrónica y Sistemas. Facultad de Informática. A Coruña Profesores de teorı́a: Diego Andrade Canosa y Emilio J. Padrón González PROGRAMA PARTE I: Jerarquı́a de Memoria 1. Conceptos básicos 2. Memoria Caché 2.1 Principios de funcionamiento. 2.2 Rendimiento y técnicas de mejora 3. Memoria Principal 3.1 Organización. 3.2 Tecnologı́as de memoria RAM. 3.3 Entrelazamiento. 4. Memoria Virtual 4.1 Sistemas paginados. 4.2 Sistemas segmentados. 4.3 Sistemas segmentados con paginación. PARTE II: Interfaz entre Procesadores y Periféricos 1. Organización de Entrada/Salida 1.1 Medidas de Rendimiento 1.2 Módulos de E/S. 1.3 E/S programada. 1.4 E/S mediante interrupciones. 1.5 Acceso directo a memoria (DMA). 1.6 Canales y procesadores de E/S. 2. Interconexión con buses. 2.1 Elementos de diseño de un bus 2.2 Circuitos de interfaz 2.3 Ejemplos de buses estándares: 3. Periféricos 3.1 Dispositivos de entrada 3.2 Dispositivos de salida 3.3 Discos magnéticos Prácticas 1. Técnicas de optimización software del rendimiento caché 2. Programación en ensamblador de E/S Bibliografı́a Básica Organización y Arquitectura de Computadores. W. Stallings. 7a edición. Pearson - Prentice Hall, 2006. Computer Architecture. A Quantitative Approach. H. L. Hennessy and D. A. Patterson, 3a edición, Morgan Kaufmann Publishers, 2003. Computer Organization and Design : the hardware/software interface . D. A. Patterson y J. L. Hennessy. Morgan Kaufmann Publishers, 2005. Bibliografı́a Complementaria Estructura y diseño de computadores: interficie circuiterı́a/programación. D. A. Patterson y J. L. Hennessy. Editorial Reverté, 2000. Organización de computadores. C. Hamacher, Z. Vranesic y S. Zaky. Mc Graw Hill, 2003. Evaluación La evaluación consiste en un examen en que la parte teórica tiene un peso de ocho puntos y la parte práctica dos puntos.