TRABAJO 1

Anuncio

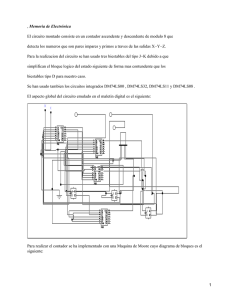

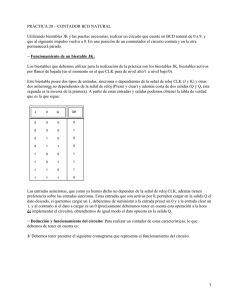

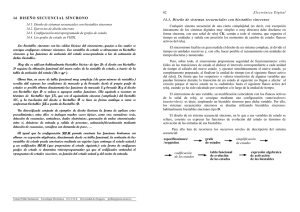

TRABAJO Nº4 SISTEMAS DIGITALES / TECNOLOGÍA DE COMPUTADORES 1. Diseñe un autómata de Mealy con dos entradas (X1 y X2) y una salida Z, que obedezca al siguiente comportamiento: • En ningún caso ambas entradas pueden estar a 1 simultáneamente. • La salida Z alcanzará el valor 1 si y sólo si aparecen dos unos consecutivos en la misma línea de entrada, pasando a dicho valor cuando se detecte el segundo 1. Hay solapamiento. 2. Sobre una única línea X se envía una información sincronizada con una señal de reloj Ck. Se ha convenido que la información sea correcta siempre que no haya dos o más unos consecutivos o cuatro o más ceros consecutivos. Obtenga el diagrama de estados de un circuito cuya salida sea uno si se detecta un error en la transmisión y que permanezca en ese valor en tanto dure el error. 3. Diseñe a partir de biestables tipo T, un circuito secuencial síncrono cuyo diagrama de estados sea el de la figura. Realice todos los pasos para la síntesis, excepto el dibujo del circuito. Estado Q2 Q1 A B 0 0 0 1 C 1 0 D 1 1 4. Diseñe un contador asíncrono que evolucione según la siguiente secuencia de cuenta: 3, 7, 9, 11, 14 Æ 3, 7… 5. Utilizando biestables D síncronos por flanco de bajada, diseñe un contador síncrono módulo 8 ascendente/descendente en código gray. 6. Utilizando biestables JK activos por flanco de bajada y con entrada asíncrona CLR activa a nivel bajo, y puertas NAND de dos entradas, diseñar un contador síncrono que posea una entrada de control “X” y cumpla las siguientes condiciones : • Si X=0, el contador funcionará de modo ascendente con la siguiente secuencia de conteo 0→2→4→6→1→3→5→7→[0→.... • Si X=1, el contador funcionará de modo descendente, siendo la secuencia de conteo 0→7→5→3→1→6→4→2→[0→.... 7. Implementar un contador asíncrono que evolucione según la siguiente secuencia : 0 , 1 , 2 , 3 , 2 , 3 , 0 , 1 , 4 , 5 , 6 , 7 , 6 , 7 , 4 , 5 , Æ 0, 1 ,...... Se dispone para ello de biestables JK con sincronismo por flanco de bajada (sin entradas asíncronas) y del menor número posible de puertas lógicas. NOTA: aunque la salida toma únicamente los valores de 0 a 7, el número de estados de este contador es mayor de ocho. 8. Diseñar un contador BCD Natural de módulo 56 , utilizando el c.i. 7490 y las puertas AND de dos entradas necesarias. 9. Diseñar un registro de desplazamiento a derechas, de cuatro bits, que reúna las siguientes condiciones: - Entrada de datos serie (E), controlada mediante una señal de validación (A=1). Entrada de datos paralelo (P0, P1, P2, P3), controlada mediante una señal de validación (A=0). La carga de datos se ha de hacer sincronizada con los pulsos de reloj. Salida de datos serie y paralelo. Implementar el circuito mediante biestables D activos por flanco de subida y con entradas asíncronas (P, C) activas a nivel alto, y los operadores lógicos necesarios. 10. Completar el siguiente cronograma para las lógicas de disparo, sincronismos y niveles iniciales indicados Reloj DKR J S T Q JKm/s,cd ↑ Q JK m/s ↓ Q RSnor Q’ Q D m/s ↓ Q T↓ Q RS m/s ↓ Q D↓ Nota: m/s indica sincronismo maestro esclavo cd cierre de datos ↓↑ Sincronismo por flanco de bajada o subida respectivamente. Nivel alto