7. Análisis y diseño con registros

Anuncio

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:43

Página 182

Análisis y diseño

con registros

En esta unidad aprenderás a:

●

Analizar los registros de

almacenamiento, también

llamados latches.

●

Conocer el circuito integrado 7475.

●

Analizar los registros de

desplazamiento, también llamados

shifters.

●

Conocer los circuitos integrados 7491

y 7494 que contienen registros de

desplazamiento de entrada

serie/salida serie y entrada

paralelo/salida serie,

respectivamente.

●

Conocer el circuito integrado

7495 que contiene un registro

de desplazamiento de

entrada paralelo/salida

paralelo.

07

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:44

Página 183

7. Análisis y diseño con registros

Introducción

Introducción

Al igual que los contadores, los registros están implementados con biestables. En esta unidad analizaremos

los registros realizados con biestables comerciales

como elemento básico para la realización de esta función, así como algunos de los registros comerciales

integrados en la escala media de integración (MSI)

dentro de la familia de tecnología TTL.

Los registros son bloques funcionales destinados a

almacenar o registrar información binaria durante un

cierto tiempo, generalmente, dentro de un proceso

global de tratamiento de dicha información. Así

como un biestable puede almacenar un bit, un conjunto de n biestables constituyen un registro de n

bits. Un registro es, por tanto, un circuito de memoria temporal, capaz de almacenar un único dato de

n bits, siendo n el número de biestables que utiliza

el registro.

Los registros, en función de su capacidad o incapacidad para realizar internamente el desplazamiento de

la información almacenada en ellos, se clasifican en:

bits de un biestable a otro, se generan los registros

de desplazamiento.

Un registro de desplazamiento consta esencialmente de una cadena de biestables conectados en

cascada, siendo la salida de uno la entrada del

siguiente. Para convertir el circuito en síncrono, se

conecta una señal de reloj a todos los biestables para

que éstos transfieran al mismo tiempo su contenido.

Se puede utilizar para la implementación de estos

registros cualquiera de los biestables que se han

estudiado en la Unidad 5, pero normalmente se utilizarán biestables del tipo J-K, R-S y D, que pueden

disponer de entradas asíncronas de Preset y/o Clear.

Por tanto, podemos encontrar registros que por la

forma de recibir y de transmitir la información pueden pertenecer a uno de los tipos mostrados en el

siguiente cuadro:

Tipos

de

registros

• Registros de almacenamiento (latch registers).

• Registros de desplazamiento (shift registers).

Los registros de almacenamiento están formados por

un conjunto de biestables (normalmente tipo D) aislados entre sí, con una señal de reloj común a todos

ellos, de forma que en todos se cargan simultáneamente los datos presentes en sus entradas, siendo

accesibles en cada momento sus entradas y salidas.

Si los registros de almacenamiento se activan por

nivel, también reciben el nombre de latch (cerrojo).

Las formas en que se hace llegar la información al

registro, y de extraerla posteriormente del mismo,

dan lugar a distintos tipos de registros.

Los datos pueden ser transferidos al registro en

forma serie o paralelo. De la misma manera, podemos transferir la información de un registro al exterior. En el formato serie se dispondrá de una sola

línea y los bits irán apareciendo uno tras otro, normalmente sincronizados con una señal de reloj. En

el segundo caso habrá tantos conductores como bits

tenga la señal binaria a registrar (bus de conductores). Cuando, además de la función de memoria, se

requiere dentro de un registro el poder desplazar

{

Registros de

almacenamiento

Registros de

desplazamiento

{

Por flanco

Por latch

{

Entrada

Entrada

Entrada

Entrada

serie/salida serie

paralelo/salida serie

paralelo/salida paralelo

serie/salida paralelo

Tipos de registros por la forma de recibir y transmitir

la información.

Una forma de representar la información que contienen los registros es la que se muestra en la Figura 7.1,

en la que se representa la información de cada biestable que compone el registro por un cuadro, de forma

que todos los cuadros unidos forman una tabla de n

bits con la información que contiene el registro.

En la Figura 7.1 se representa un registro de 8 bits,

donde cada biestable se ha numerado de 0 a 7, para

indicar su peso de menor a mayor valor. La forma en

que fluyen los datos, es decir, si éstos entran y

salen, se esquematiza mediante el empleo de flechas

que indican el sentido de movimiento de datos.

0

1

0

1

1

0

1

1

7

6

5

4

3

2

1

0

Figura 7.1. Representación del contenido de un registro

de 8 bits.

183

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:44

Página 184

7. Análisis y diseño con registros

7.1 Análisis de registros de almacenamiento

Así, por ejemplo, si se trata de un registro de entrada serie/salida serie, la representación es la que se

muestra en la Figura 7.2, en la que podemos interpretar fácilmente el sentido en el que fluyen los datos

de información del registro (de izquierda a derecha),

ya que entran por la izquierda y se desplazan y salen

hacia la derecha.

Entrada

0

1

0

1

1

0

1

1

7

6

5

4

3

2

1

0

Salida

Figura 7.2. Representación de un registro entrada

serie/salida serie.

7.1 Análisis de registros de almacenamiento

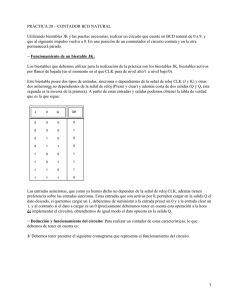

Actividades propuestas

1

• Con dos circuitos integrados TTL del tipo 7474,

monta un registro de almacenamiento de 4 bits

como el que se muestra en la Figura 7.3.

• Conecta las salidas de los biestables QA, QB, QC y QD

a los diodos LED del equipo didáctico para visualizar y medir los valores que toman en cada

momento las salidas del circuito.

• Alimenta el circuito y mide el valor que toman en

ese instante las salidas, anotando los resultados en

la Tabla 7.1.

• Utilizando los conmutadores lógicos del equipo

didáctico de electrónica digital sobre el que se está

montando el circuito, introduce por las entradas A,

B, C y D los datos 1, 0, 1, 0, respectivamente.

• Mediante el empleo del pulsador con circuito antirrebotes, genera un flanco de subida por la entrada

de reloj y posteriormente uno de bajada. Mide los

valores que toman las salidas y anota los resultados en la Tabla 7.1.

Actuación

A

B

C

D

Alimentación

↓

CLK

CLK ↓

Clear

↓

CLK

CLK ↓

Clear

1

1

1

1

1

1

0

0

0

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

Tabla 7.1. Resultados de la Actividad 1.

184

• Activa el pulsador de Clear durante un instante.

Mide y anota el valor que toman las salidas de los

biestables en la Tabla 7.1.

• Introduce ahora los datos 1, 1, 0, 0 por la entrada

de los biestables A, B, C y D. Genera un flanco de

subida por la señal de reloj y uno de bajada, posteriormente. Mide el valor que toman las salidas de

circuito y anota el resultado en la Tabla 7.1.

• Activa nuevamente la entrada de Clear.

• Completa el cronograma de la Figura 7.4.

• Contesta a las siguientes preguntas:

Registros de almacenamiento. Latch.

QA

QB

QC

QD

a) ¿Cuál es el modo de sincronismo del registro de

la Figura 7.3?

b) ¿Cuál es la capacidad de almacenamiento del

registro?

c) ¿Qué tipo de registro es?

d) ¿En qué momento se transfiere la información

al registro?

2

Registros de almacenamiento. Latch integrado.

En la Figura 7.5 se muestra el diagrama de conexión del

latch de 4 bits 7475 fabricado en tecnología TTL.

• Conecta las salidas de los biestables 1Q, 2Q, 3Q

y 4Q a los diodos LED del equipo didáctico, para

visualizar y medir los valores que toman en cada

momento las salidas del circuito.

• Emplea los conmutadores lógicos del equipo didáctico para introducir, por las entradas 1D, 2D, 3D y

4D, los valores 1, 0, 1, 0, respectivamente.

(continúa)

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:44

Página 185

7. Análisis y diseño con registros

7.1 Análisis de registros de almacenamiento

Actividades propuestas (continuación)

Salidas de datos

Entradas de datos

QA

QB

QC

QD

VCC

A

B

4

2

CLK

3

PR

D

IC1A

Q

5

10

12

11

CLK

CL

1

C

Q

PR

D

IC1B

Q

9

2

3

CL

13

Q

IC2A

4

CLK

6

7474

D

PR

D

12

11

CLK

8

CL

7474

Q

5

10

1

Q

PR

D

Q

9

R1

10 kΩ

CLK

6

7474

IC2B

CL

13

Q

8

7474

+ C1

1 μF

S

Clear

Figura 7.3. Registro de almacenamiento con biestables D.

• Utiliza el pulsador con circuito antirrebotes para

generar un flanco de subida por las entradas de reloj

1C, 2C (pin 13) y después uno de bajada. Genera,

A

B

C

D

Clear

CLK

QA

QB

QC

QD

t

t

t

t

t

t

t

t

t

t

Figura 7.4. Cronograma de funcionamiento del circuito de la

Figura 7.3.

seguidamente, un flanco de subida por las entradas

de reloj 3C, 4C (pin 4) y uno de bajada. Mide los

valores que toman las salidas y anota los resultados

en la Tabla 7.2.

• Pon a nivel alto las entradas 1C, 2C (pin 13) y 3C,

4C (pin 3). Cambia ahora los datos de las entradas

1D, 2D, 3D y 4D por 1, 1, 1, 1, respectivamente. A

continuación, pon a nivel bajo las entradas de

reloj y vuelve a cambiar los datos de entrada por

0, 0, 1, 1. Mide los valores que toman las salidas y

anota los resultados en la Tabla 7.2.

• Une las patillas 4 y 13, correspondientes a las entradas de reloj, que ahora serán una sola. Introduce por

la entrada de los biestables 1D, 2D, 3D y 4D los

datos 1, 1, 0, 0. Genera un flanco de subida por la

señal de reloj y después uno de bajada. Mide el valor

que toman las salidas de circuito y anota el resultado en la Tabla 7.2.

• Pon a nivel alto las entradas de reloj y cambia

ahora los datos de entrada 1D, 2D, 3D y 4D por 0,

1, 0, 1, respectivamente. Después, pon a nivel

(continúa)

185

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:44

Página 186

7. Análisis y diseño con registros

7.1 Análisis de registros de almacenamiento

Actividades propuestas (continuación)

Actuación

↓

1C - 2C

1C - 2C ↓

↓

3C - 4C

3C - 4C ↓

1C, 2C y 3C, 4C a nivel alto

1C, 2C y 3C, 4C ↓

a nivel alto

1C, 2C y 3C, 4C

1C, 2C y 3C, 4C ↓

1C, 2C y 3C, 4C a nivel alto

1C, 2C y 3C, 4C a nivel alto

1D

2D

3D

4D

1

1

1

1

1

0

1

1

0

1

0

0

0

0

1

0

1

1

1

0

1

1

1

1

1

1

0

0

0

1

0

0

0

0

1

1

0

0

1

0

1Q

2Q

3Q

4Q

Tabla 7.2. Resultados de la Actividad 2.

bajo las entradas de reloj y vuelve a cambiar los

datos de entrada por 1, 0, 1, 0. Mide los valores

que toman las salidas y anota los resultados en la

Tabla 7.2.

1Q

1Q

16

16

2Q

2Q

15

15

ENABLE

ENABLE

2Q

1C-2C GND

2Q 1C-2C

GND 3Q

3Q

14

13

12

11

14

13

12

11

3Q

3Q

10

10

4Q

4Q

9

9

1D

2D

Q

Q

D

D

D

D

G

G

G

G

Q

Q

Q

Q

Q

Q

Q

Q

D

D

D

D

G

G

G

G

Q

Q

Q

Q

3D

4D

Q

Q

CLK

1Q

1

1

1Q

1Q

2

2

1D

1D

3

4

5

3

4

5

ENABLE

2D

Vcc

2D ENABLE Vcc

3C-4C

3C-4C

6

6

3D

3D

7

7

4D

4D

8

8

4Q

4Q

SN5475

SN5475 (J,

(J, W)

W)

SN54L75

SN54L75 (J)

(J)

SN7475

SN7475 (J,

(J, N)

N)

SN74L75

SN74L75 (J,

(J, N)

N)

SN54LS75

SN54LS75 (J,

(J, W)

W)

SN74LS75

SN74LS75 (J,

(J, N)

N)

Figura 7.5. Diagrama de conexión del circuito 7475.

186

• Completa el cronograma de la Figura 7.6, suponiendo que

están unidas las entradas 1C, 2C y 3C, 4C a la señal CLK.

2Q

3Q

4Q

t

t

t

t

t

t

t

t

t

Figura 7.6. Cronograma de funcionamiento del latch 7475, donde CLK

es C1, C2 y C3, C4.

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:44

Página 187

7. Análisis y diseño con registros

7.1 Análisis de registros de almacenamiento

Actividades propuestas

3

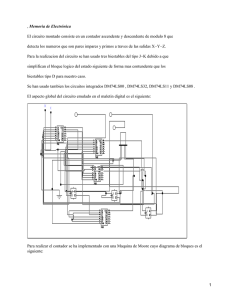

Circuito de aplicación con contadores y latchs integrados.

• Explica razonadamente las siguientes cuestiones:

a) ¿Por qué se ponen a cero los displays cuando

se alimenta el circuito?

b) ¿Por qué cada vez que se pulsa S1, se incrementa en uno el visualizador?

c) ¿Por qué cada vez que se activa S2, se pueden

producir incrementos del turno, pulsando S1,

sin que se visualicen los cambios hasta que se

desactiva S2?

• Modifica el circuito para incluir un interruptor

o pulsador que al activarse ponga a cero los contadores.

• Monta el circuito que se muestra en la Figura 7.7,

que permite indicar el turno de espera en un establecimiento de 00 a 99.

• Confirma que inicialmente el circuito se pone a

cero cuando se conecta la alimentación.

• Verifica que cada vez que se activa el pulsador S1

se incrementa en uno el visualizador.

• Comprueba que al cerrarse el interruptor S2 se

pueden producir incrementos del turno sin que

se visualicen, hasta que el interruptor S2 está de

nuevo en circuito abierto.

DECENAS

13 12 11 10

9 15 14

a b c d e

2

1

7

16

1

4

2

UNIDADES

f

13 12 11 10

IC6

7448

g

8 BI/RB0 RBI LT

6

4

1 15 14 10 11

5

9

1

"1"

3

7

8

16

IC4

7475

Q1 Q1 Q2 Q2 Q3 Q3 Q4 Q4

9 15 14

a b c d e

4

2

1

2

f

IC5

7448

g

8 BI/RB0 RBI LT

6

4

1 15 14 10 11

5

9

"1"

3

8

IC3

7475

Q1 Q1 Q2 Q2 Q3 Q3 Q4 Q4

VCC

D1

D2

D3

D4

C12 C34

2

3

6

7

13

4

D1

D2

D3

D4

C12 C34

2

3

6

7

13

R4

10 kΩ

4

S2

VCC

12

9

8 11

12

IC2

7490

QA QB QC QD

9

8 11

R2

10 kΩ

IC1

7490

QA QB QC QD

IC7A 2

3

A B R0(1) R0(2) R9(1) R9(2)

14

1

2

3

6

7

1

A B R0(1) R0(2) R9(1) R9(2)

14

1

2

3

6

S1

7400

7

IC7B 5

VCC

6

4

C1

1 μF

R1

0 kΩ

7400

+

R3

10 kΩ

VCC

Figura 7.7. Circuito para organizar el turno de una fila.

187

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:44

Página 188

7. Análisis y diseño con registros

7.1 Análisis de registros de almacenamiento

de los registros

A Estudio

de almacenamiento

Los registros de almacenamiento están formados por

un conjunto de biestables aislados entre sí, con una

señal de reloj común a todos ellos, de forma que en

todos se cargan simultáneamente los datos presentes en sus entradas, siendo accesibles en cada

momento sus entradas y salidas.

El circuito de la Figura 7.3 es un circuito de almacenamiento de datos de 4 bits, en el que la señal de

entrada se activa por flanco de subida. Su funcionamiento es muy sencillo, cada uno de los biestables

D está separado respecto de los datos de información del siguiente, de manera que cuando se pone

un dato en la entrada D de cualquiera de los biestables, éste aparece en la salida Q en el instante en

que se produce un flanco de subida en la señal de

reloj (CLK). Como todos los biestables tienen conectada la señal de sincronismo a la misma señal de

reloj, cuando en ésta se produce un flanco de

subida, los cuatro datos presentes en las entradas A,

B, C y D aparecen en las correspondientes salidas QA,

QB, QC y QD (Fig. 7.8).

capacidad de almacenamiento de 4 bits, conectados

dos a dos a una señal de sincronismo, de tal manera

que el primero y el segundo latch están sincronizados por la señal 1C, 2C (pin 13), y el tercero y el

cuarto, por la señal 3C, 4C (pin 4). Además, el circuito

dispone de una salida negada por dato almacenado.

Su estructura interna para un latch, es decir, para almacenar un solo bit, es la que se muestra en la Figura 7.9,

en la que se puede apreciar que está formado por dos

puertas AND, una NOR y dos inversores, de los cuales

uno de ellos es un amplificador de corriente. Su funcionamiento es el siguiente: cuando la entrada de Enable o C está a nivel bajo, en la salida de la puerta AND3

habrá un nivel bajo, independientemente de la entrada

de datos, mientras que a la salida de la puerta AND2

aparecerá el valor que tuviera en ese instante la salida

Qt (es decir, en el instante anterior al cambio del valor

de la entrada C). En consecuencia, a la salida de la

puerta NOR aparecerá el valor negado de Qt, que se

aprovecha para obtener la salida —

Qt, que vuelve a

negarse a la salida del buffer inversor 5, por lo que la

salida Qt no varía.

Data D

QD

QC

QB

QA

4

A otro

latch

D

C

B

A

Figura 7.8. Representación del flujo de información del

circuito de la Figura 7.3.

188

Q

3

1

5

Q

2

Enable C

Figura 7.9. Diagrama interno de uno de los latch del

C.I. 7475.

Respecto de las entradas asíncronas, las entradas

Preset están puestas a nivel alto, por lo que no

actúan, mientras que las entradas Clear están conectadas a un circuito RC de inicialización que pone a

cero las salidas del registro en el momento de alimentar el circuito. Además, el pulsador S es capaz

de poner a cero el registro cuando es activado

poniendo un nivel bajo en las entradas Clear, independientemente de la señal de sincronismo.

Cuando la entrada de Enable C está a nivel alto, a la

entrada de la puerta NOR le llega el valor del dato de

entrada y un nivel bajo; luego a su salida se tendrá el

dato de entrada negado, que vuelve a negarse para

obtener la salida Qt. Mientras que la entrada de Enable esté a nivel alto, cualquier variación de la entrada

de datos se refleja en la salida, quedando almacenado

(encerrojado) el dato sólo cuando la entrada de Enable se pone a nivel bajo. Por tanto, su tabla de funcionamiento es la que se muestra en la Tabla 7.3.

Cuando los registros de almacenamiento se activan

por nivel, también reciben el nombre de latch. Es el

caso del circuito integrado TTL 7475, que tiene una

En la Figura 7.7 se muestra un circuito en el que se

utilizan registros de datos. El circuito está constituido por dos contadores en BCD del tipo 7490

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:44

Página 189

7. Análisis y diseño con registros

7.2 Análisis de registros de desplazamiento

Entradas

Salidas

D

C

Q(t+1)

Q(t+1)

L

H

X

H

H

L

L

H

Qt

H

L

Qt

Tabla 7.3. Tabla de funcionamiento del C.I. TTL 7475.

conectados en cascada y cuyo funcionamiento ya

estudiamos en la Unidad 6. Para generar los impulsos de incremento se utiliza un circuito antirrebotes

con puertas NAND, que también se ha estudiado en

la unidad anterior. Las salidas de los contadores se

conectan a las entradas de dos circuitos del tipo

7475, que tienen unidas todas las entradas Enable,

de manera que cuando están puestas a nivel alto,

los latch son transparentes a los datos que les llegan de los contadores y éstos pasan directamente al

circuito de visualización. Cuando se quiere que salte

el turno sin que se visualice en el display, se pone

la entrada de Enable a nivel bajo; en este instante,

la información que tenían a la entrada se transfiere

a la salida, quedando ésta bloqueada (encerrojada),

por tanto, el circuito de visualización marcará el

número que tuviera en ese momento la salida del

latch. Si se activa varias veces el pulsador de cuenta

de impulsos, la visualización permanecerá en el

número que tuviera anteriormente, y sólo cuando la

señal de Enable esté a nivel alto, cambiará el nuevo

número a visualizar, que coincidirá con el número

decimal que tengan los contadores.

El circuito de visualización está compuesto por dos

decodificadores de BCD a 7 segmentos del tipo

cátodo común y que están configurados para que no

se ilumine el cero de las decenas, si el dato a visualizar es menor de 10BCD. Además, el circuito dispone

de un sistema de inicialización automática implementado por una resistencia (R1) y un condensador

(C1), que hace que los contadores se pongan a cero

al conectar la alimentación al circuito.

7.2 Análisis de registros de desplazamiento

Actividades propuestas

4

Registro de desplazamiento con biestables J-K.

• Utilizando dos circuitos integrados TTL del tipo 7476

y una puerta inversora del tipo 7404, monta un registro de desplazamiento (entrada serie/salida paralelo

y entrada serie/salida serie) de 4 bits, como el que se

muestra en la Figura 7.10.

• Conecta cada una de las salidas de los biestables (QA

a QD) a un LED indicador de nivel lógico, del equipo

didáctico sobre el que estás montando el circuito, y

la entrada de sincronismo CLK al pulsador de impulsos con un circuito antirrebotes.

• Alimenta el circuito y mide en ese instante el valor

que toman cada una de las salidas de los biestables.

Anota en la Tabla 7.4 el resultado obtenido y explica

a qué es debido.

• Si el estado de todas las salidas de los biestables

no es un nivel bajo, activa el pulsador S1.

• Utiliza el conmutador S2 para introducir un nivel

alto por la entrada de datos serie. Seguidamente,

genera un flanco de bajada por la entrada CLK. Pon

a nivel bajo el conmutador S2 y genera un flanco

de bajada por la entrada de sincronismo. Vuelve a

poner S2 a nivel alto y genera posteriormente otro

impulso de sincronismo. Pon nuevamente el conmutador S2 a nivel bajo y genera un nuevo impulso

de sincronismo. Cada vez que se genera un impulso de sincronismo, mide el estado de la salida de

cada uno de los biestables y anota el resultado en

la Tabla 7.4.

• Genera cuatro impulsos de sincronismo seguidos.

Mide y anota en la Tabla 7.4 el valor de las salidas

de los biestables para cada uno de los impulsos.

• Completa el cronograma de la Figura 7.11 de la

página 185, que indica el funcionamiento del

registro de la Figura 7.10.

(continúa)

189

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:44

Página 190

7. Análisis y diseño con registros

7.2 Análisis de registros de desplazamiento

Actividades propuestas (continuación)

QA

QB

QC

QD

VCC

VCC

2

(Datos)

S2

4

1

IC3A

16

1

(Clear)

S1

2

7404

J

PR

IC1A

Q

15

CL

3

9

6

CLK

K

Q

IC1B

7

14

12

J

PR

Q

2

11

4

1

CLK

K

7476

CL

Q

10

16

7476

8

J

PR

IC2A

Q

15

CL

3

9

6

CLK

K

7

Q

14

7476

12

J

PR

IC2B

Q

R1

10 kΩ

11

CLK

K

CL

8

Q

10

7476

+

C1

1 μF

CLK

(Sincronismo)

Figura 7.10. Registro de desplazamiento de entrada serie/salida serie con biestables J-K.

Instante de tiempo

S2

Qt

Qt+1

Qt+2

Qt+3

Qt+4

Qt+5

Qt+6

Qt+7

Qt+8

S1 = 0

X

1

0

1

0

1

1

1

1

X

QA

QB

QC

Tabla 7.4. Resultados de la Actividad 3.

• Contesta a las siguientes preguntas:

a) ¿Qué ocurre si cuando el estado de los biestables es QA

= 0, QB = 1, QC = 0 y QD = 1, activas el pulsador S1?

b) ¿Qué tipo de sincronismo emplea este registro?

c) ¿Cuántos impulsos de la señal de sincronismo tienen que producirse para que el primer dato, que se

introduce por la entrada de datos serie, aparezca

en la salida de datos serie (QD)?

190

d) ¿Cuál es el número de datos que es capaz de almacenar este registro simultáneamente?

QD

5

Ensayo y experimentación con un registro comercial

de desplazamiento entrada serie/salida serie 7491.

En la Figura 7.12, de la página siguiente, se muestra

el diagrama de conexión del registro de desplazamiento entrada serie/salida serie 7491, fabricado en

tecnología TTL.

• Conecta la entrada de reloj (pin 9) a la salida del pulsador con circuito antirrebotes del equipo didáctico,

para controlar, de forma manual, el número de impulsos que llegan al registro. Conecta las salidas

QH (pin 13) y Q¯¯H (pin 14) a los diodos indicadores de

nivel lógico. Asimismo, conecta las entradas A (pin

12) y B (pin 11) a dos conmutadores que denominaremos S1 y S2, respectivamente, y que pueden dar a

su salida un nivel alto o bajo.

• Introduce los datos que se muestran en el cronograma de la Figura 7.13 y completa las salidas que se

obtienen para cada una de las señales de reloj.

(continúa)

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:44

Página 191

7. Análisis y diseño con registros

7.2 Análisis de registros de desplazamiento

Actividades propuestas (continuación)

S2

t

CLK

t

QA

t

QB

t

QC

t

QD

Figura 7.11. Cronograma de

funcionamiento del registro

de desplazamiento de la

Figura 7.10.

t

S1

t

Figura 7.12. Diagrama de conexión

del circuito integrado 7491.

Input Input

A

B

GND CLOCK NC

QH

QH

14

13

12

11

QH

QH

A

B

10

9

8

CK

1

2

3

4

5

6

7

NC

NC

NC

NC

VCC

NC

NC

SN5491A (J)

SN54L91 (J)

SN54LS91 (J)

SN7491A (J, N)

SN74L91 (J, N)

SN74LS91 (J, N)

A

t

B

t

CLK

t

QH

t

QH

t

Qt

Q(t+1) Q(t+2) Q(t+3) Q(t+4) Q(t+5) Q(t+6) Q(t+7) Q(t+8) Q(t+9) Q(t+10) Q(t+11) Q(t+12) Q(t+13) Q(t+14) Q(t+15) Q(t+16) Q(t+17) Q(t+18) Q(t+19) Q(t+20) Q(t+21) Q(t+22) Q(t+23) Q(t+24) Q(t+25) Q(t+26)

Figura 7.13. Cronograma de funcionamiento del registro de desplazamiento entrada serie/salida serie 7491.

191

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:44

Página 192

7. Análisis y diseño con registros

7.2 Análisis de registros de desplazamiento

de los registros

A Estudio

de desplazamiento

Los registros de desplazamiento están formados por

una cadena de n biestables conectados en cascada,

de tal manera que la salida de uno es la entrada del

siguiente. Además, la entrada de sincronismo es la

misma para todos y cada uno de los biestables.

Los datos en este tipo de registros pueden transferirse en entrada serie o paralelo, la salida también

puede transmitirse en serie o paralelo, dando lugar

a distintos tipos de registros, según la forma de

introducir o extraer la información.

B

Estudio de los registros

de desplazamiento entrada

serie/salida serie

En este tipo de registros la información llega en serie

a través de un terminal y se obtiene la salida de los

datos también en serie a través de otro terminal.

En la Figura 7.10 se muestra un circuito que se comporta como un registro de entrada serie/salida serie,

si se considera que la entrada llega a través del conmutador S2 y la salida se obtiene a través de QD.

Como los biestables son del tipo Master-Slave, la

entrada de datos se transfiere en los flancos de

bajada de la señal de reloj. El número de biestables

del registro es cuatro, y como puede apreciarse,

están dispuestos de manera que la entrada J de cada

biestable está conectada a la salida Q del biestable

anterior, excepto en el primer biestable, cuya

entrada J coincide con la de datos serie. Por otra

parte, la entrada K de cada biestable está conectada

a la salida Q¯ del biestable anterior, excepto en el primero de los biestables, que está conectada a la

entrada de datos negada. Las entradas Preset están

puestas a nivel alto, por lo que no actúan, mientras

que las Clear se utilizan para inicializar el registro

poniéndolo a cero, cuando se activa el pulsador S1.

Al alimentar el circuito se produce una puesta a cero

de los biestables, ya que inicialmente el condensador C1 se encuentra descargado, por lo que, durante

un instante de tiempo, hasta que alcanza el valor de

tensión correspondiente a un nivel alto, las entradas Clear de todos los biestables están a nivel bajo,

produciendo un reset del circuito.

Supongamos que se quiere introducir la secuencia

0101. Para ello, se pone S2 = 1 y se produce un

flanco de bajada por CLK, en este mismo instante

QA = 1, mientras que QB = QC = QD = 0. Seguidamente,

se pone S2 = 0 y se genera un nuevo flanco de

bajada en CLK, lo que provoca que QB = 1 y QA = QC =

= QD = 0. Se van introduciendo el resto de los datos

de entrada y las correspondientes señales de sincronismo y se obtiene el diagrama de tiempos de la

Figura 7.14, en el que se representan también los

impulsos de sincronismo necesarios para que, por QD,

se obtenga la secuencia completa de datos.

CLK

DATOS

QA

QB

QC

QD

t

t

t

t

t

t

Figura 7.14. Cronograma de funcionamiento del registro de la Figura 7.10.

192

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:44

Página 193

7. Análisis y diseño con registros

7.2 Análisis de registros de desplazamiento

El proceso también puede verse reflejado en la

Figura 7.15.

Como puede apreciarse, este registro está realizado

con 8 biestables R-S de tipo Master-Slave pero, debido

al inversor existente entre la entrada R y S, éstas tendrán siempre valores complementarios.

Un registro entrada serie/salida serie integrado en

tecnología TTL MSI es el 7491, cuyo diagrama

interno se muestra en la Figura 7.16.

Las entradas A y B son las entradas de una puerta

NAND, que introduce la información en el primero de

los biestables, y pueden usarse, indistintamente, una

como entrada de datos y otra como entrada de validación.

Estado del registro en el instante inicial

Entrada 1

QA

QB

QC

QD

0

0

0

0

0 Salida

Su tabla de funcionamiento es la que se muestra en

la Tabla 7.5, en la que se indica el valor de la salida

QH después de 8 impulsos de sincronismo por la

entrada Clock.

Estado del registro después del primer flanco de bajada

Entrada 0

QA

QB

QC

QD

1

0

0

0

0 Salida

Input

Estado del registro después del segundo flanco de bajada

Entrada 1

QA

QB

QC

QD

0

1

0

0

Entrada 0

QB

QC

QD

1

0

1

0

A

B

QH

QH

H

L

X

H

X

L

H

L

L

L

H

H

0 Salida

Estado del registro después del tercer flanco de bajada

QA

Output

Tabla 7.5. Tabla de funcionamiento del C.I. TTL MSI 7491.

0 Salida

Estado del registro después del cuarto flanco de bajada

Entrada 1

QA

QB

QC

QD

0

1

0

1

C

0 Salida

En este instante, en la salida está el primer dato que

entró, con tres flancos de bajada más; en la salida se

obtienen los tres datos restantes.

Como la señal de reloj está conectada a un inversor, hará que el registro se active por flanco de

subida.

Figura 7.15. Movimiento de la información en el circuito

de la Figura 7.10.

A

B

Análisis de los registros

de desplazamiento entrada

paralelo/salida serie

(12)

S

(11)

Q

CK

R

Clock

S

Q

CK

Q

R

S

Q

CK

Q

R

S

Q

CK

Q

R

S

Q

CK

Q

R

S

Q

CK

Q

R

S

Q

CK

Q

R

S

Q

(13)

QH

Q

(14)

QH

CK

Q

R

(9)

Figura 7.16. Diagrama interno del registro entrada serie/salida serie 7491.

193

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:51

Página 194

7. Análisis y diseño con registros

7.2 Análisis de registros de desplazamiento

Actividades propuestas

6

Ensayo y experimentación con un registro comercial

de desplazamiento entrada paralelo/salida serie

7494.

En la Figura 7.17 se muestra el diagrama de conexión

del registro de desplazamiento entrada paralelo/salida

serie 7494, fabricado en tecnología TTL.

• Realiza el montaje que se muestra en la Figura 7.18.

• Conecta la entrada Clock (pin 8) a la salida del pulsador con circuito antirrebotes del equipo didáctico.

Conecta la salida Out (pin 9) a uno de los indicadores

de nivel lógico.

• Pon los conmutadores Load 1 y Load 2 a nivel bajo.

Activa a nivel alto el conmutador de Clear durante un

instante y ponlo nuevamente a nivel bajo.

• Utiliza el conmutador de Serial Input, e introduce

secuencialmente los datos 1, 0, 1 y 0, generando,

cada vez que se introduce un dato, un flanco de

subida por la entrada CLK (pin 8).

P2A PE2 P2B P2C GND P2D CLEAR OUTPUT

16

15

14

13

12

PE2 P2B P2C

P2A

2

3

4

10

9

P2D CLEAR

OUTPUT

P1A

P1B P1C P1D

1

11

CK

PE1 SER. IN

5

P1A P1B P1C P1D Vcc

6

7

8

PE1 SER. CLOCK

IN

SN5494 (J,W)

SN7494 (J,N)

Figura 7.17. Diagrama de conexión del circuito integrado TTL 7494.

194

• Pon a nivel alto la entrada Serial Input y genera cuatro nuevos impulsos de reloj. Mide y anota los resultados obtenidos en la Tabla 7.6.

• Genera, durante un instante, un nivel alto en la

entrada Clear. Con las entradas PE1 = PE2 = 0, pon

a nivel alto la entrada Serial Input. Seguidamente,

acciona los conmutadores de forma que en las

entradas P1A, P1B, P1C y P1D se obtengan los datos

0, 0, 1, 1, y en P2A, P2B, P2C y P2D, los datos 1, 1,

0 y 0, respectivamente. Pon, durante un instante, la

entrada PE1 a nivel alto, volviendo a situarla a nivel

bajo. Genera después cuatro flancos de subida por

la entrada CLK. Mide y anota los resultados que se

van obteniendo en la Tabla 7.7.

• Genera un impulso a nivel alto en la entrada Clear.

Seguidamente, pon la entrada PE2 a nivel alto

durante un instante de tiempo. Genera cuatro impulsos de reloj y anota los resultados que se van obteniendo en la Tabla 7.7.

• Contesta a las siguientes preguntas:

a) ¿Cuál es la capacidad de almacenamiento del

registro?

b) ¿Cuál es el tipo de sincronismo de la señal de

reloj del registro?

c) ¿Qué función tienen las entradas PE1 y PE2?

d) ¿Qué ocurre cuando la señal de Clear se pone a

nivel alto?

(continúa)

Clear

Impulso de

CLK

Serial

Input

1

0

0

0

0

0

0

0

0

0

—

↓

↓

↓

↓

↓

↓

↓

↓

↓

1

1

0

1

0

1

1

1

1

1

Tabla 7.6. Resultados de la Actividad 6.

Out

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:51

Página 195

7. Análisis y diseño con registros

7.2 Análisis de registros de desplazamiento

Actividades propuestas (continuación)

"1"

S1A

S1B

S1C

S1D

S2A

S2B

S2C

S2D

LOAD 1

LOAD 2

1

2

3

4

P1A

P1B

P1C

P1D

16

14

13

11

P2A

P2B

P2C

P2D

6

15

10

PE1

PE2

CLR

7

8

IN

CLK

1

0

0

0

0

0

0

0

↓

Clear

1

0

0

0

0

0

0

CLK

SERIAL INPUT

Figura. 7.18. Circuito para comprobar

el funcionamiento del registro de

entrada paralelo/salida serie 7494.

CLK

Serial Input

P1A

P1B

P1C

P1D

PE1

PE2

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

0

1

0

0

0

0

0

0

0

0

0

0

CLK

Serial Input

P2A

P2B

P2C

P2D

PE1

PE2

0

0

0

↓

↓

↓

↓

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

1

1

1

1

0

0

0

0

0

0

0

0

0

1

0

0

0

0

↓

↓

↓

SALIDA

7494

CLEAR

Clear

OUT 9

Out

Out

Tabla 7.7. Tabla de funcionamiento del C.I. 7494.

195

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:44

Página 196

7. Análisis y diseño con registros

7.2 Análisis de registros de desplazamiento

Estudio de los registros

de desplazamiento entrada

paralelo/salida serie

Los biestables se ponen a cero cuando la entrada

Clear es puesta a nivel alto; este paso es siempre previo a la carga de datos en paralelo. Además, tiene la

posibilidad de introducir dos entradas paralelo distintas, controladas por las señales PE1 y PE2. Las

señales P1A a P1D se cargan en los biestables

cuando la entrada PE1 recibe un impulso positivo,

teniendo que estar la entrada PE2 durante este

tiempo a nivel bajo. Por otra parte, las entradas P2A

a P2D se cargan en los biestables cuando a la

entrada PE2 le llega un impulso positivo y la entrada

PE1 está a nivel bajo.

En este tipo de registros de desplazamiento, la

información llega en paralelo a la entrada, que se

carga mediante una señal de control, y la salida

se obtiene en paralelo sincronizada por una señal de

reloj.

Para introducir los datos en paralelo, pueden utilizarse las entradas asíncronas o las entradas síncronas. De este modo, por ejemplo, el circuito

integrado 7494, cuya estructura interna es la que

se muestra en la Figura 7.19, utiliza las señales

asíncronas de Preset para introducir los datos en

paralelo.

El circuito integrado 7494 tiene la posibilidad de

introducir datos en modo serie y obtener la salida en

serie. Para que funcione en este modo, se deben

mantener a nivel bajo las entradas PE1 y PE2 y realizar un borrado del registro, poniendo, durante un

instante, a nivel alto la entrada Clear. Seguidamente,

se introducen los datos serie por la entrada Serial

Input (pin 7) y se genera un flanco positivo por la

entrada CLK por cada dato a cargar en serie.

El registro está formado por cuatro biestables R-S

del tipo Master-Slave, a cuyas entradas R y S

les llegan siempre señales complementarias.

Por tanto, la capacidad máxima del registro es de

4 bits. Además, como la entrada de la señal

de reloj tiene un inversor, el registro se hace

activo a los flancos ascendentes de la señal de sincronismo de entrada.

Las tablas de funcionamiento de este registro son

las que se muestran en la Tabla 7.8 de la página

siguiente.

PRESETS

P1A

P2A

(1)

PRESET

ENABLE

INPUTS

PE2

PE1

(16)

P1B

2

S PRESET QA

CK

CLEAR

P 1C

P 2C

(3)

(13)

P 1D

P 2D

(4)

(11)

(6)

1

A

CLOCK

(14)

(15)

1

SERIAL (7)

INPUT

P2B

(2)

R CLEAR QA

2

1

B

S PRESET QB

CK

R CLEAR QB

2

1

C

S PRESET QC

CK

R CLEAR QC

2

D

S PRESET QD

CK

R CLEAR

(8)

(10)

Figura 7.19. Diagrama interno del registro de desplazamiento entrada paralelo/salida serie 7494.

196

(9)

OUTPUT

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:45

Página 197

7. Análisis y diseño con registros

7.2 Análisis de registros de desplazamiento

TABLA DE FUNCIÓN DEL PRESET

(Bit A tomado como ejemplo para todos)

TABLA DE FUNCIONAMIENTO DEL REGISTRO

Preset

interno

Entradas de Preset

Preset interno A

PE1

P1A

PE2

P2A

L

L

X

X

H

X

X

X

L

L

H

X

L

X

L

X

X

H

X

L

X

L

X

X

H (Inactiva)

H (Inactiva)

H (Inactiva)

H (Inactiva)

L (Activa)

L (Activa)

Salidas

internas

Entradas

A

B

C

D

Clear

H

L

H

H

H

H

H

L

H

L

H

H

H

L

H

H

H

H

H

L

H

L

H

H

H

L

H

L

L

L

CLK Serial

X

X

L

L↓

X

X

X

X

H

L

↓

Salida

QA

QB

QC

QD

L

H

QA0

H

H

L

L

H

QB0

QA0

QAn

QAn

L

H

QC0

H

QBn

QBn

L

H

QD0

QD0

QCn

QCn

↓

QA0, QB0, QC0, QD0 = estado de QA, QB, QC y QD, respectivamente, después de producirse un flanco ascendente .

↓

QAn, QBn, QCn = nivel de QA, QB y QC, respectivamente, antes de producirse un flanco ascendente .

Tabla 7.8. Tabla de funcionamiento del circuito integrado 7494.

Otra forma de realizar la carga en paralelo en los

registros consiste en utilizar las entradas síncronas

como es el caso del circuito integrado 74166, cuyo

diagrama lógico se muestra en la Figura 7.20, en la

que puede apreciarse que el terminal Clear es asíncrono y que provoca la puesta a cero de todos los

biestables cuando se pone a nivel bajo.

Las entradas A, B, C, D, E, F, G y H se almacenan en

los biestables cuando se pone un nivel bajo en la

entrada S/L̄ (Shift/Load), todo ello sincronizado por

la señal Clock, que puede ser inhibida por la entrada Clock Inhibit. Una vez que se ha realizado la

entrada en paralelo de los datos, debe ponerse a

–

nivel alto la entrada S/L para permitir el desplazamiento de la información almacenada en cada uno

de los biestables.

El circuito 74166 también puede utilizarse como

registro de entrada serie/salida serie, utilizando

como entrada el terminal SI (Serial Input). Su funcionamiento se refleja en la Tabla 7.9.

Para una mejor comprensión de este registro de desplazamiento, en la Figura 7.21, de la página 193, se

muestra un cronograma de funcionamiento.

Entradas

Clear

Shift/load

Clock

Inhibit

L

H

H

H

H

H

X

X

L

H

H

X

X

L

L

L

L

H

Salidas internas

Clock

Serial

Input

Parallel

A ... H

QA

QB

X

L

↓

↓

↓

↓

X

X

X

H

L

X

X

X

a ... h

X

X

X

L

QA0

a

H

L

QA0

L

QB0

b

QAn

QAn

QB0

Salida

QH

L

QH0

h

QGn

QGn

QH0

a … h = nivel de las entradas A … H, respectivamente.

QA0, QB0 … QH0 = estado de QA, QB … QH, respectivamente, después de un flanco de subida de la señal de reloj.

QAn, QBn … QHn = nivel de QA, QB … QH, respectivamente, antes de un flanco de subida de la señal de reloj.

Tabla 7.9. Funcionamiento del registro 74166.

197

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:45

Página 198

7. Análisis y diseño con registros

7.2 Análisis de registros de desplazamiento

(9)

CLEAR

SERIAL INPUT (1)

SHIFT/LOAD (15)

A

(2)

R

CK

S

QA

B

(3)

R

CK

S

QB

C

(4)

R

CK

S

QC

D

(5)

R

CK

S

QD

E

(10)

R

CK

S

QE

F

(11)

R

CK

S

QF

G

(12)

R

CK

S

QG

(14)

(7)

CLOCK

(6)

CLOCK INHIBIT

H

R

CK

S

(13)

Figura 7.20. Diagrama lógico del registro de desplazamiento entrada paralelo/salida serie 74166.

198

QH

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:45

Página 199

7. Análisis y diseño con registros

7.2 Análisis de registros de desplazamiento

CLOCK

CLOCK INHIBIT

CLEAR

SERIAL INPUT

SHIFT/LOAD

A

H

L

B

C

H

L

PARALLEL D

INPUTS

E

F

H

L

G

H

H

H

OUTPUT QH

H

SERIAL SHIFT

CLEAR

INHIBIT

LOAD

H L

H L

H L

H

SERIAL SHIFT

Figura 7.21. Cronograma de funcionamiento del registro de desplazamiento 74166.

Actividades propuestas

7

Ensayo y experimentación con el registro universal

7495.

En la Figura 7.22 se muestra el diagrama de conexión

del registro de desplazamiento universal 7495 fabricado en tecnología TTL.

• Conecta las entradas A (pin 2), B (pin 3), C (pin 4),

D (pin 5), Mode Control (pin 6) y Serial Input (pin 1) a

conmutadores del equipo didáctico sobre el que estás

montando el circuito, capaces de dar a la salida un

nivel alto o bajo.

• Conecta las salidas QA, QB, QC y QD a los indicadores

de nivel lógico del equipo didáctico.

• Interconecta las entradas de Clock 1 (pin 8) y

Clock 2 (pin 9) y conéctalas a su vez a la salida

del pulsador con circuito antirrebotes.

• Pon a nivel alto la entrada Mode Control y la entrada

Serial Input a nivel bajo.

• Pon, en las entradas A, B, C y D, los valores lógicos 1,

0, 0, 1, respectivamente, y genera un flanco de

bajada por las entradas de reloj. Mide y anota el

resultado en la Tabla 7.10.

Figura. 7.22. Diagrama de conexión del circuito

integrado TTL 7495.

(continúa)

199

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:45

Página 200

7. Análisis y diseño con registros

7.2 Análisis de registros de desplazamiento

Actividades propuestas (continuación)

• Pon la entrada Mode Control a nivel alto y la entrada

D a nivel alto, y genera, seguidamente, cuatro flancos de bajada por la entrada CLK. Mide y anota los

resultados obtenidos en la Tabla 7.11.

• Pon a nivel bajo la entrada D y genera cuatro flancos

de bajada por la entrada CLK. Mide y anota en la Tabla 7.11, los resultados obtenidos.

• Contesta a las siguientes preguntas:

a) ¿Cuál es la capacidad de almacenamiento del

registro?

b) ¿Cuál es el tipo de sincronismo de la señal de

reloj del registro?

c) ¿Qué tipo de registro es el 7495, según su

forma de transferir los datos?

d) Cuando funciona como entrada serie/salida

serie, ¿en qué sentido pueden desplazarse los

datos?

• Repite la operación anterior, pero poniendo ahora los

datos 1, 0, 1 y 0 en las entradas.

• Pon la entrada Mode Control a nivel bajo y genera

cuatro flancos de bajada por la entrada de CLK. Mide

y anota en la Tabla 7.10 los resultados de las salidas

para cada uno de los impulsos de sincronismo.

• Con la entrada de Mode Control a nivel bajo, pon a

nivel alto la entrada Serial Input y genera cuatro flancos de bajada por la entrada de CLK. Pon ahora la

entrada Serial Input a nivel bajo y genera cuatro flancos de bajada por la entrada de CLK. Mide y anota los

resultados de las salidas obtenidos en la Tabla 7.10.

• Realiza las siguientes modificaciones en el circuito:

introduce los datos serie por la entrada D, conecta la

salida QD a la entrada C; la salida QC a la entrada B;

la salida QB, a la entrada A, y considera la salida QA

como la salida serie del registro.

(continúa)

CLK

Mode Control

Serial Input

A

B

C

D

—

↓

—

↓

↓

↓

↓

↓

—

↓

↓

↓

↓

↓

↓

↓

↓

1

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Tabla 7.10. Resultados de la Actividad 7.

200

QA

QB

QC

QD

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:45

Página 201

7. Análisis y diseño con registros

7.2 Análisis de registros de desplazamiento

Actividades propuestas (continuación)

CLK

Mode Control

A

B

C

D

QA

QB

QC

QD

—

↓

↓

↓

↓

↓

↓

↓

↓

1

1

1

1

1

1

1

1

1

QB

QB

QB

QB

QB

QB

QB

QB

QB

QC

QC

QC

QC

QC

QC

QC

QC

QC

QD

QD

QD

QD

QD

QD

QD

QD

QD

1

1

1

1

1

0

0

0

0

0

0

0

0

Tabla 7.11.

D

Resultados de la Actividad 7.

Análisis de los registros

de desplazamiento entrada

paralelo/salida paralelo

interno del registro universal 7495, denominado de

esta forma porque permite hacer todo tipo de

transferencias con los datos: entrada serie/salida

serie con desplazamiento a la derecha y a la

izquierda de los datos, entrada paralelo/salida

paralelo y entrada paralelo/salida serie.

Estudio de los registros

de desplazamiento entrada

paralelo/salida paralelo

Se puede apreciar que la carga de datos es similar a

la del circuito integrado 74166. En este caso, el

registro consta de 4 biestables R-S Master-Slave, a

cuyas entradas les llegan siempre datos complementarios. Además, dispone de una entrada de control que permite la carga de datos en paralelo o el

modo de trabajo entrada serie/salida serie.

En estos registros, los datos pueden ser introducidos en paralelo y extraídos en paralelo. Su estructura es similar a la que se ha mostrado en las

Figutas 7.19 y 7.20, con la salvedad de que se

hacen accesibles las salidas de todos los biestables. En la Figura 7.23 se muestra el diagrama

DATA INPUTS

A

B

1

C

(3)

(2)

MODE (6)

CONTROL

SERIAL (1)

INPUT

1

2

D

(4)

2

1

(5)

2

1

2

CLOCK 1 (9)

RIGHT-SHIFT

CLOCK 2 (8)

LEFT-SHIFT

R

R

CK

S

R

CK

S

QA

(13)

QA

R

CK

S

QB

CK

S

QC

(12)

(11)

QB

QC

QD

(10)

QD

OUTPUTS

Figura 7.23. Diagrama interno del registro universal 7495.

201

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:45

Página 202

7. Análisis y diseño con registros

7.2 Análisis de registros de desplazamiento

Se pone la entrada Mode Control a nivel alto y se

conecta la salida de cada biestable a la entrada

paralelo del precedente, convirtiéndose la entrada D

(pin 5) en la entrada de datos serie, y QA en la salida

serie.

Para el modo de trabajo entrada paralelo/salida paralelo, debe ponerse la entrada Mode Control (control de

modo) a nivel alto; cuando esto ocurre las puertas

señaladas con un 2 se abren, dejando pasar los datos

que están en las entradas paralelo A, B, C y D; si ahora

se produce un flanco de bajada por cualquiera de las

entradas de reloj, se efectúa la carga en paralelo.

En este tipo de registro hay que tener cierta precaución con los cambios de modo. En efecto, si, por

ejemplo, la entrada Clock 1 está a nivel bajo y la

entrada Clock 2 está a nivel alto y se pasa el control

de modo de nivel alto a bajo, se produce un flanco

de bajada en las entradas de reloj de los biestables,

generando un cambio en éstos.

Para que el registro trabaje como desplazamiento a

la derecha, ya sea de los datos cargados en paralelo

o de los datos que se introduzcan por la entrada

Serial Input, deberá ponerse a nivel bajo la entrada de control de modo. En este estado, las puertas

que se abren son las numeradas con un 1 y se cierran las numeradas con un 2, con lo que se produce

un desplazamiento a la derecha de los datos de los

biestables cada vez que se genera un flanco de

bajada por cualquiera de las entradas de reloj.

Esto se puede aprovechar en la carga en paralelo,

uniendo las entradas de Control Mode y Clock 2, de

manera que cuando esta unión está a nivel alto, se

selecciona el modo de carga en paralelo, y al pasar

a nivel bajo y producirse el flanco de bajada, se

hace efectiva dicha carga.

La razón de la existencia de dos señales de entrada

de reloj es proporcionar al circuito mayor flexibilidad.

Para que el circuito se comporte como un registro de

desplazamiento a la izquierda, hay que realizar las

conexiones que se muestran en la Figura 7.24.

A

B

(2)

"1" (6)

MODE CONTROL

(1)

SERIAL INPUT

Se puede resumir el modo de trabajo de este registro de desplazamiento en la Tabla 7.12 de la página

siguiente.

1

C

(3)

2

1

D

(4)

2

1

1

2

Entrada

serie

(5)

2

CLOCK 1

RIGHT-SHIFT

CLK

(9)

R

(8)

CLOCK 2

LEFT-SHIFT

R

CK

S

R

CK

QA

S

CK

QB

S

(13)

Salida

serie

QA

R

CK

QC

S

(12)

QB

(11)

QC

Figura 7.24. Modo de funcionamiento del registro 7495 como desplazamiento serie a la izquierda.

202

QD

(10)

QD

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:45

Página 203

7. Análisis y diseño con registros

7.2 Análisis de registros de desplazamiento

Inputs

Mode

Control

H

H

H

L

L

↓L

↓

↓

↓

↓

Outputs

Clocks

Parallel

Serial

2 (L)

1 (RT)

H

↓

↓

L

X

X

L

L

L

H

H

X

X

X

H

↓

↓

L

L

H

L

H

X

X

X

X

H

L

X

X

X

X

X

A

B

C

D

X

a

QB*

X

X

X

X

X

X

X

X

X

b

QC*

X

X

X

X

X

X

X

X

X

c

QD*

X

X

X

X

X

X

X

X

X

d

d

X

X

X

X

X

X

X

X

QA

QB

QC

QD

QA0

a

QBn

QA0

H

L

QA0

QA0

QA0

QA0

QA0

QB0

b

QCn

QB0

QAn

QAn

QB0

QB0

QB0

QB0

QB0

QC0

c

QDn

QC0

QBn

QBn

QC0

QC0

QC0

QC0

QC0

QD0

d

d

QD0

QCn

QCn

QD0

QD0

QD0

QD0

QD0

* El desplazamiento a la izquierda requiere una conexión externa de QB a A, QC a B y QD a C.

La entrada de datos serie es por la entrada D.

Tabla 7.12. Tabla de funcionamiento del registro de desplazamiento 7495.

203

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:45

Página 204

7. Análisis y diseño con registros

Ejercicios propuestos

Ejercicios propuestos

1

Un registro de desplazamiento de 8 bits contiene

el dato 10000110. Si se le aplica a la entrada

serie el dato 11011011:

Indica el número almacenado en el registro después

de cinco impulsos de desplazamiento. Supón que el

registro se desplaza de izquierda a derecha.

2

3

4

5

6

204

7

Analiza el funcionamiento del circuito de la

Figura 7.25.

Indica cuál es la función de cada una de las patillas

de los circuitos integrados.

8

¿Cuántos impulsos de desplazamiento se requieren

para cargar en forma serie una palabra de 16 bits

en un registro de desplazamiento de 16 biestables?

Si se dispone de un reloj digital, con acceso a

las entradas BCD que van a cada uno de los

cuatro decodificadores BCD a 7 segmentos:

Realiza un circuito que, mediante unos registros,

conmutadores, circuitos comparadores y los componentes necesarios, realice la función de despertador.

Conecta dos registros del tipo 7491 para que se

comporten como un único registro de desplazamiento entrada serie/salida serie de 16 bits.

9

Conecta dos registros del tipo 7495 para que se

comporten como un solo registro de desplazamiento entrada paralelo/salida serie de 8 bits.

10 Dado un contador Johnson de 5 biestables:

Dibuja y explica el funcionamiento de un registro de desplazamiento entrada serie/salida serie

implementado con biestables tipo D, mediante

circuitos 7474.

Conecta dos registros del tipo 7495 para que se

comporten como un solo registro o de desplazamiento de entrada/salida serie con desplazamiento hacia la izquierda.

Busca, en un catálogo de circuitos TTL, varios

registros de desplazamiento que puedan trabajar

como entrada serie/salida paralelo.

¿Cuántos estados distintos tiene? Indica cuáles son.

11 Un contador en anillo de 4 biestables puede utilizarse como divisor de frecuencia por:

a) 4

b) 6

c) 8

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:45

Página 205

7. Análisis y diseño con registros

Ejercicios propuestos

Ejercicios propuestos

a b c d e

1

2

4

f

IC1

7448

g

8 BI/RB0 RBI LT

Vcc

IC2

7475

Q1 Q1 Q2 Q2 Q3 Q3 Q4 Q4

D1

D2

D3

D4

C12 C34

Salida de impulsos

siguiente etapa

QA QB QC QD

IC3

7490

Carga de datos

A B

Entrada

R0(1) R0(2) R9(1) R9(2)

Vcc

Reset

Figura. 7.25 Circuito de aplicación con circuitos integrados.

205

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:45

Página 206

7. Análisis y diseño con registros

Actividades complementarias

Actividades complementarias

1

Ensayo y experimentación con un contador Johnson.

• Inicializa el circuito, activando durante un instante el pulsador S1. Anota después el resultado

en la Tabla 7.13.

• Genera ocho flancos de bajada por la entrada de

reloj. Mide y anota los resultados parciales y final

que obtengas en la Tabla 7.13.

• Partiendo del estado que se muestra en el cronograma de la Figura 7.27, completa el cronograma

de funcionamiento.

• Utilizando biestables J-K del tipo 7476, implementa un circuito contador Johnson como el que se

muestra en la Figura 7.26.

• Conecta la entrada de reloj al pulsador con circuito antirrebotes del equipo didáctico.

• Conecta las salidas de los biestables a los indicadores de estado lógico.

QA

QB

QC

QD

VCC

IC1A

CLK

J

PR

Q

CLK

K

IC1B

J

PR

Q

CLK

CL

Q

7476

K

CL

IC2A

J

PR

Q

CLK

Q

7476

K

CL

IC2B

J

PR

R1

10 kΩ

Q

CLK

Q

7476

K

CL

Inicialización

S1

Q

7476

+

C1

1 μF

Figura 7.26. Contador Johnson con biestables J-K conectados como un registro.

CLK

QA

QB

QC

QD

S1

t

t

t

t

t

t

Figura 7.27. Cronograma de funcionamiento del contador Johnson del circuito de la Figura 7.26.

206

07 GIL PADILLA - Electrónica digital y microprogramable.qxd

4/12/06

04:45

Página 207

7. Análisis y diseño con registros

Actividades complementarias

Actividades complementarias

• Conecta la entrada de reloj al pulsador con circuito antirrebotes del equipo didáctico.

• Conecta las salidas de los biestables a los indicadores de estado lógico.

• Inicializa el circuito, activando durante un instante

el pulsador S1. Anota el resultado en la Tabla 7.14.

Genera, seguidamente, cinco flancos de bajada por

la entrada de CLK. Mide y anota en la Tabla 7.14 los

resultados que se van obteniendo.

• Partiendo del estado que se muestra en el cronograma de la Figura 7.27, completa el cronograma

de funcionamiento correspondiente al circuito de

la Figura 7.28.

• Realiza un contador en anillo utilizando para ello

el circuito integrado 7495.

• Contesta las siguientes preguntas:

a) ¿Cuántos bits necesita un contador binario

para contar 8 estados distintos?

b) ¿Cuántos bits necesita un contador Johnson

para contar 8 estados distintos?

c) ¿Tienen alguna ventaja este tipo de contadores?

• Realiza un contador Johnson con alguno de los

registros comerciales que has estudiado en esta

unidad.

2

Ensayo y experimentación con un contador en anillo.

• Utilizando 4 biestables J-K del tipo 7476, monta

un contador en anillo como el que se muestra en

la Figura 7.28.

S1

CLK

ON

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

—

↓

↓

↓

↓

↓

↓

↓

↓

QA

QB

QC

QD

S1

CLK

ON

OFF

OFF

OFF

OFF

OFF

—

↓

↓

↓

↓

↓

QA

QB

QC

QD

Tabla 7.14. Resultados de la Actividad 2.

Tabla 7.13. Tabla de funcionamiento del contador Johnson.

QA

QB

QC

QD

VCC

IC1A

J

CLK

PR

Q

J

Q

K

CLK

K

IC1B

PR

Q

J

Q

K

CLK

CL

7476

CL

IC2A

PR

Q

J

Q

K

CLK

7476

IC2B

PR

Q

R1

10 kΩ

CLK

CL

7476

CL

Q

S1

7476

+ C1

1 μF

Figura 7.28. Contador en anillo.

207