Electrónica: Contador BCD (Binary-Coded Decimal) Natural

Anuncio

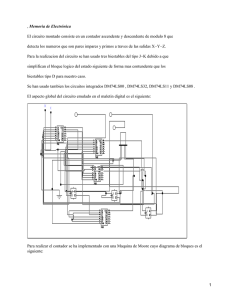

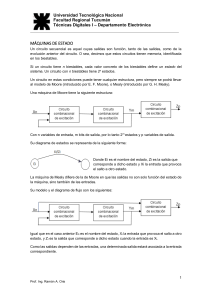

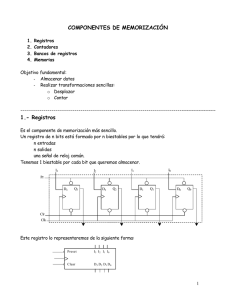

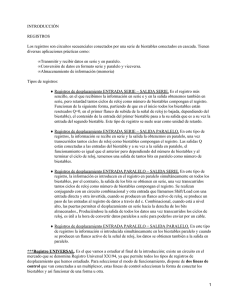

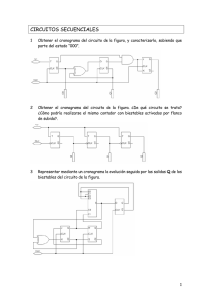

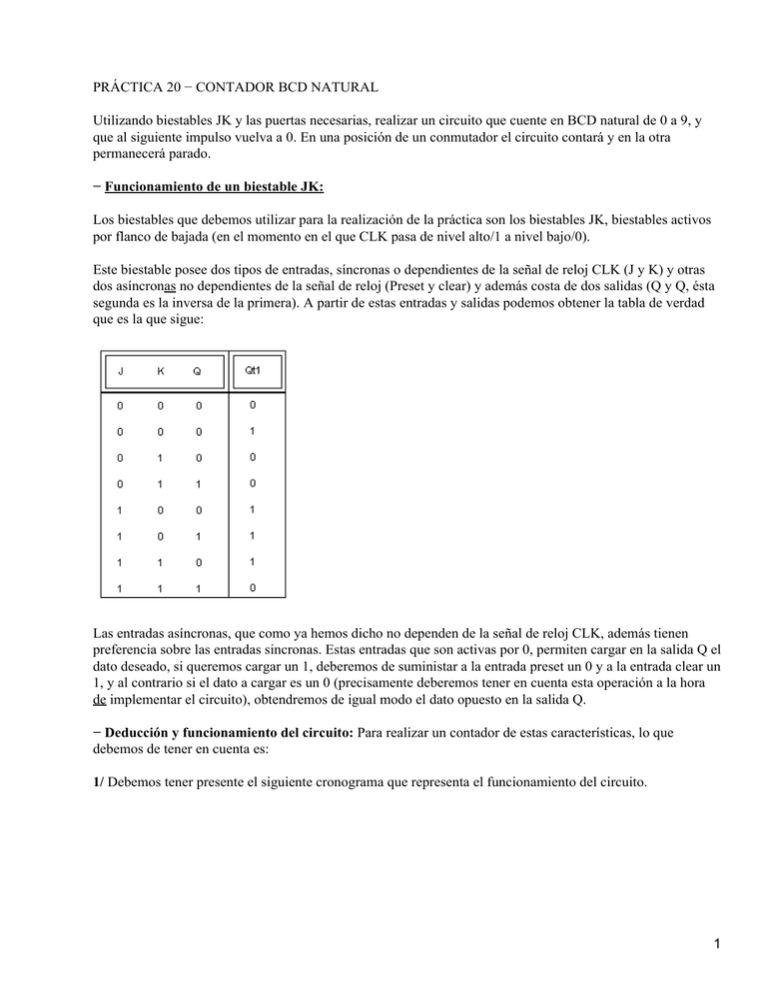

PRÁCTICA 20 − CONTADOR BCD NATURAL Utilizando biestables JK y las puertas necesarias, realizar un circuito que cuente en BCD natural de 0 a 9, y que al siguiente impulso vuelva a 0. En una posición de un conmutador el circuito contará y en la otra permanecerá parado. − Funcionamiento de un biestable JK: Los biestables que debemos utilizar para la realización de la práctica son los biestables JK, biestables activos por flanco de bajada (en el momento en el que CLK pasa de nivel alto/1 a nivel bajo/0). Este biestable posee dos tipos de entradas, síncronas o dependientes de la señal de reloj CLK (J y K) y otras dos asíncronas no dependientes de la señal de reloj (Preset y clear) y además costa de dos salidas (Q y Q, ésta segunda es la inversa de la primera). A partir de estas entradas y salidas podemos obtener la tabla de verdad que es la que sigue: Las entradas asíncronas, que como ya hemos dicho no dependen de la señal de reloj CLK, además tienen preferencia sobre las entradas sincronas. Estas entradas que son activas por 0, permiten cargar en la salida Q el dato deseado, si queremos cargar un 1, deberemos de suministar a la entrada preset un 0 y a la entrada clear un 1, y al contrario si el dato a cargar es un 0 (precisamente deberemos tener en cuenta esta operación a la hora de implementar el circuito), obtendremos de igual modo el dato opuesto en la salida Q. − Deducción y funcionamiento del circuito: Para realizar un contador de estas características, lo que debemos de tener en cuenta es: 1/ Debemos tener presente el siguiente cronograma que representa el funcionamiento del circuito. 1 2/ Para realizar el circuito debemos de tener como punto de partida el modelo del contador binario de módulo m. 3/ Debemos de tener en cuenta que debemos de forzar una puesta a 0 cuando el contador intente llegar al número 10 en binario (1010), éste número no debe de aparecer en las salidas, ya que en BCD natural no existe el número 10, que se corresponde al número 1010 en binario. 4/ Ya que debemos contar hasta 9, tendremos que utilizar cuatro biestables JK y unirlos mediante conexión asíncrona. Para forzar la puesta a 0, debemos aprovechar los 1 (Que observamos que corresponden a los biestables de las salidas Q1 y Q3) y adivinar cuál es la puerta lógica que con dos 1, nos da como resultado en su salida un 0 (recordar que el preset y el clear son activos por 0), comprobamos que únicamente la puerta NAND nos realiza esta operación. Por ello llevamos los dos 1 a las entradas de la misma, y con su salida a 0 forzamos los clear. Para poder detener e iniciar la cuenta, deberemos encontrar una puerta que estando conectados a sus dos entradas por un lado un conmutador y por otro el generador de frecuencias, nos permita detener la cuenta con un 0 del conmutador para volverla a iniciar cuando el conmutador vuelva a +Vcc, es decir, sólamente cuando las dos entradas se encuentren en nivel alto, la puerta nos dará en su salida un impulso, cosa que nos proporciona el producto lógico, expresado en la tabla de verdad de la puerta lógica AND que se muestra a continuación. 2 De esta manera obtenemos el circuito resultante: Medios utilizados para la realización de la memoria: Medios bibliográficos: −Apuntes de electrónica digital. −Fotocopias de los integrados 74LSXX. Medios informáticos: − Electronics Work bench EDA. − Microsoft word. Medios utilizados para la realización de la práctica: 3 − Entrenador digital. − 2 integrados 74 LS 76 (biestables Jk). − 1 integrado 74 LS 00 (NAND). − 1 integrado 74 LS 08 (AND). − cableado. 4 5