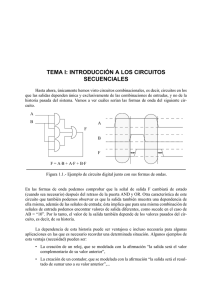

TEMA 5. Sistemas Secuenciales Síncronos

Anuncio

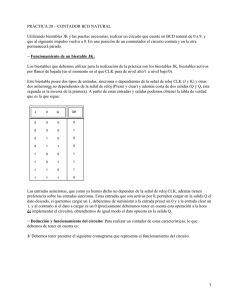

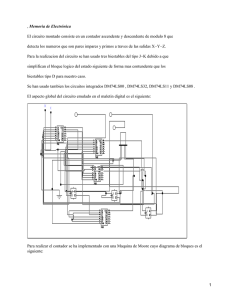

TEMA 5. Sistemas Secuenciales Síncronos 1. Introducción. (2-5) 1.1 Definición de sistema secuencial. Concepto de estado (6-10) 1.2 Esquema general de un sistema secuencial. (11) 1 3 Máquina de estados finitos. 1.3 finitos Autómata. Autómata (12-13) (12 13) 2. Autómatas de Mealy y Moore. (14-15) y ((16)) 2.1 Modelo de Mealy. 2.2 Modelo de Moore. (17) 3. Especificación y etapas en el diseño de sistemas secuenciales. (18-20) 3 1 Tablas y diagramas de transición entre estados. 3.1 estados (21-24) (21 24) 3.2 Ejemplos de sistemas secuenciales (25-39 ) p Canónica de sistemas secuenciales ((40-41)) 4. Implementación 4.1 Ejemplos de implementación (42-43) 5. Especificación de SS mediante Diagramas ASM. (44- 45) 5 1 Ejemplos de implementación (46-53) 5.1 (46 53) 6. Modelado VHDL de máquinas de estados finitos (FSM) (46-61) j p de modelado VHDL ((62-67)) 6.1 Ejemplos 7. Análisis y Síntesis de Sistemas Secuenciales (68-70) 1 1.. INTRODUCCIÓN (I) D Dentro de los sistemas m secuenciales,, los SISTEMAS EM SECUENCIALES SÍNCRONOS es el caso más habitual y más sencillo, en el diseño p práctico de dichos sistemas digitales • Sistemas síncronos: í aquellos ll en los l que existe all menos una señal de reloj que va marcando en que momento se pueden d producir d i los l cambios bi en las l salidas lid del d l circuito. i it • Disparo de reloj por flanco. flanco 2 1.. INTRODUCCIÓN (II) EJEMPLO: Circuito que no es combinacional: generador de bit de paridad Constrúyase un circuito que nos indique, si el número total de 1´s presentados en su entrada, hasta un instante determinado, determinado es par o impar. impar x z El sistema se puede especificar utilizando un tabla de verdad, en la q que se reflejen j las variables q que intervienen en el sistema: entrada, x; salida, z; “situación del sistema en un instante” 3 1. INTRODUCCIÓN (III) EJEMPLO: Circuito que no es combinacional: Generador de bit de paridad TABLA DE VERDAD ENTRADA SALIDA X(t) Z(t) Nº par de 1 N 1´ss 0 1 par impar Nº impar de 1´ss N 0 1 impar par Situación hasta el instante “t” 4 1.. INTRODUCCIÓN (IV) Será á un sistema que tendrá: á 1. Una única entrada para la llegada de datos en serie (X) 2 Una única salida que será el bit de paridad par, 2. par de la secuencia de bits llegados al sistema hasta el momento t (Z) sta os internos, nt rnos, pu puesto sto qu que to toda a la a h historia stor a pasa pasada a 3.. Dos estados puede reducirse a dos situaciones: PAR (P) sii ell número ú d “1” llegados de ll d hasta h ell instante i t es PAR IMPAR (I) si el número de “1” llegados hasta el instante t es IMPAR → Será necesaria 1 variable de estado y una función f que relacione el estado presente, con el estado anterior y la entrada presente de acuerdo con el esquema: X = 0 PAR IMPAR X = 1 PAR IMPAR IMPAR MP R P R PAR 5 1.1 DEFINICIÓN DE UN SISTEMA SECUENCIAL (I) Un sistema es secuencial si la salida en cada instante t, t depende tanto del valor de las entradas presentes en ese instante, como de la “historia” historia del sistema, sistema estado esta determinada, determinada por el estado del sistema en el instante que comienza a operar y por los valores de las entradas en ese momento inicial. Un sistema secuencial depende de su “historia”, pues de acuerdo de ella, el sistema estará en cada instante en un estado determinado 6 1.1 DEFINICIÓN DE UN SISTEMA SECUENCIAL (II) 1. D p Dependen del tiempo: mp p para una m misma m combinación m de entradas pueden obtenerse salidas diferentes; de esto, se deduce, q que estas dependen p del momento en que se presentan las distintas combinaciones de entrada. 2. Debe existir realimentación de la salida a la entrada: para que ell estado t d del d l circuito i it repercuta t en ell valor l de la salida, dicho estado ha de almacenarse y presentarse al circuito, circuito como un “tipo tipo de variable de entrada”. 7 1.1 DEFINICIÓN DE UN SISTEMA SECUENCIAL (III) En los sistemas secuenciales síncronos con disparo por flanco del reloj está garantizado que: reloj, 1. Transcurrido un tiempo suficiente desde el flanco del reloj, los valores actualizados (nuevos valores) de las señales de entrada a la memoria del sistema (biestables) se propagarán a lo largo del mismo y éste adqu adquirirá r rá una conf configuración gurac ón estable. Las entradas al sistema deben ser estables y no deben existir lazos de realimentación puramente combinacionales (es decir sin que atraviesen una célula de almacenamiento, un biestable). 2 2. No sucederán cambios en el sistema hasta el nuevo flanco del reloj, reloj pues las realimentaciones quedan cortadas en los biestables. 8 1.1 DEFINICIÓN DE UN SISTEMA SECUENCIAL (IV) VARIABLES El número de variables independientes p es el conjunto j de: Entradas al sistema. z Salidas S lid de d los l biestables. bi bl El estado interno del circuito: z • Es igual E i l a la l combinación bi ió de d valores l que tengan t l los biestables. Ap partir de las entradas al sistema m y el estado interno se generarán: z • z z Las salidas del circuito. Las propias entradas a los elementos de memoria (biestables). 9 1.1 DEFINICIÓN DE UN SISTEMA SECUENCIAL (V) Variables: entrada xi, i=1…n, salida zj, j=1…m estado siguiente Yk, k=1…p, k=1 p estado actual yl, l=1…q, Ecuaciones: Zj(t) = f1 (x1(t) x2(t)….. xn(t), Y1(t) Y2(t)….Yp(t)) Yl(t) = f2 (x1(t) x2(t)….. xn(t), y1(t) y2(t)….yp(t)) yk(t+1) = f3 (Y1(t) Y2(t)….Y (t) Yq(t)) 10 1.2 ESQUEMA GENERAL DE UN SISTEMA SECUENCIAL ENTRADAS CIRCUITO COMBINACIONAL SALIDAS MEMORIA (Bi (Biestables) bl ) Estado actual Estado futuro Reloj 11 1.3 MÁQUINA DE ESTADOS FINITOS. AUTÓMATA El modelo g general de la máquina q síncrona que estamos presentando es una “Máquina de Estados Finitos Finitos” o FSM (Finite State Machine), dado que el número de combinaciones de los valores de los biestables; es decir, en nuestro caso los estados t d internos i t d l sistema, del i t es finito. fi it 12 1.3 MÁQUINA DE ESTADOS FINITOS. AUTÓMATA La teoría de circuitos secuenciales se le denomina también teoría de autómatas, autómatas ya que estos ante una sucesión de valores de entrada que se presentan a lo largo del tiempo, tiempo proporcionan en cada instante una salida que depende de toda la secuencia de entradas llegadas hasta ese momento. Entrada/salida Estado 13 2. AUTÓMATAS DE MEALY Y DE MOORE (I) Autómata de MEALY Las salidas dependen p de las entradas y de las variables de estado. Autómata de MOORE Las salidas no dependen directamente de las entradas, sino que éstas primeramente han de producir un cambio de estado; este cambio de estado determinará el nuevo valor de las salidas. z z z lla salida l d está á vinculada l d all estado, d cambiando b d sincrónicamente ó con el reloj. Las salidas no se modifican en las transiciones (arcos). (arcos) Cada cambio de la entrada, produce una modificación de las variables de excitación, que producirán con el reloj, un nuevo estado. d Las L salidas lid dependerán d d á de d este estado. d 14 2. AUTÓMATAS DE MEALY Y DE MOORE (II) Las máquinas de Moore, Moore al cambiar las salidas de forma síncrona con el reloj, son en general, más estables q que las máquinas q de Mealy, y y ya q que cualquier q ruido transitorio que pudiera traer la entrada queda eliminado en las salidas. Las máquinas de Moore constituyen un caso particular de las máquinas de Mealy. 15 2.1 MODELO DE MEALY ENTRADAS Estado actual CIRCUITO COMBINACIONAL MEMORIA (Biestables) SALIDAS Estado futuro RELOJ 16 2.2 MODELO DE MOORE CIRCUITO COMBINACIONAL ENTRADAS SALIDAS CIRCUITO COMBINACIONAL MEMORIA ( (Biestables) ) Estado actual Estado futuro Reloj 17 3. ESPECIFICACIÓN Y ETAPAS DE DISEÑO DE SISTEMAS SECUENCIALES (I) El diseño de un sistema secuencial constará de dos etapas: 1. Determinación del número de estados necesarios, o lo que es equivalente, del número de biestables, N z El número de estados P deberá cumplir: P ≤ 2N. 2 Construcción de la red combinacional, 2. combinacional tal que para cada combinación del estado interno y las entradas proporcione las salidas requeridas y los valores que han de atacar a los biestables → z Estos últimos darán lugar, lugar en el próximo ciclo de reloj, reloj al nuevo estado. 18 DISEÑO DE LA MEMORIA: Elección del tipo de autómata (Mealy o Moore) Determinación D t i ió del d l número ú d estados de t d internos, i t P P. Codificación de los estados Descripción formal del problema (Tabla de estados, Di Diagrama d de t transiciones, i i t bl tabla d de t transiciones, i i diagramas ASM,…..) Elección del tipo de biestable. Determinación D t i ió del d l número ú d biestables, de bi t bl N N. P ≤ 2N 19 DISEÑO DEL SISTEMA (RED) COMBINACIONAL Identificación de variables: entrada, salida, estado y excitación. R Realización li ió de d la l tabla t bl de d transiciones t i i entre t estados t d y la l tabla de salida. Obtención de las funciones lógicas de salida y de entradas a los biestables. Realización física mediante elementos combinacionales ( (puertas t s lógicas, ló i s muxe´ss, …….)) 20 3.1 TABLAS Y DIAGRAMAS DE TRANSICIÓN ENTRE ESTADOS (I) La tabla de transición entre estados es directamente la especificación de la parte combinacional del sistema secuencial E la tabla de transición entre estados,, p En para cada estado y para combinación de las entradas se recoge cuál va a ser el próximo estado y qué valor van a tomar las señales de salida. 1. Se nombran los estados. 2. Se codifican los estados: 1.. Se cu S cuenta nta el núm número ro de estados sta os distintos. st ntos. 2. Se escoge el número adecuado de biestables. 3 3. Se asigna un código (una combinación de variables) distinto a cada estado. 21 3.1 TABLAS Y DIAGRAMAS DE TRANSICIÓN ENTRE ESTADOS ((II)) Un diagrama de transición de estados, diagramas de flujo, autómata es una representación que muestra las transiciones entre los estados, de acuerdo con las condiciones de conmutación. Se representa utilizando los siguientes símbolos: Círculos. z Indican un estado. Dentro del círculo aparecerá p una etiqueta q del tipo: codificación del estado. (MEALY) codificación del estado/salida del estado. estado (MOORE) Arcos. z Indican la transición de un estado origen g a un estado destino p por medio de una ocurrencia en alguna de sus entradas. El arco se acompaña de una etiqueta del tipo: entrada o entradas. entradas (MOORE) entrada o entradas/salida o salidas. (MEALY) 22 3.1 TABLAS Y DIAGRAMAS DE TRANSICIÓN ENTRE ESTADOS ((III)) AUTÓMATA DE MEALY AUTÓMATA DE MOORE Entrada/salida Entrada Estado Estado Salida Entrada/salida Entrada Estado Estado •0 salida 23 3.1 TABLAS Y DIAGRAMAS DE TRANSICIÓN ENTRE ESTADOS (IV) EJEMPLOS: EJEMPLOS Autómatas de MEALY 0 1/1 0/1 0 Autómatas de MOORE 1/0 1 0/0 1 0/0 2 1 1/0 0 0/1 0 1/11 0 1/10 1 0/10 2 0/00 1 1 1/01 0 2/11 1 1/01 0/11 2/1 1 1/1 0/00 0 0 24 3.2 EJEMPLOS DE CIRCUITOS SECUENCIALES (I) 1. Diséñese un detector de secuencia, que detecte la secuencia i 101 y que una vez detectada d t t d permanezca en esa situación hasta que se inicialice. Impleméntese con p D disparados p por f p flanco de bajada, j , con biestables tipo señal CLEAR, y puertas lógicas necesarias para la red combinacional. 1. 2. 3. 4. 5. Realícese mediante un autómata de Mealy. Realícese mediante un autómata de Moore. Implementación canónica del detector Descripción mediante diagramas ASM Modelado VHDL en los tres estilos de descripción 25 3.21 DETECTOR DE SECUENCIA “101” (II) Autómata de MOORE 0 1 0/0 1 1/0 x 0 2/0 1 Tabla de transición entre estados 3/1 Estado actual (t) 0 Diagrama de transición entre j ) estados ((flujo) Entradas: E (una entrada) Salidas: S (una salida) Estados: 4 estados 4 = 2P Î p=2 Nª Biestables: 2 Q1 0 0 0 0 1 1 1 1 Q0 0 0 1 1 0 0 1 1 Ent (t) E 0 1 0 1 0 1 0 1 Estado sig.(t+1) D1 0 0 1 0 0 1 1 1 Sal (t) D0 0 1 0 1 0 1 1 1 S 0 0 0 0 0 0 1 1 26 3.21 DETECTOR DE SECUENCIA “101” (III) D1 E D0 E Q1 Q0 0 1 Q1 Q0 0 1 00 0 0 00 0 1 01 1 0 01 0 1 11 1 1 11 1 1 10 0 1 10 0 1 D0 = E + Q 1 Q 0 S = Q 1Q 0 D1= EQ E 0 + EQ E 1 27 3.21 DETECTOR DE SECUENCIA “101” (IV) Implementación con biestables tipo D y puertas lógicas E D0 = E + Q 1 Q 0 D1= EQ0 + EQ1 S = Q 1Q 0 S D1 CLK CLR Q1 D0 Q1 CLK CLR Q0 Q0 CLK RESET 28 3.21 DETECTOR DE SECUENCIA “101” (V) Autómata de MEALY 0/0 1/0 0 1/0 1 X/1 0/0 2 1/1 Tabla de transición entre estados 3 Q1 0 0 0 0 1 1 1 1 0/0 Diagrama de transición entre estados (flujo) Entradas: E (una entrada) Salidas: S (una salida) Estados: 4 estados 4 = 2P Î p=2 Nª Biestables: 2 Q0 0 0 1 1 0 0 1 1 E 0 1 0 1 0 1 0 1 D1 0 0 1 0 0 1 1 1 D0 0 1 0 1 0 1 1 1 S 0 0 0 0 0 1 1 1 29 3.21 DETECTOR DE SECUENCIA “101” (VI) S E Q1 Q0 0 1 D0 = E + Q 1 Q 0 00 0 0 D1= EQ0 + EQ1 01 0 0 S = Q 1E + Q 1Q 0 11 1 1 10 0 1 30 3.21 DETECTOR DE SECUENCIA “101” (VII) Implementación con biestables tipo D y puertas lógicas E D0 = E + Q 1 Q 0 D1= EQ0 + EQ1 S = Q 1E + Q 1Q 0 D1 CLK CLR D0 Q1 Q0 Q1 CLK CLR Q0 CLK S RESET 31 3.22 EJEMPLOS DE CIRCUITOS SECUENCIALES (II) 2. Diséñese un contador hasta 10 (módulo 10) síncrono, mediante un autómata de Moore, Moore e impleméntese con biestables tipo D disparados por flanco de bajada, con señal CLEAR, y puertas lógicas para la red combinacional. 0 9 Autómata de Moore: Entradas: no tiene entradas 1 8 2 7 3 f con Estados: hasta 10 se codifica 4 bits → 4 biestables 10 estados; 10 ≤ 2P Î p=4 6 4 5 Nº Biestables N Biestables: 4 Salidas: es el estado Diagrama de flujo 32 3.22 Contador módulo 10 (II) ESTADO ACTUAL ESTADO PRÓXIMO Q3 Q2 Q1 Q0 D3 D2 D1 D0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 0 0 0 0 0 0 1 1 0 x x x x x x 0 0 0 1 1 1 1 0 0 0 x x x x x x 0 1 1 0 0 1 1 0 0 0 x x x x x x 1 0 1 0 1 0 1 0 1 0 x x x x x x 33 3.22 Contador módulo 10 (III) D0 Q1Q0 D1 Q1Q0 Q3Q2 00 01 11 10 Q3Q2 00 01 11 10 00 1 0 0 1 00 0 1 0 1 01 1 0 0 0 01 0 1 0 1 11 X X X X 11 X X X X 10 1 0 X X 10 0 0 X X D0= Q0 D1= Q1Q0+ Q3Q1Q0 D2 Q1Q0 Q3Q2 00 01 11 10 00 0 0 1 0 01 1 1 0 1 11 X X X X 10 0 0 X X D3 Q1Q0 Q3Q 00 01 11 10 00 0 0 0 0 01 0 0 1 0 11 X X X X 10 1 0 X X 2 D2= Q2Q1+ Q2Q0+ Q2Q1Q0 D3= Q3Q0+ Q2Q1Q0 34 3.22. Contador módulo 10 (IV) Implementación: puertas lógicas y biestables tipo D disparados por flanco de bajada D3 CLK CLR Q3 D2 Q3 CLK CLR Q2 Q2 D1 CLK CLR D0 Q1 Q1 CLK CLR Q0 Q0 CLK RESET 35 3.23,4,5 EJEMPLOS DE CIRCUITOS SECUENCIALES (III) 3. Una máquina expendedora de billetes de transporte, admite billetes de 5€ y 20€. El precio del billete unitario es de 15€. La máquina debe admitir billetes hasta que se alcance o se supere el precio del billete, en ese momento lo expende y da el cámbio, si fuese preciso. Diséñese un autómata de Mealy y otro de M Moore, que permita it construir st i una máquina á i de d estas st s característ ís tícas, con el menor número de estados posible. 4. Diséñese una red con salida alta, que detecte si el número de unos incluido en una secuencia de tres bits es impar. Constrúyase el sistema utilizando biestables tipo D disparados por flanco de bajada y puertas lógicas básicas 5 Diséñese un sistema secuencial síncrono utilizando biestables 5. tipo D disparados por flanco de bajada de la señal de reloj, que genere en su salida reversiblemente y a voluntad la secuencia d los de l números ú pares codificados difi d con tres t bit bits 36 3.23 MÁQUINA EXPENDEDORA (I) EJ 3 Autómata de Mealy Autómata de Moore ai,bi ai,bi /ci+1si ai,bi /ci+1si ai,bi Estado/ cisi ci 20 20 20/15 billlete 5/0 20 0/5 billete 0/10 billete 0/15 billete 0 20 5/0 billete 20/0 billete 5 20 5 5 20/15 billete 10 5/0 0/0 5/0 5 5 10/0 37 3.24 RED DE DETECCIÓN DE NÚMERO DE 1´S (I) EJ4 Variables EJ4: V i bl : 0 0/0 1 0/0 3 0/0 entrada t d w salida z estados: 5 estados; 5 ≤ 2P Î p=3 estado QA QB QC excitación DA DB DC 1/0 1/0 1/1 0 3 biestables tipo D 1/0 0/1 1/0 2 0/0 4 38 3.24 RED DE DETECCIÓN DE NÚMERO DE 1´S (II) Estado actual (t) Entrada (t) Estado próximo Qi(t+1)=Di Salida (t) QA QB QC W DA DB DC Z 0 0 0 0 0 0 0 1 0 0 0 1 1 0 0 0 0 0 0 0 1 1 0 1 0 1 1 0 1 0 0 0 0 0 1 1 0 0 0 1 1 0 0 1 0 1 0 0 0 0 1 1 1 1 0 1 0 0 0 0 0 0 0 1 1 1 0 0 0 0 0 1 0 0 0 0 0 0 1 0 1 1 0 0 1 1 0 1 1 1 1 1 0 0 0 1 1 1 1 1 1 1 0 1 39 4. IMPLEMENTACIÓN CANÓNICA DE SS: CONSTRUCCIÓN CON BIESTABLES,, MUX´ES Y DECODIFICADORES ((I)) Utilización de circuitos que presenten regularidad en su estructura: multiplexores y decodificadores. decodificadores Consideraciones para la implementación del sistema combinacional: Decodificación D difi ió de d estados: t d l las variables i bl de estado d t d se toman como entradas a un decodificador → las salidas serán los estados Realización del secuenciamiento de los estados mediante multiplexores → el valor de las variables que determinan el estado siguiente, variables de excitación, solamente depende de las entradas al sistema. Esto supone la utilización de un mux, mux por cada biestableÎ – – Las entradas de control de los mux´es: variables de estado Las entradas de los mu mu´es: es: funciones combinacionales de las entradas del sistema 40 4.IMPLEMENTACIÓN CANÓNICA DE SS: CONSTRUCCIÓN CON BIESTABLES,, MUX´ES Y DECODIFICADORES ((II)) DIAGRAMA DE BLOQUES Entrada cc 0 1 2 3 D1 MUX Q1 Q1 CLK C1 C0 2 3 D0 MUX CLK C1 C0 CLK … … cc … 0 1 C1 DEC C0 0 1 2 3 … Q0 SAL2 Q0 cc SAL1 ……. 41 4.1 EJEMPLOS DE IMPLEMENTACIÓN (I) 1. Diséñese un detector de secuencia, que detecte la secuencia i 101 y que una vez detectada d t t d permanezca en esa situación hasta que se inicialice. Impleméntese con p D disparados p por f p flanco de bajada, j , con biestables tipo señal CLEAR, y puertas lógicas necesarias para la red combinacional. 1. 2. 3. 4. 5. Realícese mediante un autómata de Mealy. Realícese mediante un autómata de Moore. Implementación canónica del detector. Descripción mediante diagramas ASM Modelado VHDL en los tres estilos de descripción 42 4.11 Detector de secuencia 101 (VIII) D0= E + Q1Q0 D1= EQ Q0 + EQ Q1 SMoore = Q1Q0 SMealy = Q1E + Q1Q0 43 5. ESPECIFICACIÓN DE SS MEDIANTE DIAGRAMAS ASM (I) o Los diagramas de flujo son muy útiles para especificar sistemas secuenciales simples. o Hasta H t una docena d d estados de t d aproximadamente. i d t o Por este motivo, motivo vamos a presentar otro método de especificación de sistemas secuenciales: los diagramas de maquinas de estado algorítmicas o ASM (“Algorithmic State Machine”). o Nos N describen d ib d forma de f sistemática i t áti y estructurat t da el algoritmo de una máquina secuencial 44 5. ESPECIFICACIÓN de SS MEDIANTE DIAGRAMAS ASM (II) Estos diagramas expresan detalladamente el algo algoritmo que se debe de seguir para resolver un determinado t rm na o pro problema. ma. Indican: n o p Los estados por los que puede atravesar el sistema. Las condiciones L di i que producen d transiciones i i entre estados. Entre dos estados hay un ciclo de reloj. Las señales de salida que se deben producir en cada estado. 45 5. ESPECIFICACIÓN de SS MEDIANTE DIAGRAMAS ASM M (III) ( ) Un diagrama ASM consta de los siguientes símbolos: Rectángulos (disponen de un pequeño círculo en el ángulo superior izquierdo, para incluir el nombre). zIdentifican los estados. zDentro del rectángulo se especifican aquellas salidas que se activan siempre que nos encontremos en dicho estado, estado con independencia de los valores que tomen las entradas. Rombos o hexágonos. g zPermiten expresar bifurcaciones en el flujo de control. Óvalos. Óvalos zIndican las salidas condicionales. – Siempre se presentan a continuación de una bifurcación. bifurcación 46 5. ESPECIFICACIÓN de SS MEDIANTE DIAGRAMAS ASM (IV) 1. Secuenciamiento de estados. 2. X X Y Si Z 3. Bifurcaciones en el flujo de g m . control del algoritmo. No ¿A=1? ¿A 1? Z Y Salidas condicionales. X Si No ¿A=1? Z B:= 1 Y 47 5. ESPECIFICACIÓN de SS MEDIANTE DIAGRAMAS ASM (V) Ejemplo INIC Si SAL1:= 1 No ¿Entrada=1? U SAL2:= S L 1 SAL2:= 1 SAL2 V 48 5. ESPECIFICACIÓN de SS MEDIANTE DIAGRAMAS ASM (VI) COMENTARIOS: 1. Dado que hay salidas condicionales el autómata es de Mealy. 2 Tenemos 3 estados → necesitamos 2 biestables. 2. biestables 3. Variables: entrada E salidas l d Sall1 Sall2 estados inic,, u,, v 4. Utilizaremos implementación canónica y biestables tipo D disparados p por flanco de bajada. p j 49 5. ESPECIFICACIÓN de SS MEDIANTE DIAGRAMAS ASM (VII) Tabla de transición entre estados y de salida Estado actual Nombre Q1 INIC: 0 INIC: 0 U: 0 V: 1 Q0 0 0 1 0 Entradas Entrada 0 1 x x Estado siguiente D1 D0 U: 0 1 V: 1 0 INIC: 0 0 INIC: 0 0 Salidas Sal1 Sal2 1 0 1 1 0 1 0 0 D0= INIC•E= Q1Q0E D1= INIC•E= Q1Q0E Sal1= INIC= Q1Q0 Sal2= INIC•E+ U= Q1Q0E+ Q1Q0 50 5. ESPECIFICACIÓN de SS MEDIANTE DIAGRAMAS ASM (VIII) Implementación canónica del ejemplo Entrada 00 01 10 11 D1 MUX 4:1 CLK C1 C0 Q1 Q1 C1 DEC C0 00 01 10 11 D0 MUX 4:1 CLK C1 C0 00 01 10 11 Q0 SAL2 Q0 CLK SAL1 51 5.11 DETECTOR DE SECUENCIA “101” (IX) 1. Diséñese un detector de secuencia, que detecte la secuencia i 101 y que una vez detectada d t t d permanezca en esa situación hasta que se inicialice. Impleméntese con p D disparados p por f p flanco de bajada, j , con biestables tipo señal CLEAR, y puertas lógicas necesarias para la red combinacional. 1. 2. 3. 4. 5. Realícese mediante un autómata de Mealy. Realícese mediante un autómata de Moore. Implementación canónica del detector. Descripción mediante diagramas ASM Modelado VHDL en los tres estilos de descripción 52 5.11 DETECTOR DE SECUENCIA “101” (X) Autómata de MEALY 0/0 Autómata de MOORE 1/0 0 1/0 1 X/1 0/0 2 1/1 3 0 0/0 0/0 1 1 1/0 x 0 2/0 1 3/1 0 53 6. MODELADO VHDL DE MÁQUINAS DE ESTADOS FINITOS ((FSM)) ((I)) • Modelos de Moore y Mealy • Metodología de diseño de FSM - Modelo Comportamiento (Algorítmico) - Señales de Reset - Varios PROCESS - Modelo Flujo de datos (Transferencia entre registros) - Modelo M d l estructural t t l 54 4. METODOLOGÍA DE DISEÑO DE (FSM´S) (II) Niveles de Descripción asociados con los HDLs 1) Diagrama o Tabla de estados, diagrama ASM Entrada Entrada } Entrada/salida Estado Estado Salida lida Moore Entrada/salida Comportam ento o Comportamiento algorítmico Estado Estado Mealy 2) Ecuaciones del estado futuro y salidas D1(t+1) = C1(t) A(t) + C0(t) A(t)’+ ...... D0(t+1) = C1(t) B(t) + C0(t) B(t)’+ ...... X(t) = ........ Y(t) = ................ 3) Implementación del circuito: instanciación de componentes y conexionado Dispositivos lógicos (puertas: NOT, AND... MUX, DECODERS, .....) Elementos de memoria ((biestables)) } Flujo de datos o Transferencia entre registros i } Estructural 55 4. MODELO ALGORÍTMICO DE UNA FSM (III) • Consideraciones Generales: El estilo del código tiene que ser independiente de la máquina de estados que se diseñe. Diferentes formas de modelar la misma máquina: Número de procesos PROCESS Sentencias IF o CASE Uso de señales o de variables El uso de la sentencia WAIT o lista de sensibilidad ¿Debe ¿D b ser s i i i li d la inicializada l máquina má i en un estado st d válido? ¿Hay que utilizar señal de reset? Portabilidad del código 56 4. MODELO ALGORÍTMICO DE UNA FSM (IV) • MODELO DE MEALY • DOS PROCESOS: uno para la generación del estado futuro y de la salida y otro para la actualización de la memoria S lid futuro: Salida, f t PROCESS (entrada, ( t d e_actual) t l) salida <= ENTRADAS SALIDAS CIRCUITO COMBINACIONAL e_futuro <= Actual: PROCESS (reset, (reset clok) Estado actual MEMORIA (Biestables) Estado futuro RELOJ e_actual t l <= 57 4. MODELO ALGORÍTMICO DE UNA FSM (V) • MODELO DE MOORE • TRES PROCESOS PROCESOS: uno para la generación del estado futuro otro para la generación de la salida y el tercero para la actualización de la memoria CIRCUITO COMBINACIONAL Salida: PROCESS (e_actual) salida <= ENTRADAS Futuro: PROCESS (entrada, e_actual) Futuro e actual) e_futuro <= Actual: PROCESS (reset, (reset clok) e_actual <= SALIDAS CIRCUITO COMBINACIONAL MEMORIA (Biestables) Estado actual Estado futuro Reloj 58 4. MODELADO ALGORÍTMICO DE UNA FSM (VI) • Uso de señales o de variables: los estados deben definirse con un tipo de datos enumerado y deben ser señales para que puedan comunicar procesos • Sentencias IF o CASE: los estados deben modelarse con sentencia CASE y las transiciones con sentencias IF • ¿Debe ser inicializada la máquina en un estado válido?: es recomendable que se inicialice en un estado inicial • ¿Hay que utilizar señal de reset?: es recomendable • La señales q que activan PROCESS deben ir en la lista de sensibilidad o en WAIT: En la generación de las salidas y/o el estado futuro, deben incluirse l todas d las l señales l que entran en ell bloque bl En el bloque de memoria se incluirá siempre el reloj y la señal reset si es asíncrona reset, asíncr na 59 4. MODELADO EN FLUJO DE DATOS DE UNA FSM (VII) • Se parte de las ecuaciones lógicas • Se utilizan sentencias de asignación concurrente de señal • ¿Hay que utilizar señal de reset?: es recomendable • La señales que activan PROCESS deben ir en la lista de sensibilidad o en WAIT WAIT: – Generación de las salidas y/o del estado futuro ((entradas a los biestables)) – Di <= – Si <= – Generación del estado actual (reloj y reset) – Qi <= ( ….reset, rrising s ng_edge, edge, fall fallinf nf_edge…..) edge…..) 60 4. MODELADO ESTRUCTURAL DE UNA FSM (VIII) • Se debe disponer, en la librería WORK, de los componentes necesarios para la implementación. implementación • Se instacian y se conectan con las señales adecuadas • Biestables, Biestables puertas, puertas muxe muxe´ss, decoder decoder´ss ,….. – POR MAP 61 6.1 EJEMPLOS DE MODELADO VHDL (XI) 1. Diséñese un detector de secuencia, que detecte la secuencia i 101 y que una vez detectada d t t d permanezca en esa situación hasta que se inicialice. Impleméntese con p D disparados p por f p flanco de bajada, j , con biestables tipo señal CLEAR, y puertas lógicas necesarias para la red combinacional. 1. 2. 3. 4. 5. Realícese mediante un autómata de Mealy. Realícese mediante un autómata de Moore. Implementación canónica del detector Descripción mediante diagramas ASM Modelado VHDL en los tres estilos de descripción 62 6.11 DETECTOR DE SECUENCIA “101” (XII) AUTÓMATA DE MEALY 0/0 1/0 0 1/0 X/1 0/0 1 2 1/1 3 0/0 AUTÓMATA DE MOORE 0 0/0 1 1 1/0 x 0 2/0 1 3/1 0 63 6.11 Detector de secuencia “101” (XIII) •RESET •RESET 64 6.11 Detector de secuencia “101” (XIV) •RESET •RESET 65 6.11 Detector de secuencia “101” (XV) •and2_1 d •and2_2 d AUTÓMATA DE MEALY 0/0 1/0 0 1/0 / X/1 0/0 / 1 •and2_3 2 1/1 / 3 0/0 AUTÓMATA DE MOORE 0 0/0 1 1 1/0 x 0 2/0 1 •or2 1 •or2_1 3/1 •aux 1 •aux •and2_2 2 •aux 2 •aux 3 0 •or2_3 •or2_2 66 6.11 Detector de secuencia “101” (XVI) 67 7.ANÁLISIS Y SÍNTESIS DE SISTEMAS SECUENCIALES (I) Dos formas contrapuestas de abordar el estudios de los sistemas secuenciales: a. Síntesis o construcción de sistemas secuenciales: partiendo de una especificación encontrar el sistema cuya implementación cumpla los requerimientos exigidos. b Análisis de sistemas secuenciales: a la vista b. implementación, indicar la operación que realiza de una 68 7.ANÁLISIS Y SÍNTESIS DE SISTEMAS SECUENCIALES (II) EJEMPLOS de ANÁLISIS VDD P P D0 Q0 T1 CLK Q1 CLK Q0 C C Q1 reset CLK VDD 69 7.ANÁLISIS Y SÍNTESIS DE SISTEMAS SECUENCIALES (III) EJEMPLOS de ANÁLISIS (II) •x*y •00 •x*y •01 MUX •x •10 •x •11 •QA •0 •00 •x •01 MUX •x •10 •x •D •○ •0 •00 •1 •01 MUX •0 •10 •1 •11 •QA •CLK •QB •QB •D DB •D •○ •QB •CLK CLK •11 •QA •QA •D DA •QB •Z Z 70