Tema 5: Amplificadores de entrada diferencial

Anuncio

TEMA 5: AMPLIFICADORES DE ENTRADA

DIFERENCIAL

d

Francisco J. Franco Peláez

d

ri

Apuntes para uso en la asignatura Electrónica Analógica, impartida en la Ingeniería Superior

p

.u

c

m

m

o

w

:/

/

w

w

id

e

rs

tt

p

h

U

n

iv

Pa

ra

u

so

de

C

alu

m

a

d

n

os

de

la

lu

.e

te

s

n

se

d

e

M

a

Electrónica en la Facultad de Físicas de la Universidad Complutense de Madrid.

1

Amplicadores de Entrada Diferencial

Tema 5

Índice

1. Nociones generales sobre amplicadores diferenciales

3

1.1.

Denición y usos . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3

1.2.

Modo común y diferencial . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4

2. Pares diferenciales

2.1.1.

Tecnología Bipolar . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6

2.1.2.

Tecnología CMOS / Transistores JFET . . . . . . . . . . . . . . . . . . . .

9

d

6

12

2.2.1.

Corriente de polarización de la entrada

. . . . . . . . . . . . . . . . . . . .

12

2.2.2.

Tensión de oset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13

2.2.3.

Corriente máxima de salida

13

2.2.4.

Impedancia de entrada y salida

. . . . . . . . . . . . . . . . . . . . . . . .

14

2.2.5.

Frecuencia máxima de trabajo . . . . . . . . . . . . . . . . . . . . . . . . .

14

M

a

d

ri

No idealidades en un par diferencial . . . . . . . . . . . . . . . . . . . . . . . . . .

d

e

. . . . . . . . . . . . . . . . . . . . . . . . . .

14

2.3.1.

Tecnología bipolar . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14

2.3.2.

Tecnología CMOS/JFET

2.3.3.

Mejoras de los pares diferenciales con carga activa

. . . . . . . . . . . . . .

19

2.3.4.

Uso de pares diferenciales como amplicadores operacionales . . . . . . . . .

20

. . . . . . . . . . . . . . . . . . . . . . . . . . .

w

.u

c

m

m

16

h

tt

p

:/

/

w

w

id

e

rs

p

de

C

de

so

n

iv

Pa

ra

u

U

lu

.e

te

s

n

se

. . . . . . . . . . . . . . . . . . . . . . . . . .

la

Pares diferenciales con carga activa

alu

m

a

d

n

2.3.

. . . . . . . . . . . . . . . . . . . . . . . . . .

o

2.2.

Par diferencial con cargas resistivas

os

2.1.

6

Electrónica Analógica

Ingeniería Superior en Electrónica

2

Amplicadores de Entrada Diferencial

Tema 5

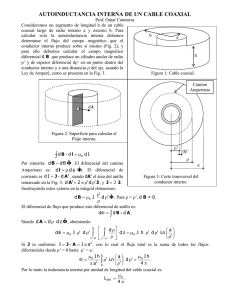

Figura 1: Esquema básico de funcionamiento de un amperímetro. La tensión de salida puede ser

d

ri

d

recogida por un conversor A/D y procesada por un microcontrolador.

M

a

1. Nociones generales sobre amplicadores diferenciales

d

e

1.1. Denición y usos

Un amplicador diferencial es un dispositivo con dos entradas cuya salida es proporcional a la

lu

.e

te

s

n

se

diferencia de tensión entre ambas. Esto quiere decir que la salida crece a medida que lo hace la tensión

la

aplicada en una entrada y decrece si aumenta la aplicada a la otra. Esto nos permite distinguirlas

de

entre sí pues la primera entrada se llama entrada no inversora en tanto que la segunda, entrada

inversora .

p

m

alu

m

a

d

n

os

En la gran mayoría de los casos, las señales de entrada son tensiones pero la salida puede ser bien

tensión, bien corriente. En el caso de que la salida sea tensión, ésta puede ser absoluta o diferencial.

c

m

C

o

Finalmente, existe la posibilidad de que haya un términal adicional, llamado de referencia, cuyo

valor se suma directamente a la salida. Éste sería el caso de los amplicadores de instrumentación,

.u

de

que se estudiarán en temas posteriores.

w

id

so

El uso de esta familia de amplicadores es variado. Por un lado, pueden utilizarse para medir

w

w

e

rs

Pa

ra

u

diferencias de tensión en el circuito, como es el caso de un amperímetro clásico. En este aparato, la

corriente que alimenta un circuito crea una pequeña diferencia de tensión entre los extremos de una

/

:/

iv

resistencia, que es medida por un amplicador diferencial y transmitida a un acondicionador de señal

U

n

(Fig. 1). En otros casos, nos permite eliminar el ruido en señales de baja calidad como se muestra

tt

p

en Fig. 2, donde se le resta la tensión de referencia a una señal aparentemente inútil de tal modo

h

que se regenera la señal correcta.

Sin embargo, uno de los usos más extendidos de los amplicadores diferenciales es la estabilización

de sistemas. Así, una de las entradas puede utilizarse para realimentar el sistema convirtiendo la salida

en una entrada más. Evidentemente, la realimentación debe ser negativa para que el sistema no sea

1

inestable . La otra entrada puede utilizarse para introducir la señal de interés. Básicamente, éste es

el principio fundamental de trabajo de la mayor parte de los circuitos lineales con un amplicador

operacional. En realidad, un amplicador operacional no es sino un amplicador diferencial con muy

1 ½Ojo!, no es lo mismo realimentación negativa que realimentación a través del terminal inversor. Casi siempre,

se usará este terminal para introducir la realimentación pero, en algunos casos, no se debe proceder de este modo.

Electrónica Analógica

Ingeniería Superior en Electrónica

3

Amplicadores de Entrada Diferencial

Tema 5

(a)

(b)

(c)

Figura 2: Señal con alto nivel de ruido (a), señal de referencia (b) y señal regenerada al restar la

M

a

d

ri

d

otras dos señales (c).

d

e

Figura 3: Equivalente circuital de la tensión común y diferencial.

la

lu

.e

te

s

n

se

alta ganancia e impedancia de entrada innita.

la tensión aplicada a la entrada no inversora de un amplicador diferencial y

VB

la

p

VA

os

Sea

de

1.2. Modo común y diferencial

m

alu

m

a

d

n

tensión aplicada a la otra entrada. El objetivo de un amplicador diferencial es restar ambas señales

c

m

1

VD = · (VA − VB )

2

(1)

.u

de

C

una nueva tensión igual a:

o

y multiplicarlas por un valor mayor que cero. En este caso, salta a la vista que es conveniente denir

w

id

so

que llamaremos tensión o modo diferencial . Otra tensión de interés es la media aritmética de ambas

w

w

1

VC = · (VA + VB )

2

(2)

:/

/

e

rs

n

iv

Pa

ra

u

señales. Ésta se llama tensión o modo común y se calcula como:

h

tt

p

U

Es trivial encontrar entonces la siguiente relación:

V =V +V

A

C

D

V =V −V

B

C

D

(3)

Esto nos permite transformar un circuito en uno equivalente que tome en cuenta estas nuevas

deniciones (Fig. 3). En un amplicador diferencial ideal, es conveniente que la salida solo dependa

de

VD

y no de

VC .

Sin embargo, esto no suele ser posible. Así, si suponemos que la salida es de

Electrónica Analógica

Ingeniería Superior en Electrónica

4

Amplicadores de Entrada Diferencial

Tema 5

tensión, se va a cumplir que, generalmente:

VOU T = VOS + AD ·VD + AC ·VC

AD es la ganancia diferencial y

AC la ganancia en modo común. Es trivial demostrar que AD > 0 pues, si no fuera así, bastaría

con intercambiar los papeles de los terminales no inversor e inversor. En cambio, AC puede tener

cualquier valor aunque, lógicamente, |AC | << AD . Por otro lado, si reemplazamos los valores de

donde

VOS

(4)

es la tensión de oset, típica de todo amplicador,

d

ri

1

1

VOU T = VOS + · (AD + AC ) ·VA − · (AD − AC ) ·VB =

2

2

(5)

En otras palabras, el modo común inuye en la salida

e

AC = KA − KB .

M

a

= VOS + KA ·VA − KB ·VB

de lo que se deduce que

d

las tensiones de modo común y diferencial por las tensiones reales, puede demostrarse que:

d

solo cuando las ganancias de cada una de las dos entradas no se han apareado adecuadamente.

lu

.e

te

s

n

se

Por otra parte, en caso de que el amplicador sea no lineal, es necesario denir las ganancias en

la

torno al punto de operación por medio de derivadas parciales:

∂VOU T KB = −

∂VB Q

∂VOU T AD =

∂VD Q

∂VOU T AC =

∂VC Q

(6)

p

os

de

∂VOU T KA =

∂VA Q

m

alu

m

a

d

n

Para medir la calidad de un amplicador diferencial, suele utilizarse un parámetro llamado razón

Se dene como:

c

m

CM RR.

(7)

.u

AD CM RR = AC w

so

de

C

o

de rechazo al modo común , que en inglés se abrevia como

w

w

id

Pa

ra

u

Es un parámetro adimensional, carente de unidades, por lo que suele expresarse en decibelios.

e

rs

Sin embargo, las deniciones de Eq. 1-2 no representan la única manera de denir las tensiones

/

iv

de modo común y diferencial. En algunos textos y situaciones, se preere hacer equivalente la tensión

:/

n

de la entrada inversora con el modo común y la diferencia con la entrada no inversora como el modo

tt

p

h

U

diferencial. Así, la representación de Fig. 4 se opondría a la de Fig. 3. Es fácil ver que, entonces,

VA = VC∗ + VD∗

VC∗ = VC − VD

⇒

VB = VC∗

VD∗ = 2·VD

Carecen de asterisco los términos y parámetros relacionados con la denición usual de modo

común y modo diferencial. Se puede deducir fácilmente que:

A∗D =

Electrónica Analógica

∂VOU T ∂VD

1

∂VOU T

=

· ∗ = ·AD

∗

∂VD

∂VD ∂VD

2

Ingeniería Superior en Electrónica

(8)

5

Amplicadores de Entrada Diferencial

Tema 5

Figura 4: Equivalente circuital de la denición alternativa de tensión común y diferencial.

1

∂VC∗

∂VC∗ ∂VC

∂VC∗ ∂VD

1

1

=

=

·

+

·

=

−

∗

AC

∂VOU T

∂VC ∂VOU T

∂VD ∂VOU T

AC

AD

d

(9)

d

ri

En ambos casos, se ha empleado la regla de la cadena. En el segundo caso, se ha tenido que realizar

las operaciones con el inverso de la ganancia en modo común para que la aplicación de esta regla

d

e

2. Pares diferenciales

M

a

fuera coherente desde el punto de vista matemático.

lu

.e

te

s

n

se

Todo amplicador diferencial, sea cual sea cual sea su complejidad, está basado en una estructura

de

la

llamada par diferencial. El par diferencial está compuesto por los siguientes elementos:

1. Dos transistores idénticos (o al menos, muy bien apareados) cuyos emisores (o fuentes, si son

m

o

alu

m

a

d

n

PMOS, N-JFET, P-JFET, ...

p

os

FET) están conectados al mismo nodo. Pueden ser de cualquier tipo: NPN, PNP, NMOS,

.u

c

m

IQ .

de

fuente de corriente,

C

2. El nudo donde se conectan los dos emisores/fuentes se drena (alimenta) por medio de una

e

rs

w

Pa

ra

u

transistores.

w

w

id

so

3. Las entradas del par diferencial, cuyas tensiones se restarán, son las bases/puertas de los

/

iv

4. Dos cargas se conectan a los colectores/drenadores de los transistores. Estas cargas pueden

:/

U

n

ser simples resistencias o fuentes de corriente con elevada impedancia de salida.

h

tt

p

2.1. Par diferencial con cargas resistivas

En este caso, se conecta al colector/drenador de cada transistor dos resistencias exactamente

iguales. Suele tomarse la salida como la diferencia de tensión entre los dos colectores/drenadores.

2.1.1. Tecnología Bipolar

Pueden darse dos casos: NPN (Fig. 5a) y PNP (Fig. 5b). En ambos, se debe suponer que los

transistores bipolares se encuentran en zona activa directa para que el funcionamiento sea correcto.

Existen dos maneras de determinar la relación entre la entrada y la salida. Por un lado, se puede

Electrónica Analógica

Ingeniería Superior en Electrónica

6

Amplicadores de Entrada Diferencial

Tema 5

(b)

d

(a)

d

ri

Figura 5: Pares diferenciales bipolares con cargas resistivas. NPN (a) y PNP (b). Puede apreciarse

hacer un análisis directo en DC para obtener la relación entre

VO

M

a

la distinta posición de la fuente de corrientes pues deben estar unidos al nudo de los emisores.

y

VA − VB .

Las ventajas de

e

este ataque consisten en que se pueden determinar con facilidad los valores de la tensión de oset

d

de la salida, la distorsión, etc. El inconveniente es que las ecuaciones derivadas son relativamente

lu

.e

te

s

n

se

complicadas e inmanejables si se añaden más elementos. La otra solución consiste en estudiar el

la

equivalente en pequeña señal del amplicador. En este caso, solo se puede obtener un parámetro,

de

que es la ganancia diferencial pero, en muchos casos, es el único que interesa.

p

os

Para abordar el problema utilizando el método DC, debemos jarnos en que, para el par NPN:

m

si se suponen las dos resistencias perfectamente apareadas. Por

.u

IEA + IEB = IQ

(11)

w

id

so

de

otra parte, se cumple que:

(10)

c

m

R· (ICA − ICB )

C

que se convierte en

o

alu

m

a

d

n

VO = (VCC − RB ·ICB ) − (VCC − RA ·ICA ) = RA ·ICA − RB ·ICB

IC

. Si denominamos

IE

IEA = IS · exp

VE

a la tensión del nudo donde convergen los emisores, se

VA − VE

N ·VT

IEB = IS · exp

VB − VE

N ·VT

tt

p

U

n

iv

descubre que:

w

w

αF =

/

2

:/

terístico

e

rs

Pa

ra

u

Ahora, imaginemos que los transistores son exactamente iguales y que tienen un parámetro carac-

h

Si divido ambas expresiones entre sí:

IEA

= exp

IEB

VA − VB

N ·VT

= exp

2·VD

N ·VT

Si utilizamos esta expresión para reducir el número de variables de Eq. 11:

IEB · exp

2 Por otra parte, no olvidemos que

Electrónica Analógica

αF =

2·VD

N ·VT

+ IEB = IQ ⇒

hF E

hF E +1 .

Ingeniería Superior en Electrónica

7

Amplicadores de Entrada Diferencial

d

ri

d

Tema 5

VD

exp

−

N ·VT

IQ

= IQ ·

=

2·VD

VD

VD

1 + exp N ·VT

exp − N ·VT + exp N ·VT

d

e

⇒ IEB

M

a

Figura 6: Relación entrada-salida en un amplicador diferencial BJT.

2·VD

N ·VT

·IEB = IQ ·

exp

VD

N ·VT

exp − NV·VDT + exp NV·VDT

p

os

de

IEA = exp

la

lu

.e

te

s

n

se

y, lógicamente,

m

alu

m

a

d

n

Operando, se acaba por deducir la siguiente relación entre la entrada y la salida:

c

m

VD

N ·VT

.u

w

⇒ VO = αF ·R·IQ · tanh

w

w

id

e

rs

Pa

ra

u

so

de

C

o

− exp − NV·VDT

⇒

VO = R· (ICA − ICB ) = αF ·R· (IEA − IEB ) = αF ·R·IQ ·

VD

VD

exp − N ·VT + exp N ·VT

exp

VD

N ·VT

(12)

/

iv

Esta expresión es válida siempre que los transistores se encuentren en zona activa directa. Fig.

:/

n

6 muestra el ejemplo de simular un par diferencial formado por dos transistores bipolares 2N2222A

tt

p

U

con resistencias de 1 kΩ de carga a medida que varía la corriente de alimentación de 1 mA a 2 mA

con pasos de 0.2 mA. Es fácil ver que, si

|VD | >> N ·VT , |VO | → αF ·R·IQ

h

la función anterior es similar a:

VO ≈

αF ·R·IQ

·VD .

N ·VT

y, que en torno a 0 V,

(13)

Un modo alternativo de atacar el problema consiste en buscar directamente la ganancia en pequeña

señal, que es el parámetro más importante del amplicador diferencial. Así, los circuitos de Fig. 5

se transforman en los de Fig. 7, sea cual sea el tipo de transistor. En este circuito, es fácil ver que:

vO = R·hf e · (ib1 − ib2 )

Electrónica Analógica

Ingeniería Superior en Electrónica

8

Amplicadores de Entrada Diferencial

Tema 5

vD .

d

ri

entiende que la excitación en pequeña señal es la componente diferencial,

d

Figura 7: Equivalente en pequeña señal de un par diferencial BJT con resistencias de carga. Se

vD − ve

hie

−vD − ve

ib2 =

hie

e

M

a

ib1 =

d

ib1 + hf e ·ib1 + ib2 + hf e ·ib2 = 0

de

la

lu

.e

te

s

n

se

v

De esta última ecuación, se deduce inmediatamente que ib1 = −ib2 por lo que ib1 = D y vO =

hie

2·R·hf e

·vD . Veamos cuanto vale esta ganancia en función de los parámetros del punto de operación:

hie

os

2·R·hf e

2·R·hf e ·IB1

2·R·hf e

2·R·hF E ·IB1

2·R·IC1

= N ·VT =

=

=

hie

N ·VT

N ·VT

N ·VT

I

p

o

C

y que, en el punto de

w

.u

2·R·IC1

2·R

1

αF ·R·IQ

2·R·hf e

=

=

·αF · ·IQ =

hie

N ·VT

N ·VT

2

N ·VT

id

Pa

ra

u

so

de

IE1 = IE2 =

αF ·IE1

c

m

hf e con hF E . Ocurre que IC 1 =

1

·I de lo que se deduce que la ganancia es:

2 Q

Para el penúltimo paso, se identicó

operación,

m

alu

m

a

d

n

B1

w

w

e

rs

Con lo que se demuestra que, los resultados de los modelos en pequeña y gran señal son compatibles.

/

:/

n

iv

2.1.2. Tecnología CMOS / Transistores JFET

tt

p

U

Pueden darse cuatro posibilidades, mostradas en Fig. 8: Par NMOS (a), par PMOS (b), par

JFET de canal N (c) y par JFET de canal P (d). Las ecuaciones derivadas de un transistor MOS

h

son idénticas a las del JFET con la misma polaridad, cambiando la tensión umbral por la tensión

de pinch-o. Sin embargo, nos vamos a centrar en el caso de los transistores NMOS, en los que el

estudio es más sencillo al ser todos los parámetros positivos.

Supondremos que

VS

es la tensión del nudo de fuente, común a ambos transistores. Es fácil ver

entonces que:

IQ = IDS1 + IDS2

1 W

IDS1 = k· · (VA − VS − VT H )2

2 L

Electrónica Analógica

Ingeniería Superior en Electrónica

9

Amplicadores de Entrada Diferencial

Tema 5

(b)

(c)

(d)

d

(a)

(14)

d

e

1 W

IDS2 = k· · (VB − VS − VT H )2

2 L

VO = R· (IDS1 − IDS2 )

M

a

d

ri

Figura 8: Pares diferenciales bipolares con transistores de efecto campo.

1 W

k se representaba como

2 L

ahora que el término

IDS1

− VD =

β

s

por simplicidad

3

y que

VA = VC + VD , VB =

p

IDS2

+ VD = VC − VS − VT H

β

m

alu

m

a

d

n

os

s

β

la

Es fácil ver, entonces, que

de

VC − VD .

lu

.e

te

s

n

se

Se ha supuesto que los dos transistores y resistencias están perfectamente apareados. Recordemos

c

m

C

o

Esto nos permite librarnos de la incómoda presencia de distintas tensiones y reducir el problema a

resolver el siguiente sistema de ecuaciones:

.u

w

w

w

id

e

rs

Pa

ra

u

so

de

( √

√

√

IDS1 − IDS2 = 2 β·VD

IDS1 + IDS2

=

IQ

/

IDS1 −

√

IDS2

2

tt

p

h

U

n

√

:/

iv

Para resolverlo, elevemos la primera ecuación al cuadrado:

⇒ IDS1 ·IDS2 =

√

= IDS1 + IDS2 +2 IDS1 ·IDS2 = 4β·VD2 ⇒

|

{z

}

IQ

2β·VD2

1

− IQ

2

2

1

= 4β 2 ·VD4 + IQ2 − 2βIQ ·VD2 ⇒

4

1

⇒ IDS1 · (IQ − IDS1 ) = 4β 2 ·VD4 + IQ2 − 2βIQ ·VD2 ⇒

4

1

2

⇒ IDS1

− IQ ·IDS1 + 4β 2 ·VD4 + IQ2 − 2βIQ ·VD2 = 0

4

Esta ecuación cuadrática se resuelve fácilmente. Descartamos, por absurda, la solución negativa ya

3 Y, de paso, para hacer que las ecuaciones sean más fáciles de extrapolar a JFETs.

Electrónica Analógica

Ingeniería Superior en Electrónica

10

Amplicadores de Entrada Diferencial

Tema 5

que implicaría que la corriente uye hacia arriba, de un modo antinatural, y se llega a la solución:

IDS1

s

1

1

1 2

2

2

4

2

= IQ + · IQ − 4· 4β ·VD + IQ − 2βIQ ·VD =

2

2

4

d

ri

d

r

1

1

1

= IQ + · IQ2 − 4·4·β 2 ·VD4 − 4· IQ2 + 4·2βIQ ·VD2 =

2

2

4

q

1

1

= IQ + · 8βIQ ·VD2 − 16β 2 ·VD4 =

2

2

s

p

1

2β 2

= IQ + 2βIQ ·VD · 1 −

·V

2

IQ D

s

p

1

2β 2

= IQ − 2βIQ ·VD · 1 −

·V

2

IQ D

e

IDS2 = IQ − IDS1

M

a

Y, por tanto,

d

Con lo que:

la

lu

.e

te

s

n

se

s

p

2β 2

·V

VO = R· (IDS1 − IDS2 ) = 2·R· 2βIQ ·VD · 1 −

IQ D

de

Es posible ver que estas funciones alcanzan máximos/mínimos en

VD =

(15)

q

± √12 ·

IQ

2β

=

± 12

q

IQ

. A

β

os

partir de ese instante, las ecuaciones dejan de tener validez al pasar uno de los transistores a zona

p

m

alu

m

a

d

n

de corte. Por otra parte, debe garantizarse que los transistores no abandonen la zona de saturación.

o

Grácamente, la relación entrada-salida es muy similar a la de un par bipolar pero aparece una

IQ pero, en los pares FET, a

−1/2

IQ . En general, este hecho redunda en una menor capacidad amplicadora de los pares FET.

.u

VD

sea muy pequeña, Eq. 15 se puede transformar en:

w

id

so

En el hipotético caso de que la tensión

c

m

de

C

curiosa diferencia. En el par bipolar, la ganancia era proporcional a

w

w

/

e

rs

iv

Pa

ra

u

s

p

p

2β 2

2β 2

VO = 2·R· 2βIQ ·VD · 1 −

·V ' 2·R· 2βIQ ·VD · 1 −

·V

IQ D

IQ D

:/

n

De lo que se deduce que, en torno al origen, la ganancia es

p

2·R· 2βIQ .

(16)

Este parámetro también

tt

p

U

se podría haber deducido a partir del modelo en pequeña señal de los transistores, que se muestra

en Fig. 9. Se ha incluido en este dispositivo la acción del efecto sustrato que, sin embargo, está

h

restringido a transistores MOSFET con el sustrato unido a una tensión constante.

En este circuito, se va a cumplir que:

Electrónica Analógica

Ingeniería Superior en Electrónica

11

Amplicadores de Entrada Diferencial

Tema 5

Figura 9: Equivalente en pequeña señal de un par diferencial FET con resistencias de carga. Se

vD .

M

a

e

lu

.e

te

s

n

se

d

vgsA = vD − vs

vgsB = −vD − vs

vbsA = vbsB = −vs

vO = R· (idsA − idsB )

idsA = gm ·vgsA − gmb ·vbsA

idsB = gm ·vgsB − gmb ·vbsB

d

ri

d

entiende que la excitación en pequeña señal es la componente diferencial,

de

la

Al combinar estas ecuaciones, se llega a la conclusión de que:

(17)

p

os

vO = 2·R·gm ·vD

m

alu

m

a

d

n

El efecto sustrato, si existiera, desaparece al ser la conguración de los

qtransistores similar. Esta

p

√

I

gm = 2· β·ID = 2· β· 2Q = 2·β·IQ .

c

m

C

o

ecuación es similar a la obtenida por Eq. 16 porque

.u

w

so

de

2.2. No idealidades en un par diferencial

w

w

id

Pa

ra

u

Aprovechando que ya se ha explicado el comportamiento de un par diferencial con carga resistiva,

e

rs

es un buen momento para conocer las no idealidades asociadas pues pueden extenderse con facilidad

/

:/

iv

a cualquier otro amplicador diferencial, como los amplicadores operacionales.

tt

p

U

n

2.2.1. Corriente de polarización de la entrada

h

Este es un parámetro DC. En otras palabras, interviene en el cálculo del punto de operación.

Cualquier fuente de tensión aplicada a la entrada debe ser capaz de proporcionar esta corriente de

entrada. Si hubiera una resistencia en serie con esta entrada, se producirá una caída de tensión entre

sus extremos.

En el caso del par bipolar, la corriente que atraviesa el emisor de cada amplicador es

de lo que se deduce que la corriente de base de cada transistor es

IB =

IE

βF +1

IE = 21 ·IQ

I

= 12 · βFQ+1 .

Así, si

el par estuviese polarizado por una fuente de 0.1 mA y con transistores NPN de ganancia 100, la

corriente de base, que coincide con la corriente de polarización en la entrada, sería de 1

Electrónica Analógica

Ingeniería Superior en Electrónica

µA.

En

12

Amplicadores de Entrada Diferencial

Tema 5

general, se suele tomar como positiva si entra en el amplicador diferencial y negativa si sale. Así,

si el par fuera PNP, la corriente sería negativa pues sale de las bases del transistor.

Si el transistor fuera de efecto campo, la corriente de polarización sería prácticamente nula ya

que se está atacando la puerta de un transistor.

Por otra parte, pequeños desapareamientos entre parámetros conducen a dos valores distintos

de

IB

en cada una de las entradas.

Para disminuir la corriente de polarización de la entrada, puede optarse por distintas estrategias.

En algunos casos, se utiliza un par Darlington o CC-CE reemplazando al transistor del par diferencial.

Al comportarse como transistores con una ganancia del orden de

h2F E ,

ese parámetro disminuye

d

ri

d

aunque, lamentablemente, se introduce una penalización en frecuencia. Otra opción, más habitual,

consiste en crear una fuente de corriente que inyecte en el terminal de entrada la corriente que necesite

M

a

la base del transistor. Esta estrategia, que requiere del uso de varios transistores perfectamente

calibrados, tiene la ventaja de que no actúa sobre la velocidad de respuesta del dispositivo.

d

e

2.2.2. Tensión de oset

lu

.e

te

s

n

se

Como el anterior, es un parámetro DC. Idealmente, si se aplica la misma tensión a las entradas

la

de un par diferencial, la salida debería ser nula pero, en la práctica, dista de ser así. El origen de esto

de

radica en la existencia de asimetrías dentro del par diferencial. Así, por ejemplo, si las resistencias

que aparecen en Eq. 10 fuesen distintas, y no iguales como se supuso, la tensión de salida sería

p

m

alu

m

a

d

n

os

distinta de 0 si las corrientes fueran iguales.

Se dene tensión de oset de la salida,

VOS,O

como el valor de la tensión de salida con entrada

c

m

C

o

nula. Obviamente, también puede realizarse una denición análoga cuando la salida es en modo

corriente, como veremos en el caso del par diferencial con carga activa.

AD , se dene Tensión de oset de la entrada, VOS,I

VOS,O

. En pares diferenciales, da lo mismo con qué tipo de oset estemos trabajando pero, en

como

AD

.u

w

id

so

de

Si el par diferencial tiene una ganancia

w

w

e

rs

Pa

ra

u

dispositivos más complejos, como son los amplicadores operacionales, se utiliza preferentemente la

tensión de oset de la entrada, que es independiente de la ganancia DC del sistema completo, cuya

/

iv

ganancia puede jarse por realimentación.

:/

U

n

Por otra parte, las asimetrías en la construcción no solo conducen a la aparición de una tensión

tt

p

de oset. Así, también son las responsables de la aparición de una ganancia del modo común no

CM RR.

h

nula, que lleva a un descenso en el valor de

2.2.3. Corriente máxima de salida

Es la máxima corriente que puede proporcionar una par diferencial. Obviamente, está limitada por

la corriente de polarización del circuito,

IQ ,

aunque, en la práctica, es menor ya que los transistores

del par diferencial habrían abandonado la zona activa directa.

Electrónica Analógica

Ingeniería Superior en Electrónica

13

Amplicadores de Entrada Diferencial

Tema 5

2.2.4. Impedancia de entrada y salida

Estos parámetros son válidos para modelos en pequeña señal y jamás debe utilizarse en modo

DC. Para esto último, ya están las corrientes de polarización de la entrada así como la corriente

en cortocircuito. Se utiliza, por ejemplo, para calcular los polos y ceros del sistema completo. En

general, la valor de la impedancia de entrada es del orden de

hie

en transistores bipolares y de la

capacidad de puerta en los transistores de efecto campo. La de salida debe calcularse realizando el

modelo Thévenin del par visto desde los terminales de salida aunque, por lo general, serán del orden

de la resistencia de carga en paralelo con la impedancia de salida de los transistores.

d

ri

d

2.2.5. Frecuencia máxima de trabajo

M

a

Recordemos que, dentro de cada par diferencial, hay varias capacidades. En general, se puede

suponer que ambos transistores están en una situación similar a la del emisor común y que los

lu

.e

te

s

n

se

2.3. Pares diferenciales con carga activa

d

e

resultados obtenidos allí son extrapolables a esta nueva estructura.

la

Estos pares se caracterizan por utilizar las dos ramas de un espejo de corriente como cargas de los

de

dos transistores del par diferencial. En general, estos dispositivos se diseñan como transconductores,

os

que convierten la tensión de entrada en corriente de salida, tienen una ganancia extraordinariamente

p

m

alu

m

a

d

n

alta y no requieren de grandes valores de resistencia para obtener una ganancia muy alta. Por ello, son

o

muy populares al diseñar circuitos integrados como amplicadores operacionales o comparadores.

c

m

C

Por otro lado, cuanto más ecaz sea la reexión de corriente del espejo y cuanto mayor sea su

w

w

w

id

Pa

ra

u

so

2.3.1. Tecnología bipolar

.u

de

impedancia de salida, mejores características tendrá el par diferencial.

e

rs

En esta tecnología, el par diferencial más sencillo construido íntegramente con transistores bipo-

/

iv

lares es el mostrado en Fig. 10. En ella, el par diferencial NPN es polarizado con un espejo de

n

:/

corriente simple de caracter opuesto (PNP). La salida, simple, se encuentra en el terminal formado

tt

p

U

por los dos conectores en serie.

Es preferible estudiar esta estructura como un transconductor. Para darle mayor generalidad,

h

supondremos que hay dos fuentes de corriente polarizando cada transistor, estando relacionadas

k = 1 − ≈ 1 ⇒ & 0 (Fig. 11). Esto nos permite extrapolar los resultados a

cualquier espejo distinto del simple cambiando, simplemente, el valor de . En un espejo simple PNP,

−4

este parámetro es 0.02 pero, en espejos más complejos, es del orden de 10 . En esta estructura es

entre sí por un factor

fácil ver que:

IEa = IS · exp

Electrónica Analógica

IEa + IEb = IQ

VB − VE

VA − VE

IEb = IS · exp

N ·VT

N ·VT

Ingeniería Superior en Electrónica

14

Amplicadores de Entrada Diferencial

Tema 5

os

de

la

lu

.e

te

s

n

se

d

e

M

a

d

ri

d

Figura 10: Par diferencial NPN con carga activa simple y salida en corriente. La tensión diferencial

1

amplicada es vD =

(VA − VB ).

2

p

m

alu

m

a

d

n

Figura 11: Par diferencial NPN con carga activa generalizada.

ICb = αF ·IEb = k·IA − IO

c

m

C

o

ICa = αF ·IEa = IA

.u

w

vD

VC − VE

· exp

ICa = αF ·IS · exp

N ·VT

N ·VT

VC − VE

vD

ICb = αF ·IS · exp

· exp −

N ·VT

N ·VT

w

w

tt

p

:/

/

e

rs

id

so

U

n

iv

Pa

ra

u

que:

de

VE la tensión del nudo donde se conectan los dos emisores. Suponiendo que VA = VC +vD

y VB = VC −vD (siendo VC la tensión común y no la de ninguno de los colectores), puede demostrarse

Siendo

h

Combinando con el resto de ecuaciones, se demuestra que:

IEa + IEb = IS · exp

VC − VE

N ·VT

⇒ IS · exp

Electrónica Analógica

vD

vD

· exp

+ exp −

= IQ ⇒

N ·VT

N ·VT

VC − VE

N ·VT

=

I

1

Q

2 cosh vD

N ·VT

Ingeniería Superior en Electrónica

15

Amplicadores de Entrada Diferencial

Tema 5

d

ri

d

Figura 12: Par diferencial NMOS con carga activa simple y salida en corriente.

− ·αF ·IQ ·

1

1 + exp − N2·v·VDT

(18)

d

e

IO = αF ·IQ · tanh

vD

N ·VT

M

a

A partir de esta expresión, no es difícil demostrar que

salida no lo es!. En efecto,

lu

.e

te

s

n

se

Expresión que proporciona unos datos curiosos. En primer lugar, si la tensión aplicada es nula, ½la

de

la

1

IO (0) = − ·αF ·IQ

2

(19)

Este hecho es lógico pues la reexión no es perfecta en un espejo de corriente y, por tanto, aparecen

p

m

alu

m

a

d

n

os

asimetrías en el circuito incluso cuando los dispositivos son idénticos. Por otra parte, es fácil ver

id

c

m

1

.u

so

α ·I

≈ F Q

− ·αF ·IQ ·

N ·VT

1 + exp − N2·v·VDT

w

de

IO = αF ·IQ · tanh

vD

N ·VT

C

o

que, en torno al punto de operación, se cumple que:

w

w

e

rs

Pa

ra

u

de lo que se deduce que la ganancia del par es del orden de

1

1

1 − · ·vD − ·αF ·IQ

2

2

αF ·IQ

. En caso de afrontar el problema

N ·VT

tomando como punto de partida los modelos en pequeña señal, se deduciría que ésta es, más o menos,

:/

n

envueltos en el problema.

/

iv

la ganancia en pequeña señal aunque habría que incluir los equivalentes de todos los transistores

tt

p

U

¾Y cuanto sería la ganancia en tensión? Simplemente, habría que multiplicar la trasconductancia

por el valor de la resistencia de carga. Si ésta no estuviera o fuera muy grande, habría que tener

h

en cuenta el paralelo formado por la impedancia de salida del espejo de corriente y el transistor B.

Lógicamente, cuanto mayor sean, mayor es la ganancia en tensión del par diferencial.

2.3.2. Tecnología CMOS/JFET

La construcción de esta estructura es similar a la de Fig. 10 con la salvedad de que los NPN se

reemplazan por NMOS y los PNP por PMOS (Fig. 12). El modelo idealizado es similar al de Fig.

Electrónica Analógica

Ingeniería Superior en Electrónica

16

Amplicadores de Entrada Diferencial

Tema 5

11, reemplazando los transistores NPN por NMOS. Es fácil ver que, en esta estructura:

IA · (1 + k) = IQ + IO

IDa = β· (VGSa − VT H )2 = β· (VC + vD − VS − VT H )2 = IA

IDb = β· (VGSb − VT H )2 = β· (VC − vD − VS − VT H )2 = k·IA − IO

VT H

común y VS

Siendo

la tensión umbral de los transistores,

β

la trasconductancia,

VC

la tensión del modo

la tensión del nudo común a los dos terminales de fuente. Estas dos últimas ecuaciones

d

ri

d

puede combinarse para obtener:

M

a

p

p

p

p

p

p

p

IA − β·vD = k·IA − IO + β·vD ⇒ IA − k·IA − IO = 2· β·vD

Elevando ambos miembros al cuadrado:

lu

.e

te

s

n

se

d

e

√ √

2

⇒

IA + k·IA − IO −2 IA · k·IA − IO = 4·β·vD

{z

}

|

IQ

k·IA − IO = IQ − IA

p

y desarrollando el segundo término:

os

Recordando que

de

la

p p

2

2 2

IQ − 2 IA · k·IA − IO = 4·β·vD

⇒ 4·IA · (k·IA − IO ) = IQ − 4·β·vD

m

c

m

8

=

s

p

1

2·β· 2

= IQ ± 2·β·IQ ·vD · 1 −

v

2

IQ D

:/

/

w

w

id

IA =

4

2

16·IQ2 − 16·IQ2 − 162 ·β 2 ·vD

+ 32·β·IQ ·vD

.u

q

w

4·IQ ±

e

rs

so

n

iv

Pa

ra

u

o

C

IA :

de

Despejando

alu

m

a

d

n

4

2

4·IA2 − 4·IQ ·IA + IQ2 + 16·β 2 ·vD

− 8·β·IQ ·vD

=0

tt

p

U

En principio, debemos descartar una de las dos soluciones. Como la corriente aumenta con la tensión

diferencial, descartamos la solución con signo menos. El radical alcanza un máximo en

h

resultando, obviamente,

IQ = IA .

q

I

vD = 21 · βQ

A partir de este instante, la ecuación anterior deja de ser válida

y la salida se hace constante. Para deducir la corriente de salida:

IO = (k + 1) ·IA − IQ = (2·IA − IQ ) − ·IA =

s

p

2·β· 2

v − ·

= 2 2·β·IQ ·vD · 1 −

IQ D

Electrónica Analógica

s

!

p

1

2·β· 2

IQ + 2·β·IQ ·vD · 1 −

v

2

IQ D

Ingeniería Superior en Electrónica

(20)

17

Amplicadores de Entrada Diferencial

Tema 5

Suponiendo que el valor de la tensión diferencial es muy bajo, se puede realizar la siguiente aproximación:

p

1

1

IO ≈ 2 2·β·IQ 1 − ·vD − ·IQ

2

2

(21)

Esto indica que, en primer lugar, la salida no es nula con entrada nula. En otras palabras, hay un

oset en la corriente de salida de valor

− 12 ·IQ .

Por otro lado, la ganancia en pequeña señal es del

p

orden de 2

2·β·IQ . Sin embargo, en la práctica, el resultado puede verse alterado ya que se supuso

inicialmente que la tensión umbral de los transistores era constante. Esto no es cierto salvo que la

fuente y el sustrato estén cortocircuitados. El valor exacto de la ganancia puede realizarse a partir de

d

los modelos en pequeña señal de los transistores, que sí toman en cuenta este fenómeno. Asimismo,

p

√

gm = 2· β·ID = 2·β·IQ .

común pues VS diere de VC

e

La primera parte de esta expresión es equivalente a Eq. 21 ya que

M

a

io = (2 − ) ·gm ·vD + · (gm + gmb ) ·vS

d

ri

se aprecia la aparición de una dependencia del modo común pues:

d

segunda parte, en cambio está relacionada con la tensión del modo

La

en

lu

.e

te

s

n

se

una tensión más o menos constante del orden de la tensión umbral. Evidentemente, cuanto mejor

la

sea la capacidad de reexión del dispositivo, menor será la inuencia del efecto sustrato.

de

Esto nos lleva a una importante conclusión: Las asimetrías estropean las características de los

pares diferenciales con carga activa. Más aún, todos los parámetros descritos en el apartado 2.2,

p

m

alu

m

a

d

n

con carga activa.

os

que originalmente se centraban en los pares con cargas resistivas, tienen su equivalente en los pares

c

m

C

o

Por otra parte, la ganancia en tensión del par diferencial se calcularía multiplicando la transconductancia por la resistencia de carga. Si ésta no existiera o fuera muy alta, habría que multiplicarla

.u

de

por la impedancia de salida del transconductor. Esta impedancia se calcularía poniendo en paralelo

w

id

so

la resistencia de salida del espejo de corriente, calculada con una corriente de salida igual a

2

h−1

oe = λ·IQ .

p

proporcional a

IQ y la

w

w

e

rs

Pa

ra

u

y la del transistor que forma el par diferencial, que será del orden de

a un interesantísimo resultado pues la trasconductancia es

1

·I ,

2 Q

Esto nos lleva

impedancia de

n

p

IQ .

/

proporcional a

Debe notarse la diferencia con los transistores bipolares en los que, al ser la

:/

iv

−1

salida a IQ con lo que, en ausencia de resistencia de carga, la ganancia en tensión es inversamente

tt

p

U

transconductancia y la resistencia de carga directa e inversamente proporcionales a

IQ ,

se produce

h

una cancelación de parámetros que nos llevaría a concluir que la ganancia en tensión de un par

diferencial bipolar con carga activa es, más o menos, independiente de la corriente de polarización.

Finalmente, los resultados descritos en este apartado son perfectamente aplicables a los transistores JFET con la evidente salvedad de que no existe efecto sustrato y, por otro lado, al ser propios

de tecnologías bipolares, los espejos de corrientes se construyen con BJTs o, en algunos casos, se

usan como cargas JFETs con puerta y drenador cortocircuitados.

Electrónica Analógica

Ingeniería Superior en Electrónica

18

Amplicadores de Entrada Diferencial

Tema 5

(a)

(b)

(c)

(d)

(e)

d

Figura 13: Técnicas para aumentar la impedancia de salida de un par diferencial en tecnología

d

ri

bipolar: Uso de un espejo cascode (a), Wilson (b), con degeneración de emisor simple (c) y de base

m

alu

m

a

d

n

os

(a)

p

de

la

lu

.e

te

s

n

se

d

e

M

a

compensada (d). Estas técnicas también pueden utilizarse en pares JFET (e).

(b)

(c)

Figura 14: Técnicas para aumentar la impedancia de salida de un par diferencial en tecnología CMOS:

c

m

C

o

Uso de un espejo Wilson (a), cascode autopolarizado (b) y cascode con polarización externa (c).

.u

de

2.3.3. Mejoras de los pares diferenciales con carga activa

w

id

so

Básicamente, las mejoras que se pueden introducir a estos pares consisten en el uso de espejos

w

w

/

iv

del par.

e

rs

Pa

ra

u

de corriente con una mayor impedancia de salida y en el aumento articial de la impedancia de salida

:/

n

En tecnologías bipolares, podría recurrirse a la utilización de espejos Wilson y cascode para

tt

p

U

aumentar la impedancia de salida del espejo (Fig. 13a-b). Sin embargo, es más habitual utilizar

espejos con degeneración de emisor (Fig. 13c) que se transforman con la ayuda de un transistor

factor

h

adicional en un espejo con base compensada (Fig. 13d). Este espejo tiene la ventaja de minimizar el

de Eq. 19. Es posible aplicar estas soluciones a pares basados en transistores JFET, como

se muestra en Fig. 13e.

En tecnologías CMOS, se suele recurrir, simplemente, a la utilización de espejos Wilson o cascode,

bien autopolarizados, bien polarizados externamente (Fig. 14). Debe tenerse en cuenta que, en estos

casos, puede aumentarse también la impedancia de salida de los transistores del par diferencial

CMOS añadiendo otro par de transistores cascode entre la salida y el par diferencial, polarizados

con otra tensión

VY , VY < VX .

Electrónica Analógica

Ingeniería Superior en Electrónica

19

Amplicadores de Entrada Diferencial

Tema 5

d

Figura 15: Par diferencial con salida y entrada inversoras cortocircuitadas para crear un sencillo

d

ri

seguidor de tensión.

M

a

2.3.4. Uso de pares diferenciales como amplicadores operacionales

En tecnologías CMOS, se ha visto que la mayor parte de los dispositivos amplicadores tienen su

d

e

entrada a través de la puerta de algún tipo de transistor MOS. Por tanto, en estas circunstancias,

lu

.e

te

s

n

se

la corriente de entrada es nula y cualquier amplicador, incluso aquellos que apenas pueden proporcionar unos microamperios de corriente de salida, es capaz de atacar exitosamente nuevos bloques

la

amplicadores.

de

Así, los pares diferenciales en tecnología CMOS pueden ser utilizados en determinadas circun-

p

os

stancias como amplicadores operacionales siempre y cuando no deban proporcionar corriente de

m

alu

m

a

d

n

salida. Por ejemplo, recordemos que en el tema anterior se trató el amplicador cascode activo.

o

En general, el amplicador operacional se podía construir como un simple par diferencial ya que

c

m

C

se atacaba directamente la puerta de un MOS. Ejemplos similares se pueden encontrar al construir

.u

de

etapas de salida (Próximo tema) o al construir circuitos S/H y ltros conmutados, que se verán

someramente en el último tema.

w

id

Pa

ra

u

so

Fig. 15 muestra un ejemplo de como se puede conseguir un seguidor de tensión a partir de un

w

w

e

rs

par diferencial. Con apenas 5 transistores MOS (2 del par, 2 de la carga activa y 1 que sería la

4

pues podrían degradar la salida por lo que debemos limitarnos a estructura

:/

n

salida con resistencias

/

iv

corriente de polarización) se ha creado un seguidor de tensión. Evidentemente, es peligroso cargar la

tt

p

U

con ganancia unidad. Sin embargo, esto es más que suciente para muchos casos.

En tecnologías bipolares esta solución no es común. Sería necesario colocar una etapa de salida

h

pues, en general, la impedancia de entrada de las etapas bipolares es relativamente baja. Y esto

signica espacio consumido por lo que estas estructuras solo tienen cabida en algunos dispositivos

muy complejos y voluminosos.

4 Que, por otra parte, son difíciles de integrar en tecnologías CMOS y ocupan mucho espacio.

Electrónica Analógica

Ingeniería Superior en Electrónica

20