Reválida de Septiembre - Universitat de les Illes Balears

Anuncio

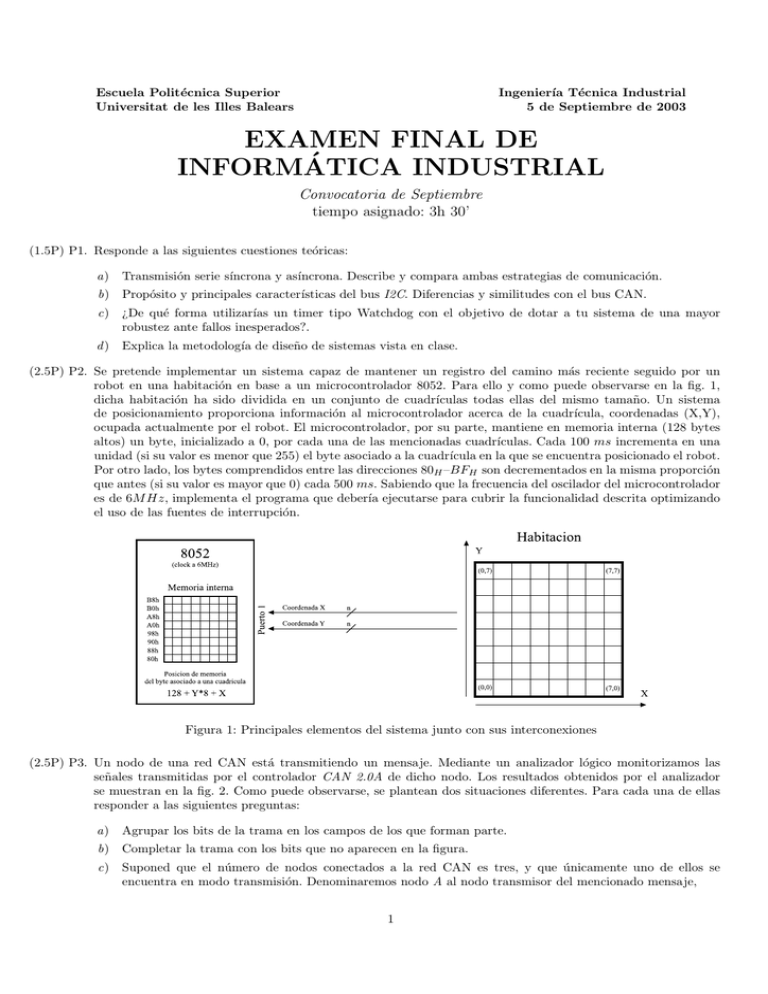

Escuela Politécnica Superior Universitat de les Illes Balears Ingenierı́a Técnica Industrial 5 de Septiembre de 2003 EXAMEN FINAL DE INFORMÁTICA INDUSTRIAL Convocatoria de Septiembre tiempo asignado: 3h 30’ (1.5P) P1. Responde a las siguientes cuestiones teóricas: a) Transmisión serie sı́ncrona y ası́ncrona. Describe y compara ambas estrategias de comunicación. b) Propósito y principales caracterı́sticas del bus I2C. Diferencias y similitudes con el bus CAN. c) ¿De qué forma utilizarı́as un timer tipo Watchdog con el objetivo de dotar a tu sistema de una mayor robustez ante fallos inesperados?. d ) Explica la metodologı́a de diseño de sistemas vista en clase. (2.5P) P2. Se pretende implementar un sistema capaz de mantener un registro del camino más reciente seguido por un robot en una habitación en base a un microcontrolador 8052. Para ello y como puede observarse en la fig. 1, dicha habitación ha sido dividida en un conjunto de cuadrı́culas todas ellas del mismo tamaño. Un sistema de posicionamiento proporciona información al microcontrolador acerca de la cuadrı́cula, coordenadas (X,Y), ocupada actualmente por el robot. El microcontrolador, por su parte, mantiene en memoria interna (128 bytes altos) un byte, inicializado a 0, por cada una de las mencionadas cuadrı́culas. Cada 100 ms incrementa en una unidad (si su valor es menor que 255) el byte asociado a la cuadrı́cula en la que se encuentra posicionado el robot. Por otro lado, los bytes comprendidos entre las direcciones 80H –BFH son decrementados en la misma proporción que antes (si su valor es mayor que 0) cada 500 ms. Sabiendo que la frecuencia del oscilador del microcontrolador es de 6M Hz, implementa el programa que deberı́a ejecutarse para cubrir la funcionalidad descrita optimizando el uso de las fuentes de interrupción. Figura 1: Principales elementos del sistema junto con sus interconexiones (2.5P) P3. Un nodo de una red CAN está transmitiendo un mensaje. Mediante un analizador lógico monitorizamos las señales transmitidas por el controlador CAN 2.0A de dicho nodo. Los resultados obtenidos por el analizador se muestran en la fig. 2. Como puede observarse, se plantean dos situaciones diferentes. Para cada una de ellas responder a las siguientes preguntas: a) Agrupar los bits de la trama en los campos de los que forman parte. b) Completar la trama con los bits que no aparecen en la figura. c) Suponed que el número de nodos conectados a la red CAN es tres, y que únicamente uno de ellos se encuentra en modo transmisión. Denominaremos nodo A al nodo transmisor del mencionado mensaje, 1 Examen Final de Septiembre Informática Industrial haciendo referencia a los receptores del mismo como nodos B y C. Explicar con detalle el proceso de detección y tratamiento para las situaciones de error marcadas con un asterisco en la fig. 2. El error se origina en cada caso por motivos diferentes: 1) 2) Se produce un fallo en la recepción: el nodo C recibe del bus un bit recesivo en lugar de un bit dominante. Se produce un fallo de monitorización: el nodo A recibe del bus un bit dominante en lugar de un bit recesivo. Debéis indicar el tipo de error que detectará cada uno de los nodos. Hacer especial hincapié en la estructura y el instante de generación de las tramas de error. Figura 2: Resultados de la monitorización de la transmisión de un nodo de una red CAN (2P) P4. Un computador tiene una memoria principal de 32K palabras de 16 bits. Dispone a su vez de una cache de 4K palabras dividida en conjuntos de 4 lı́neas con 64 palabras por lı́nea. En un momento dado, el procesador accede en modo lectura y en el orden especificado a las siguientes posiciones de memoria 0, 1, 2, 3, . . . , 4.351. La secuencia de acceso se repite posteriormente 8 veces más. Suponiendo que la cache se encuentra inicialmente vacı́a y que la polı́tica de sustitución de bloques es LRU, calcular su tasa de aciertos H para la situación descrita. (1.5P) P5. La fig. 3 muestra la jerarquı́a de memoria de un determinado computador. Según sus especificaciones, cuando se referencia una palabra que se encuentra en la cache se requieren 20 ns para acceder a ella. Las penalizaciones de fallo1 y las tasas de acierto en memoria cache y memoria principal son, respectivamente, 10 µs — 80 % y 5 ms — 90 %. ¿Cuál es, en nanosegundos, el tiempo medio necesario para acceder a una palabra en este sistema?. Figura 3: Jerarquı́a de memoria de tres niveles 1 Notar que en este caso las penalizaciones de fallo son relativas al nivel inmediatamente inferior. 2

![curso-can-bus-modelo-capas-propiedades-conceptos-protocolos-can-tramas-errores-implementacion-sistema-transmision[1]](http://s2.studylib.es/store/data/008895045_1-9680d208d05be4b1ead704cd6ab707b5-300x300.png)