Enunciats de problemes (Part 2) Segmentació i Paral·lelisme

Anuncio

Enunciats de problemes (Part 2)

Segmentació i Paral·lelisme:

Arquitectura dels Microprocessadors Actuals

Professors:

Eduard Ayguadé

Josep Llosa

Departament d’Arquitectura de Computadors

Curs 2006-07

1

Problema 1

Sean las siguientes secuencias de código:

mov $6, #100

ld F1, b($3)

bucle: ld F2, a($2)

add.f F1, F1, F2

mul.f F1, F1, F7

add $2, $2, #1

st b($2), F1

sub $6, $6, #1

bnz bucle

mov $6, #100

bucle: ld F1, a($4)

ld F2, b($4)

add.f F3, F1, F2

st c($4), F3

add $4, $4, #1

sub $6, $6, #1

bnz bucle

donde .f indica que las instrucciones operan con operandos en formato punto flotante.

Suponer un procesador superescalar con las características siguientes:

•

ancho 2 con el mecanismo de Tomasulo, que nunca bloquea la búsqueda de instrucciones

porque suponemos ilimitado el número de estaciones de reserva. El procesador busca dos

instrucciones por ciclo (alineadas tal como indican las líneas) y es capaz de finalizar la

ejecución y escribir resultados de dos instrucciones por ciclo (commit en orden).

•

tiene una unidad funcional (UF) de suma en coma flotante y una UF de multiplicación en

coma flotante. Ambas están no segmentadas y sus latencias son 12 y 15 ciclos,

respectivamente. La aritmética entera se realiza en otra UF con latencia 1.

•

para acceder a memoria se dispone de un puerto, con una latencia de 1 ciclo para el cálculo

de la dirección efectiva y un ciclo para el acceso a memoria.

•

suponer que el procesador dispone de predicción de saltos ideal.

Se pide: Indicar para cada secuencia de código si la segmentación de las unidades funcionales reduciría

el tiempo de ejecución de la misma.

Problema 2

Sigui el següent programa:

for ( i = 1; i <= n ; i++) {

if (a[i] ≠ 0) then x[i] = y[i] / a[i];

}

i la seva traducció a llenguatge màquina per un processador superescalar:

mov $10, #0

mov $11, #n

for: ld F0, a($10)

beq.f F0, #0, fin

ld.f F1, y($10)

div.f F2, F1, F0

st.f x($10), F2

fin: add $10, $10, #8

sub $11,$11, #1

bneq $11, #0, for

;

;

;

;

;

;

;

;

;

;

$10 ← 0

$11 ← n

F0 ← M[a + $10]

si F0 = 0 llavors salta a fin

F1 ← M[y + $10]

F2 ← F1 / F0

M[x + $10] ← F2

$10 ← $10 + 8

$11 ← $11 - 1

si $11 <> 0 llavors salta a for

L’arquitectura del processador superescalar es la següent:

•

Processador capaç d’iniciar l’execució de dues instruccions noves cada cicle. Unitats

funcionals disponibles: 1 entera, 1 d’aritmètica real, 1 de memòria i 1 de salts. Segmentació

amb 7 etapes (FDIEMWC) excepte les d’aritmètica real que en tenen 6 (FDIEWC).

2

•

Memòria ideal (sempre fa hit i latència 1 cicle); Unitat entera amb latència 1 cicle; Unitat real

segmentada amb latència 5 cicles; unitat de salts resol el salt al final de l’etapa ALU.

• Predictor de salts basat amb comptador saturat de 2 bits; inicialment val zero (si el bit de

més pes val zero, llavors la predicció es no saltar). La predicció es fa a l’etapa de fetch.

Es demana:

a) Si de les n iteracions del bucle, només les 4 primeres compleixen la condició a[i] ≠ 0, calcula la

probabilitat d’encert del predictor de salt per cadascun dels salts del programa.

b) Temps d’execució del programa que executa n=64 iteracions.

Problema 3

Considerad un procesador superescalar de grado 4 con las siguientes características:

- Etapas de la segmentación:

o FDIE…EWC para las arítméticas, siendo el número de ciclos de ejecución (E)

dependiente del tipo de instrucción (1 ciclo para las enteras y 4 ciclos para las

operaciones de punto flotante).

o FDIEMWC para las de memoria, tardando un ciclo de ejecución para el cálculo de la

dirección de memoria y 1 ciclo para el acceso a la memoria (que se considerará

ideal).

o FDIEWC para las de salto, para las que supondremos predicción de saltos ideal (es

decir, después de la etapa F siempre se sabe la dirección de la siguiente instrucción

a ejecutar).

- Unidades funcionales: 1 de aritmética entera, 1 de aritmética en punto flotante (segmentada)

y 1 de saltos.

- Puertos de acceso a memoria: 2 puertos bidireccionales con los correspondientes

sumadores para el cálculo de direcciones. En las instrucciones de store, el cálculo de la

dirección se realiza tan pronto como se tenga el valor del registro que se utiliza para calcular

la dirección, quedando la instrucción almacenada en un buffer de escrituras a memoria en

caso de no disponer del dato a escribir.

- Infinitas estaciones de reserva e infinitos registros para realizar el renombre.

- Permite hacer 4 writes (W) y 4 commits (C) por ciclo, realizándose los C en el mismo orden

que se había hecho el correspondiente decode (D).

Dado el siguiente fragmento de código en alto nivel:

for (i=1; i<=max; i++) y[i] = a[i] + y[i] * x ;

y su traducción a lenguaje máquina (observación: las líneas en el código indican líneas de cache, los

registros $0, $1 y F3 están inicializados con anterioridad):

bucle:

ld F1, y($0)

ld F2, a($0)

mul.f F1, F1, F3 ; F3 contiene el valor de x

add.f F1, F1, F2

st F1, y($0)

add $0, $0, 8

sub $1, $1, 1

jnz bucle

Se pide:

a) ¿Cual sería el factor de proporcionalidad que multiplica al número de iteraciones (max) en la

expresión que determina el tiempo de de ejecución del bucle? Para ello dibujar el cronograma de

ejecución

b) En régimen permanente, ¿Cuántos registros de renombre se consumen y liberan por ciclo? Para ello

dibujar en el cronograma anterior los ciclos en que se consumen/liberar registros de renombre.

3

c) Si la arquitectura tuviera 32 registros de renombre, ¿en que iteración del bucle se satura este recurso?

A partir de este momento, cual seria el factor de proporcionalidad que multiplica al número de iteraciones

(max) en la expresión que determina el tiempo de de ejecución del bucle?

Problema 4

Dado un procesador vectorial con las siguientes características:

•

•

8 registros vectoriales (V0-V7) de 128 elementos (MVL=128)

1 sumador y 3 multiplicadores, todas las unidades funcionales tienen un tiempo de arranque

de 10 ciclos.

• 1 puerto de acceso a memoria bidireccional, todas las operaciones de acceso a memoria

tienen un tiempo de arranque de 15 ciclos.

• La unidad de control permite lanzar una instrucción por ciclo.

• Una instrucción no se puede lanzar si otra instrucción anterior está bloqueada debido a un

riesgo estructural o de datos.

Queremos analizar su comportamiento al ejecutar el código máquina vectorial correspondiente a:

do i=1, 128

x(i) = y(i) *(s*x(i)+t*z(i))

enddo

Suponed que los vectores de datos x, y, z están inicialmente en memoria (las direcciones de base están

en los registros $x, $y y $z), que al final debe quedar en memoria el vector resultado x, y que los

escalares s y t están en los registros $s y $t.

Proponed el código máquina vectorial más eficiente que encontréis, y calculad el tiempo de ejecución

(dibujar cronograma) para cada uno de los casos que se describen a continuación.

a) Se permite el encadenamiento de un máximo de dos instrucciones sucesivas. Los registros

disponen de un puerto de acceso bidireccional.

b) Lo mismo que el apartado a), pero además se pueden encadenar cualquier número de

instrucciones dependientes sucesivas. Los registros incorporan dos puertos independientes de

lectura y escritura.

c) Lo mismo que el apartado b), pero además se añade un segundo puerto a memoria.

Problema 5

Donat el següent programa i la seva traducció a llenguatge màquina per un processador escalar i un

processador vectorial:

for ( i = 1; i <= n ; i++) {

if (a[i] ≠ 0) then x[j] = y[i] / a[i];

}

4

CODIGO ESCALAR

mov $1, n

mov $2, @a

mov $3, @x

mov $4, @y

bucle:

ld.f F1, 0($2)

beq.f F1, fin

ld.f F2, 0($3)

div.f F3, F2, F1

st.f F3, 0($4)

fin:

add $2, $2, #8

add $3, $3, #8

add $4, $4, #8

sub $1, $1, #1

bne $1, bucle

CODIGO VECTORIAL

mov $2, @A

mov $3, @X

mov $4, @Y

ld.v V1, 0($2)

sne.v V1, #0

ld.v V2, 0($3)

ld.v V3, 0($4)

div.v V3, V2, V1

st.v V3, 0($4)

cvm

Considereu dues arquitectures alternatives:

•

Processador superescalar capaç d’iniciar l’execució de dues instruccions per cicle amb una

unitat funcional entera (latència 1 cicle), una unitat funcional de punt flotant (latència 10

cicles, segmentada) i dos unitats d’accés a memòria (latència 1 cicle). El processador

incorpora predicció de salts i implementa salt amb anul·lació en cas de fer una predicció

incorrecte.

• Processador vectorial amb una unitat vectorial de propòsit general (suma, comparació, ...,

temps d’arrancada de 4 cicles), una unitat vectorial per fer la divisió (temps d’arrancada de

10 cicles) i dos ports d’accés a memòria (temps d’arrancada de 4 cicles). La longitud

vectorial màxima es de 64. S’incorporen tots els encadenaments necessaris i els registres

vectorials tenen ports de lectura i escriptura independents. El processador escalar es igual al

de l’arquitectura anterior i es capaç d’iniciar l’execució de dues instruccions escalars per

cicle, o una escalar i una vectorial per cicle.

Es demana:

a) Temps mig d’execució del programa que executa n=64 iteracions en l’arquitectura

superescalar. Per si us fa falta, p es la probabilitat de saltar en el salt “beqf F1, fin”.

b) Ídem en l’arquitectura vectorial.

Problema 6

Dado un procesador vectorial con las siguientes características:

•

8 registros vectoriales (V0-V7) de 128 elementos (MVL=128). Disponen de un único puerto

de acceso bidireccional.

• 1 unidad funcional de suma (Tiempo de arranque 7 ciclos), 1 unidad funcional de

multiplicación (Tiempo de arranque 8 ciclos) y una unidad funcional de división (Tiempo de

arranque 20 ciclos).

• 1 camino de acceso a memoria bidireccional.

• La memoria está organizada en 16 bancos de memoria entrelazados de una palabra de

ancho. Los bancos tiene un tiempo de acceso de 6 ciclos.

• La unidad de control permite lanzar una instrucción por ciclo.

• Encadenamiento de un máximo de dos instrucciones.

• Una instrucción no se puede lanzar si otra instrucción anterior está bloqueada debido a un

riesgo estructural o de datos.

Queremos ejecutar el siguiente programa en alto nivel:

real v(n), a(n, n)

5

do i = 1, n

v(i) = (a(i, i) + a(n-i+1, i)) / b

end do

Dado que la matriz a está almacenada por columnas, el código vectorial (eliminando la parte escalar)

podría ser el siguiente:

ld.vws V0, ($1, #stride1)

ld.vws V1, ($2, #stride2)

add.v V2, V1 + V0

div.v V3, V2, F1

st.v $3, V3

Se pide:

a) ¿Cuánto valdrían los valores stride1 y stride2 para n = 127?

b) Dibujad el diagrama de tiempo de ejecución de la primera instrucción de load para n = 127.

Ídem para la segunda instrucción de load suponiendo que la instrucción 1 ya ha terminado.

c) Dibujad el diagrama de tiempo de ejecución de para todo el código, marcando los

encadenamientos y calculad el tiempo total de ejecución para n = 128.

d) Calculad el tiempo total de ejecución para n = 1000 (teniendo en cuenta el strip mining).

Problema 7

Donat el següent programa:

for ( i = 1; i <= n ; i++) {

if (a[i] ≠ 0) then x[i] = y[i*2] / a[i*4];

}

i la seva traducció a llenguatge màquina per un processador vectorial:

CODI VECTORIAL

mov $2, @A

mov $3, @X

mov $4, @Y

ld.v V1, 0($2)

sne.v V1, 0

ld.vws V2, 0($3), 4; amb stride i mascara

ld.vws V3, 0($4), 2

div.v V3, V2, V1

st.v V3, 0($4)

cvm

Es demana calcular el temps mig d’execució del programa quan N=64 iteracions i amb l’arquitectura

vectorial següent:

•

•

•

Processador vectorial amb una unitat vectorial de propòsit general (suma, comparació, ...,

temps d’arrancada de 4 cicles), una unitat vectorial per fer la divisió (temps d’arrancada de

10 cicles) i un port d’accés a memòria (temps d’arrancada de 4 cicles). La longitud vectorial

màxima es de 64. S’incorporen tots els encadenaments necessaris i els registres vectorials

tenen ports de lectura i escriptura independents.

Memòria organitzada en 4 mòduls. Temps d’accés a un mòdul de memòria de 4 cicles.

El processador escalar es capaç d’iniciar l’execució de dues instruccions escalars per cicle,

o una escalar i una vectorial per cicle.

6

Problema 8

Dado un procesador vectorial con las siguientes características:

•

•

8 registros vectoriales (V0-V7) de 128 elementos (MVL=128)

1 sumador y 3 multiplicadores, todas las unidades funcionales tienen un tiempo de arranque

de 10 ciclos.

• 1 camino de acceso a memoria bidireccional, todas las operaciones de acceso a memoria

tienen un tiempo de arranque de 15 ciclos.

• La unidad de control permite lanzar una instrucción por ciclo.

• Una instrucción no se puede lanzar si otra instrucción anterior está bloqueada debido a un

riesgo estructural o de datos.

Queremos analizar su comportamiento al ejecutar el código máquina vectorial correspondiente a este

bucle:

do i=1, 128

x(i) = y(i) *(s*x(i)+t*z(i))

enddo

Suponed que los vectores de datos X, Y, Z están inicialmente en memoria (las direcciones de base están

en los registros Rx, Ry y Rz), que al final debe quedar en memoria el vector resultado X, y que los

escalares s y t están en los registros Rs y Rt.

Proponed el código máquina vectorial más eficiente que encontréis, y calculad el tiempo de

ejecución (dibujar cronograma) para cada uno de los casos que se describen a continuación.

a) No es posible ningún encadenamiento y solapamiento de instrucciones.

b) Se permite solapar instrucciones.

c) Lo mismo que el apartado b), pero además se puede encadenar dos (no más) instrucciones

sucesivas siempre y cuando sea en forma directa (no en cualquier instante).

d) Lo mismo que el apartado b), pero además se pueden encadenar cualquier número de

instrucciones dependientes sucesivas, y en cualquier instante de su ejecución.

e) Lo mismo que el apartado d), pero además se añade un segundo camino con memoria.

Problema 9

Suposeu un sistema multiprocessador amb memòria compartida format per 8 processadors que

cooperen en l’execució paral·lela del següent codi seqüencial:

integer*8 a(max)

/* vector amb “max” elements; cada element

és un enter que ocupa 8 bytes */

for (i=0; i<max; i++)

a(i) = 1.0;

for (i=0; i<max-1; i++)

a(i) = a(i+1) * 2.0

for (i=1; i<max-1; i++)

a(i-1) = a(i) + a(i+1) / 3.0

La paral.lelització de codi consisteix en que cada processador executa (aprox. max/8) iteracions

consecutives de cada bucle. Cada processador disposa de una memòria cache de 64 Kbytes

(correspondència directa) i la mida de la línia (bloc) de la cache es de 64 bytes. El protocol de coherència

es “escriptura i invalidació” amb “snoopy”.

a) Suposant que max=1024, ¿quants bytes es transfereixen per la xarxa d’interconnexió durant

l’execució de tot el programa?

b) Ídem si max=32.

Notes: Podeu considerar que l’execució de cada iteració dels bucles triga el mateix temps. En una

comanda d’invalidació es transfereix 1 byte per la xarxa d’interconnexió.

7

Problema 10

Considereu els següents paràmetres que defineixen el temps d’execució d’un programa seqüencial i de

la seva corresponent versió paral·lela:

•

•

Fracció paral·lelitzable: f; fracció seqüencial: 1-f.

Probabilitat de hit en la fracció seqüencial: hs; probabilitat de miss en la fracció seqüencial: 1hs. Aquestes probabilitats també apliquen a la versió seqüencial.

Probabilitat de hit en la fracció paral·lela: hp; probabilitat de miss en la fracció seqüencial: 1hp.

Temps d’accés a cache: tmc cicles; temps d’accés a memòria principal compartida: tmp cicles.

P processadors, cadascun amb un CPI (suposant hit a la memòria cache): CPI.

•

•

•

Es demana:

a) Trobeu l’expressió que defineix el speed-up (relació entre el temps d’execució seqüencial i el

temps d’execució paral·lel) en funció dels paràmetres anteriors.

b) Si hp=hs, quina es l’expressió pel speed-up?

c) Com hauria d’empitjorar la probabilitat de hit hp respecte a hs (es a dir, la relació entre hp i hs)

per tal d’obtenir la meitat del speed-up obtingut a l’apartat b)? .

Problema 11

Es vol resoldre un sistema triangular d’equacions utilitzant un sistema multiprocessador. El sistema

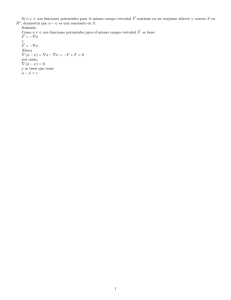

triangular es pot expressar com:

a 11 0

0

0

a 21 a 22 0

0

a 31 a 32 a 33 0

a 41 a 42 a 43 a44

b1

x1

×

x2

x3

=

x4

b2

b3

b4

on les incògnites a trobar es el vector [x1, x2, x3, x4]. Alhora de programar-lo en paral·lel, el problema el

podem rescriure tal com es mostra a continuació:

x1

b2

b3

b4

=

=

=

=

b1

b2

b3

b4

/

-

a11

a21 • x1; x2 = b2 / a22

a31 • x1; b3 = b3 - a32 • x2; x3 = b3 / a33

a41 • x1; b4 = b4 - a42 • x2; b4 = b4 - a43 • x3; x4 = b4 / a44

on podeu observar que el vector [b1, b2, b3, b4] del sistema es perd. Aquest plantejament suggereix una

possible implementació paral·lela del problema (plantejat pel cas general d’un sistema de N equacions

amb N incògnites):

doall (i=1; i<=N; i++) {

doall (j=1; j<=i-1; j++)

b(i) = b(i) - a(i, j) • x(j)

x(i) = b(i) / a(i, i)

}

Es demana:

a) Suposeu que el sistema multiprocessador consta de N processadors amb memòria compartida.

El bucle "doall" assigna iteracions consecutives a processadors consecutius. Afegir la

sincronització necessària per tal de garantir que el resultat de l’algorisme és correcte.

b) Si el sistema multiprocessador té memòria distribuïda, de manera que cada processador

8

guarda a la seva memòria local una fila de la matriu a, i un element dels vectors x i b. La

topologia de la xarxa es linial, es a dir, un processador p només es pot comunicar amb els seus

veïns p-1 i p+1. Afegir la comunicació necessària mitjançant pas de missatges.

Notes: Podeu utilitzar les primitives de sincronització i pas de missatges següents:

wait (semafor)

signal (semafor)

suposant que el hardware ofereix vectors de semàfors semafor(1:P). D’aquests vectors n’hi ha tants

com necessaris.

send (val, port)

receive (val, port)

on port={dreta | esquerra} indica cap on s’envia la dada val.

9