CIRCUITOS SECUENCIALES ASÍNCRONOS

Profesor Jorge Gianotti Hidalgo

Departamento de Ingeniería Eléctrica

Universidad de Antofagasta

2007

Sistemas Digitales

1

Modelo de Circuito Secuencial Asíncrono

Modalidad Nivel

Un circuito se considera asíncrono si no utiliza una señal de reloj

periódica para sincronizar sus cambios de estado interno.

Las sencillas técnicas asíncronas son necesarias para diseñar

dispositivos de memoria, circuitos con tiempos de entrada

imprevisibles y circuitos con varios relojes.

Los circuitos asíncronos son potencialmente más rápidos que los

síncronos, pero son difíciles de analizar y diseñar. El modelo básico

es el de Huffman, que restringe la ubicación de retardos del circuito

y los tiempos en que pueden cambiar las entradas primarias.

Sistemas Digitales

2

• Al analizar su comportamiento se distinguen los estados

estables, aquellos que no cambian con entradas primarias

constantes, de los estados inestables, que si varían.

• Por otra parte ocurren las carreras que ocurren cuando dos o

más variables de estado cambian como respuesta a un solo

cambio de las variables de entrada al sistema secuencial

asíncrono. La carrera se considera crítica si el estado estable

final depende del orden en que cambien las variables de

estado.

• Los circuitos secuenciales asíncronos deben diseñarse para

evitar las carreras críticas y diversos riesgos (señales

espurias)

Sistemas Digitales

3

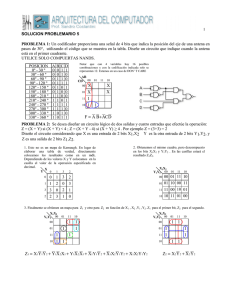

Modelo Básico de Circuito Modalidad Nivel (HUFFMAN)

Entradas

primarias

Entradas

secundarias

X1

X2

Lógica

Z1

Z2

Xn

Combinacional

Zp

y1

de salida

y2

(Variables de

estado)

yr

salidas

Y1

Yr

Y2

excitaciones

retardo

retardo

retardo

Sistemas Digitales

4

• Los elementos de retardo son una concentración de los retardos

distribuidos en los elementos lógicos combinacionales. Se

considera que estos proporcionan una memoria a corto plazo.

• Cuando hay un cambio en una variable de entrada (xi), el retardo

le permite al circuito recordar los valores actuales de las variables

de estado y1,y2….yr un tiempo lo suficientemente largo como

para desarrollar los nuevos valores de Y1, Y2,…Yr, que a su vez,

se convierten en los nuevos valores del siguiente estado de

y1,y2….yr después de un retardo.

• De la figura del modelo de HUFFMAN, se aprecia que los cambios

en las variables de las entradas secundarias y de excitación se

pueden producir en respuesta a un cambio de las variables de

entrada X1,X2,..Xn

Sistemas Digitales

5

• El trato que se realiza en el análisis para el diseño de

secuenciales asíncronos se denomina modalidad fundamental,

que significa que sólo se permite que ocurra en las variables de

entrada, donde sólo pueden cambiar una a la vez, pero no dos

o más simultaneamente. De esta forma las variables secundarias

y de excitación deberán también cambiar sólo una a la vez.

• El circuito se estabiliza o cae en un estado estable cuando las

variables de excitación y secundarias llegan a la estabilización de

sus valores.

• El proceso de síntesis que se sigue para obtener un diseño

definitivo es semejante al seguido para los secuenciales

síncronos.

Sistemas Digitales

6

Ejemplo para analizar un sistema secuencial asíncrono

Un circuito de retardo de control, tiene una entrada de pulso de

control X, una entrada de reloj C y una salida de pulso de control Z.

los pulsos en la línea de entrada estarán siempre separados por

varios períodos de reloj.

Siempre que se produzca un pulso en la línea X, se superpondrá a un

pulso de reloj y tendrá más o menos la misma anchura que éste. Es

decir, la línea X sólo pasará a valor “1” despues de que el pulso de

reloj pase a “1” y retornará a valor “0” sólo después de que el pulso

de reloj haya vuelto a valor “0”.

Por cada pulso de entrada debe haber un pulso de salida en la línea

Z, que coincida con el siguiente pulso de reloj que sigue al pulso en

X. Por lo tanto, cada pulso X da como resultado un pulso en Z

retardado en aproximadamente un período de reloj.

Sistemas Digitales

7

Diagrama del sistema y señales de entrada y salida

X

Retardo de

C

Control

Z

C

X

Z

Sistemas Digitales

8

Desarrollo: Tabla de Flujo Primitiva

Entradas: XC

Estado

Inicial

Salida: Z

00

01

11

10

00

01

11

10

1

2

-

-

0

-

-

-

1

2

3

-

-

0

-

-

-

-

3

4

-

-

0

-

5

-

-

4

-

-

-

0

5

6

-

-

0

-

-

-

1

6

-

-

-

1

-

-

Sistemas Digitales

9

Implicancia para resolver los estados mínimos

2

√

3

√

√

4

1-5

1-5

√

5

2-6

2-6

1-5

√

√

6

2-6

√

1-5

1-5

3

4

5

1

2

Clase de estado: a = (1,2) ; b = (3,4,5) ; c = (6)

Sistemas Digitales

10

Tabla Mínima de Flujo y Asignación de Estados

Estado

Inicial

Entradas: XC

Salida: Z

00

01

11

10

00

01

11

10

a=(1,2)

a

a

b

-

0

0

-

-

b=(3,4,5)

b

c

b

b

0

-

0

0

c=(6)

a

c

-

-

-

1

-

-

y2y1 = 00 para el estado “a”

y2y1 = 01 para el estado “b”

y2y1 = 11 para el estado “c”

Asignación de

estados

y2y1 = 10 don’t care

Sistemas Digitales

11

Ecuaciones de Estado

Tabla de Transición y Mapa de Salida

XC

y2y1

XC

00

01

11

10

00

00

00

01

-

00

01

01

11

01

01

01

11

00

11

-

-

11

-

1

-

-

10

-

-

-

-

10

-

-

-

-

Y2Y1

Sistemas Digitales

y2 y 1

00

01

11

10

-

-

Z

12

Ecuaciones de Estado

Mapas de Excitación y Funciones de Excitaciones

XC

y2y1

XC

00

01

11

10

00

0

0

1

-

0

01

1

1

1

1

-

-

11

0

1

-

-

-

-

10

-

-

-

-

00

01

11

10

00

0

0

0

-

01

0

1

0

11

0

1

10

-

-

y2 y 1

Y2

Y2 = X ’ C y 1

Sistemas Digitales

Y1

Y1 = X + y2’ y1 + C y1

Z = y2

13

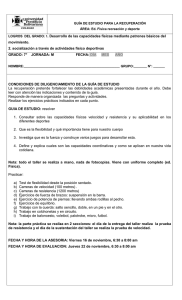

Circuito Final

Y2'

X

Z

Y2

y2'

y1

Y1

C

y1

Si el circuito final tiene retardos de tiempo distintos por compuerta,

esto puede introducir carreras críticas.

A continuación, se analizará la naturaleza de estas carreras y la

manera de lograr eliminarlas.

Sistemas Digitales

14

Ciclos y Carreras

•

Un sistema o bien un circuito puede asumir más de un estado

inestable antes de llegar a un nuevo estado estable.

•

Si para un estado inicial dado y una transición de las variables

de entrada, este tipo de secuencia de estados inestables es

única, se le denomina CICLO.

Sistemas Digitales

15

Ciclos

X2X1

y2 y 1

00

00

01

1

2

01

11

3

3

10

4

4

11

2

10

Las transiciones del estado

estable 1 proceden a través

de los estados inestables 2,3 y

4 hasta el estado estable 4

cualquier otro inicio en los

estados estables seguirá el

mismo camino hacia el estado

estable 4

Y2Y1

Sistemas Digitales

16

Ciclos (estados asignados)

X2X1

y2 y 1

00

00

01

00

01

01

11

10

11

11

11

10

01

10

10

Y2Y1

Sistemas Digitales

17

Carreras

Carreras No-Críticas

X2X1

y2 y 1

X2X1

01

00

11

1

2

00

01

2

01

11

11

2

11

11

10

2

10

11

Y2Y1

Sistemas Digitales

10

00

01

00

11

y2 y 1

00

11

10

Y2Y1

18

Carreras

Carreras Críticas

X2X1

y2 y 1

X2X1

01

11

10

00

00

00

01

-

b

01

01

11

01

01

-

-

11

00

11

-

-

-

-

10

-

-

-

-

01

11

10

00

a

a

b

-

01

b

c

b

11

a

c

10

-

Y2Y1

Sistemas Digitales

y2 y 1

00

00

Y2Y1

19

Eliminación de Carreras Críticas

Carreras críticas del ejemplo anterior.

XC

y2y1

00

01

11

10

00

00

00

01

-

01

01

11

01

01

11

00

11

-

-

10

-

-

-

-

Cuando XC cambia de 01 a 00,

el estado estable 11 debe llegar

al estado estable 00 y no al

estado estable 01 pues así lo

indica el estado inestable 00 en

XC=00, luego hay carrera crítica

Y2Y1

Sistemas Digitales

20

Eliminación de Carreras Críticas

Carreras críticas del ejemplo anterior.

XC

y2y1

00

01

11

10

00

00

00

01

-

01

01

11

01

01

11

10

11

-

-

10

00

-

-

-

Al cambiar el estado inestables

00 en XC=00 para y2y1=11 al

estado inestable 10, estamos

conduciendo al circuito a que

secuencia luego al estado

inestable 00 y finalmente al

estado estable 00

Y2Y1

Sistemas Digitales

21

Eliminación de Carreras Críticas

Carreras críticas del ejemplo anterior.

Bajo esta nueva situación, ha cambiado la situación de las ecuaciones

de estado y se debe volver a la nueva Tabla de Transición.

XC

y2y1

Sistemas Digitales

00

01

11

10

00

00

00

01

-

01

01

11

01

01

11

10

11

-

-

10

00

-

-

-

Y2Y1

22

Mapas de Excitación y Funciones de Excitaciones

XC

y2y1

XC

00

01

11

10

00

0

0

1

-

0

01

1

1

1

1

-

-

11

0

1

-

-

-

-

10

0

-

-

-

00

01

11

10

00

0

0

0

-

01

0

1

0

11

1

1

10

0

-

y2 y 1

Y2

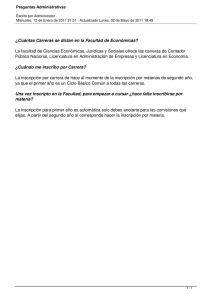

Y2 = X’ C y1 + y2y1

Sistemas Digitales

Y1

Y1 = X + y2’ y1 + C y1

Z = y2

Nuevo término para eliminar carrera crítica

23

Circuito Final Libre de Carreras Críticas

Y2

Z

C

X

Sistemas Digitales

Y1

24

Asignación de Estados

Es importante considerar que la asignación de estados debe buscar

la eliminación de las carreras críticas.

X1X2

y2 y 1

Sistemas Digitales

00

01

11

10

1

2

5

8

3

4

5

7

3

2

6

7

1

4

5

7

Y2Y1

25

Por ejemplo: si se aplicara al azar una asignación como la que

se indica en la figura, se podrían generar las siguientes

carreras críticas:

X1X2

y2 y 1

00

01

11

10

00

a

c

b

a

11

a

b

b

d

10

b

c

c

d

01

d

c

b

d

Y2Y1

Sistemas Digitales

26

Si se intercambia la asignación entre las filas 2 y 4 se logra

eliminar las carreras críticas.

X1X2

y2 y 1

00

01

11

10

00

a

c

b

a

01

a

b

b

d

10

b

c

c

d

11

d

c

b

d

Y2Y1

Sistemas Digitales

27

Otro ejemplo de asignación de estados que resulta algo más

complejo es el siguiente. Sea la siguiente tabla de flujo mínimo:

En

esta

tabla

existe

carreras críticas hacia el

estado estable “C”, para

X1X2=11 desde más de un

estado estable.

Sistemas Digitales

00

X1X2

01

a

11

10

a

c

a

b

b

c

b

a

b

c

d

d

d

c

d

28

Para lograr superar

esta situación se

opta por trabajar

con tres elementos,

y1y2y3, tal que la

asignación sea la

siguiente:

Sistemas Digitales

y1 y 2 y3

X1X2

00

01

11

10

000

a

a

c

a

001

a

b

c

d

011

b

b

c

b

010

-

-

-

-

110

-

-

-

-

111

-

-

-

-

101

d

d

c

d

100

-

-

-

29

Ejemplo Ilustrativo Operación Nivel (modo fundamental)

Un circuito de conmutación secuencial bajo operación de nivel,

tiene 2 terminales de entrada, X1 y X2 y un terminal de salida Z.

El circuito trabaja de la manera siguiente:

• Z va a estado “1” cuando X1 cambio a estado “1”.

• Z va a estado “0” cuando X2 cambia a estado “0”.

• Ninguna otra secuencia de entrada produce cambios en la

salida Z. Solamente una entrada puede cambiar de estado a

la vez (modo fundamental)

• Obtener:

1.- La tabla de Flujo Primitiva

2.- La tabla de Flujo Mínima

3.- Asignación de estados libre de carreras críticas.

4.- Ecuaciones de las variables de estado.

5.- El diagrama del circuito

Sistemas Digitales

30

Solución : Tabla de Flujo Primitiva

X1X2

00

01

Sistemas Digitales

11

10

Z

1

2

-

3

0

1

2

4

-

0

5

-

4

3

1

-

6

4

7

1

5

6

-

3

1

1

6

4

-

1

1

-

8

7

0

-

2

8

7

0

31

Solución: Tabla de Flujo Mínima

Por simple inspección se observa que las clases de estado son

las siguientes: a=(1,2); b=(3,5); c=(4,6); d=(7,8)

X1X2

Sistemas Digitales

00

01

11

10

Z

1

2

4

3

0

5

6

4

3

1

1

6

4

7

1

1

2

8

7

0

32

Solución: Clases de estado en Tabla de Flujo Mínima

X1X2

Sistemas Digitales

y1y2

00

01

11

10

Z

00

a

a

c

b

0

01

b

c

c

b

1

11

a

c

c

d

1

10

a

a

d

d

0

33

Solución: Asignación de Estados

Carreras Críticas

X1X2

X1X2

y1 y 2

00

01

11

10

y1 y 2

00

01

11

10

00

00

00

11

01

00

0

0

-

-

01

01

11

11

01

01

1

1

1

1

11

00

11

11

10

11

-

1

1

-

10

00

00

10

10

10

0

0

0

0

Y1Y2

Sistemas Digitales

Z

34

Solución: Asignación de Estados Libre de Carreras Críticas

X1X2

X1X2

y1 y 2

00

01

11

10

y1 y 2

00

01

11

10

00

00

00

01

01

00

0

0

-

-

01

01

11

11

01

01

1

1

1

1

11

10

11

11

10

11

-

1

1

-

10

00

00

10

10

10

0

0

0

0

Y1Y2

Sistemas Digitales

Z

35

Solución: Ecuaciones de Variables de Estado Y1 y Y2

X1X2

X1X2

y1 y 2

00

01

11

10

y1 y 2

00

01

11

10

00

0

0

0

0

00

0

0

1

1

01

0

1

1

0

01

1

1

1

1

11

1

1

1

1

11

0

1

1

0

10

0

0

1

1

10

0

0

0

0

Y1= x2y2 + y1y2 + x1y1

Sistemas Digitales

Y2 = x1y1’ + y1’y2 + x2y2

36

Solución: Ecuación de Salida Z

X1X2

y1 y 2

00

01

11

10

00

0

0

-

-

01

1

1

1

1

11

-

1

1

-

10

0

0

0

0

Z = y2

Sistemas Digitales

37

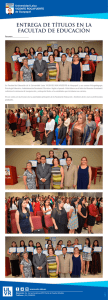

Solución: Ecuaciones Finales de Estado

Y1 = x2y2 + y1y2 + x1y1

Y2 = x1y1’ + y1’y2 + x2y2

Z = y2

Sistemas Digitales

38

Solución: Diagrama del Circuito

y2

X1 X2 y1

y1'

Y1

Y2

y1

y2

Z

Sistemas Digitales

39

Ejercicio

La figura y las ecuaciones siguientes definen un circuito

secuencial asíncrono en modo fundamental.

a. Obtenga una tabla de

flujo

Y1 = x2’y2 + x1y1 +x1x2’

Y2 = x1’y2 + x1’x2 + x2y1

Z = x1x2’ + x2y1’ + x1’y2

b. Utilice la tabla de flujo

preparada en la parte

(a) para determinar la X1

secuencia

de

salida X2

Lógica

correspondiente a la

Combinacio

y

secuencia de entrada 1

y2

nal

x1x2 = 00, 01, 11, 10,

11, 01, 00, 10 si las

líneas de retardo se

encuentran inicialmente

∆t

en cero (estado estable

∆t

x1 = x2 = y1 = y2 = 0).

Sistemas Digitales

Z

Y2

Y1

40

Solución: variables de estado

X1X2

X1X2

y1 y 2

00

01

11

10

y1y2

00

01

11

10

00

0

0

0

1

00

0

1

0

0

01

1

0

0

1

01

1

1

0

0

11

1

0

1

1

11

1

1

1

0

10

0

0

1

1

10

0

1

1

0

Y1= x2’y2 + x1y1 +x1x2’

Sistemas Digitales

Y2 = x1’y2 + x1’x2 + x2y1

41

Solución: salida

X1X2

y1 y 2

00

01

11

10

00

0

1

1

1

01

1

1

1

1

11

1

1

0

1

10

0

0

0

1

Z = x1x2’ + x2y1’ + x1’y2

Sistemas Digitales

42

Solución: Tabla de Flujo Mínima

X1X2

X1X2

y1 y 2

00

01

11

10

y1 y 2

00

01

11

10

00

00

01

00

10

00

0

1

1

1

01

11

01

00

10

01

1

1

1

1

11

11

01

11

10

11

1

1

0

1

10

00

01

11

10

10

0

0

0

1

Y1Y2

Sistemas Digitales

Z

43

Solución: Clases de estado en Tabla de Flujo Mínima

X1X2

X1X2

y1 y 2

00

01

11

10

y1 y 2

00

01

11

10

00

a

b

a

d

00

0

1

1

1

01

c

b

a

d

01

1

1

1

1

11

c

b

c

d

11

1

1

0

1

10

a

b

c

d

10

0

0

0

1

Y1Y2

Sistemas Digitales

Z

44

Solución: secuencia de salida

X1X2

00

01

11

10

11

01

00

10

Estado

a

b

a

d

c

b

c

d

Z

0

1

1

1

0

1

1

1

Sistemas Digitales

45

Ejercicio

Encuentre las ecuaciones de estado, libre de carreras críticas,

un circuito secuencial asíncrono que posee dos entradas, X1 y

una salida Z. El circuito se caracteriza porque:

para

X2 y

• Trabaja en modalidad fundamental

• La frecuencia de la señal de una de las entradas X es 4 veces

la frecuencia de la señal de salida en Z.

• La frecuencia de la señal de una de las entradas X es 2 veces

la frecuencia de la señal de salida en Z.

• Las señales de entrada y salida varían entre niveles binarios 0

y 1.

Sistemas Digitales

46

Solución

Diagrama de tiempo de acuerdo a condiciones del

problema

X1

X2

Z

Sistemas Digitales

47

Solución

X1

X2

X1

X2

Z

0

0

0

0

0

1

0

0

1

0

1

1

1

1

0

0

1

1

0

0

1

1

1

1

0

1

0

0

1

0

0

0

0

0

1

1

0

0

1

1

1

1

1

1

1

0

1

1

0

1

1

1

1

1

1

1

0

0

1

1

0

0

0

0

0

1

0

0

1

0

1

1

1

1

0

0

1

1

0

0

1

1

1

1

0

1

0

0

1

0

Sistemas Digitales

Tabla de Flujo Primitiva

X1X2

00

01

11

10

Z

1

4

-

2

0

5

-

3

2

0

-

4

3

2

0

5

4

3

-

0

5

8

-

6

1

1

-

7

6

1

-

8

7

6

1

1

8

7

-

1

48

Tabla de Implicancia

2

1-5

3

√

√

4

1-5

√

√

1-5

2-6

3-7

4-8

2-6

4-8

2-6

3-7

1-5

3-7

1-5

3-7

4-8

√

√

1-5

√

√

5

6

7

5

6

2-6

7

4-8

2-6

3-7

2-6

8

4-8

1-5

3-7

3-7

4-8

1

2

3

Sistemas Digitales

4

49

Clases de Estado y Tabla Mínima

Clases:

a = {1,3} ; b = {2,4} ; c = {5,7} ; d = {6,8}

Tabla Mínima

X1X2

Z(X1X2)

00

01

11

10

00

a

b

a

b

01

c

b

a

11

c

d

10

a

d

Sistemas Digitales

00

01

11

10

00

0

--

0

--

b

01

--

0

--

0

c

d

11

1

--

1

--

c

d

10

--

1

--

1

50

Asignación de Estados y Ecuaciones de Estado

Clases:

a = 00 ; b = 01 ; c = 11 ; d = 10

X1X2

Z(X1X2)

00

01

11

10

00

01

11

10

00

00

01

00

01

00

0

--

0

--

01

11

01

00

01

01

--

0

--

0

11

11

10

11

10

11

1

--

1

--

10

00

10

11

10

10

--

1

--

1

Y1 = y2 x’1 x’2 + y1 x2 + y1 x1

Y2 = y’1 x’1 x2 + y’1 x1 x’2 + y2 x’1 x’2 + y1 x1 x2

Z = y1

Sistemas Digitales

51