- Ninguna Categoria

Informe - Escuela de Ingeniería Eléctrica

Anuncio

Universidad de Costa Rica

Facultad de Ingeniería

Escuela de Ingeniería Eléctrica

IE – 0502 Proyecto Eléctrico

Síntesis y optimización de la CPUCR en la librería

AMI 0.5 micrones con herramientas de Synopsys

Por:

Alejandro Mora Lizano 982423

Henry Rojas Fonseca A03672

Diciembre del 2004

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas

de Synopsys

ii

Síntesis y optimización de la CPUCR en la

librería AMI 0.5 micrones con herramientas de

Synopsys

Por:

Alejandro Mora Lizano

Henry Rojas Fonseca

Sometido a la Escuela de Ingeniería Eléctrica

de la Facultad de Ingeniería

de la Universidad de Costa Rica

como requisito parcial para optar por el grado de:

BACHILLER EN INGENIERÍA ELÉCTRICA

Aprobado por el Tribunal:

___________________

Ing. Roberto Rodríguez

Profesor Guía

___________________

Ing. Enrique Coen

Profesor Lector

___________________

Ing. Federico Ruiz

Profesor Lector

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas iii

de Synopsys

ÍNDICE GENERAL

ÍNDICE DE FIGURAS ___________________________________________________v

ÍNDICE DE TABLAS ___________________________________________________ vi

NOMENCLATURA ____________________________________________________ vii

RESUMEN ___________________________________________________________ viii

CAPÍTULO 1: Introducción ______________________________________________ 1

1.1 Objetivos _______________________________________________________________ 3

1.1.1 Objetivos Específicos:_________________________________________________________ 3

1.2 Metodología ____________________________________________________________ 3

CAPÍTULO 2: Marco teórico _____________________________________________ 4

2.1 Diseño en VLSI__________________________________________________________ 4

2.1.1 Métodos de diseño en VLSI ____________________________________________________ 7

2.1.2 Síntesis lógica _______________________________________________________________ 8

2.2 Herramientas de Synopsys ________________________________________________ 9

2.2.1 Librerías de celdas __________________________________________________________ 11

CAPÍTULO 3: Guía para el uso de Design Analyzer en la síntesis de circuitos

integrados ____________________________________________________________ 14

3.1

Ventana del Design Analyzer __________________________________________ 14

3.1.1 Barra de menú ______________________________________________________________ 15

3.2 Síntesis de un nuevo proyecto _____________________________________________ 18

3.2.1 Síntesis manual _____________________________________________________________ 18

3.2.1.1 Ventana de comandos ____________________________________________________ 18

3.2.1.2 Especificación de la librería _______________________________________________ 20

3.2.1.3 Lectura del diseño _______________________________________________________ 21

3.2.1.4 Definición del entorno____________________________________________________ 22

3.2.1.5 Definir las restricciones___________________________________________________ 22

3.2.1.5 Optimización del diseño __________________________________________________ 24

3.2.1.6 Análisis y resolución de problemas de diseño__________________________________ 24

3.2.1.7 Salvar la base de datos del diseño ___________________________________________ 26

3.2.2 Síntesis por medio de un script _________________________________________________ 27

CAPÍTULO 4: Síntesis de la CPUCR con el Design Analyzer __________________ 29

4.1 Problemas en la síntesis de la CPUCR ______________________________________ 30

4.2 Problemas del código de la CPUCR conductual _____________________________ 33

4.2.1 Descripción de los problemas en las simulaciones __________________________________ 34

4.3 Análisis de resultados____________________________________________________ 39

4.3.1 Posibles problemas __________________________________________________________ 41

CAPÍTULO 5: Conclusiones y recomendaciones_____________________________ 45

5.1 Conclusiones ___________________________________________________________ 45

5.2 Recomendaciones ______________________________________________________ 46

BIBLIOGRAFÍA ______________________________________________________ 47

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas

de Synopsys

iv

Libros ___________________________________________________________________ 47

Manuales _________________________________________________________________ 47

Páginas web ______________________________________________________________ 47

Información digital ________________________________________________________ 47

APÉNDICES _________________________________________________________ 48

Apéndice A. Script utilizado para la síntesis de la CPUCR ________________________ 48

Apéndice B. Script original __________________________________________________ 48

Apéndice C. Instrucciones de la CPUCR _______________________________________ 50

Apéndice D. Diagramas de temporización del modelo estructural obtenido de la CPUCR

_________________________________________________________________________ 51

Apéndice E. Bitácora de la sesión del Design Analyzer ___________________________ 62

Apéndice F. Modelo conductual original _______________________________________ 68

cpucr_rarr.v ____________________________________________________________________ 68

Dec_Inst.v _____________________________________________________________________ 83

Apéndice G. Modelo conductual modificado____________________________________ 84

Apéndice H. Modelo estructural obtenido en la síntesis con el Design Analyzer _______ 99

ANEXOS____________________________________________________________ 142

Anexo 1. Características de una celda Flip-Flop D de la librería AMI 0.5 __________ 142

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas

de Synopsys

v

ÍNDICE DE FIGURAS

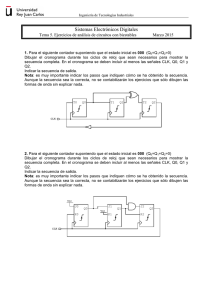

Figura 2.1. Evolución de la complejidad lógica en circuitos integrados. __________________________ 4

Figura 2.2. Ilustración de la ley de Moore. _________________________________________________ 5

Figura 2.3. Inversor y sus perspectivas. ____________________________________________________ 6

Figura 2.4. Visualización de los métodos de diseño en VLSI. ___________________________________ 8

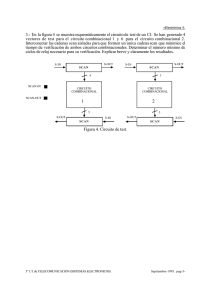

Figura 2.5. Design Compiler dentro del flujo de diseño. ______________________________________ 10

Figura 2.6. Ilustración de un transistor NMOS. _____________________________________________ 13

Figura 2.7. Ilustración de la Leff. ________________________________________________________ 13

Figura 3.1. Ilustración de la ventana del Design Analyzer. ____________________________________ 14

Figura 3.2. Submenú de atributos resaltado. _______________________________________________ 17

Figura 3.3. Ventana de comandos._______________________________________________________ 19

Figura 3.4. Esquema para la síntesis de un proyecto en el Design Analyzer. ______________________ 20

Figura 4.1. Simulación programa de prueba 1. _____________________________________________ 35

Figura 4.2. Simulación programa de prueba 2. _____________________________________________ 35

Figura 4.3. Simulación programa de prueba 3. _____________________________________________ 36

Figura 4.4. Simulación programa de prueba 4. _____________________________________________ 36

Figura 4.5. Simulación programa de prueba 5. _____________________________________________ 37

Figura 4.6. Simulación programa de prueba 6. _____________________________________________ 37

Figura 4.7. Simulación programa de prueba 7. _____________________________________________ 38

Figura 4.8. Simulación programa de prueba 8. _____________________________________________ 38

Figura 4.9. Simulación programa de prueba 9. _____________________________________________ 39

Figura 4.10. Lógica de tercer estado inferida con el comando assign. ___________________________ 42

Figura 4.11. Lógica de buffer de tercer estado con registros. __________________________________ 43

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas

de Synopsys

vi

ÍNDICE DE TABLAS

Tabla 2.1 Pasos del diseño en VLSI. ______________________________________________________ 6

Tabla 3.1. Formatos aceptados por el Design Analyzer. ______________________________________ 26

Tabla 4.1. Dispositivos inferidos por el Design Analyzer. _____________________________________ 40

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas vii

de Synopsys

NOMENCLATURA

VLSI

AMI

DA

DC

CI

HDL

CMOS

CAD

ASIC

Integración a muy gran escala

AMI semiconductor

Design Analyzer

Design Compiler

Circuitos integrados

Lenguaje de descripción de hardware

Silicio óxido metálico complementario

Diseño asistido por computadora

Circuito integrado para una aplicación específica

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas viii

de Synopsys

RESUMEN

El presente trabajo trata sobre el uso de las herramientas de Synopsys en la síntesis de un

diseño en VLSI y su posterior aplicación en la síntesis con la librería AMI 0.5 de la

CPUCR.

Para esto, se dividió el trabajo en tres partes:

1. Una breve explicación del diseño en VLSI, con un poco de su historia y

una reseña con los diferentes métodos que existen, resaltando el diseño

utilizando librerías estándar.

2. Un manual de uso para la síntesis por medio de librerías estándar

utilizando las funciones básicas de las herramientas, propiamente del

Design Analyzer

3. La síntesis de la CPUCR y el análisis de la misma, explicando los

inconvenientes que se presentaron y las soluciones aplicadas. Además, se

dejan abiertas varias posibilidades para la corrección de algunos errores

propios de la elaboración del código en su forma conductual, para lograr

una síntesis sin problemas posteriores.

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas

de Synopsys

1

CAPÍTULO 1: Introducción

Los circuitos integrados (CI) día con día evolucionan y literalmente se van integrando a

la vida cotidiana del ser humano, se utilizan en estructuras de la simplicidad de un reloj

hasta en la complejidad de las súper computadoras. Este rango de aplicación tan extenso

ubica a los circuitos integrados como una herramienta dinámica fundamental que facilita

el trabajo diario del hombre.

El desarrollo de los CI ha estado dominado tradicionalmente por las grandes potencias

mundiales, en especial Japón, Estados Unidos, Alemania y Francia; aunque su

manufactura muchas veces se da en países subdesarrollados, tales como Costa Rica.

Además, las universidades de los países desarrollados destinan altas sumas de dinero a la

enseñanza del diseño de CI llevándolos no sólo a la investigación teórica, sino también a

la práctica. Dentro de esta realidad, la Escuela de Ingeniería Eléctrica de la Universidad

de Costa Rica (UCR), por medio de su Departamento de Automática y Sistemas

Digitales, desea llevar a la práctica los conocimientos teóricos adquiridos por sus

estudiantes, por lo que ha comenzado una etapa de diseño de circuitos integrados y su

posterior fabricación gracias a compañías de bajo costo que ayudan a universidades con

el fin de nivelar la formación académica de sus estudiantes con la formación que se

imparte en la universidades del primer mundo.

Para esto, se ha escogido a la CPUCR; una unidad central de procesamiento que dispone

de un bus de direcciones de 16 líneas, un BUS de datos bidireccional de 8 bits y un bus

de control de 12 líneas. Esto por cuanto ya se cuenta con un diseño teórico realizado en

la UCR a nivel de un lenguaje HDL (Hardware Description Language)1. Además, este

componente ha sido ampliamente estudiado en la escuela, para citar algunos estudios:

•

Análisis y revalidación del diseño de la CPUCR. José Pablo Arguedas, Lochi

Yu Lo (2002)

1

Lenguaje de descripción de Hardware

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas

de Synopsys

•

2

Conclusión del diseño físico y construcción de la CPUCR. Enrique Martin

Acuña Acosta (1993)

•

Depuración del diseño de la CPUCR. Frantz Aimé Gamboa, Ramón Mena

Licairac (2001)

•

Diseño físico de la CPUCR. José Campos Briceño, Luis Golcher Balguil,

Jorg Sander Mangel (1991)

•

Modelado y síntesis de la CPUCR. Roberto Arellano Cartín, José Antonio

Cruz Pastora (2003)

•

Síntesis en VLSI de la CPUCR. Javier Gonzáles Hidalgo, Luis Diego León

Hoffman (2001)

Para poder lograr avanzar en el área de diseño de circuitos integrados se debe disponer de

la ayuda de herramientas de cómputo que permitan realizar compilaciones y síntesis de

grandes proyectos digitales. Para este efecto se utilizan las herramientas de la familia de

Synopsys, específicamente el software Design Compiler y Design Analyzer. Con éstas se

desea obtener una síntesis de la CPUCR, también se pretende optimizar el modelo de

manera que quede en una forma simplificada, lo más veloz posible.

Debido a la importancia de promover el desarrollo de este tipo de tecnologías, se

considera de gran importancia elaborar, paralelamente a la síntesis, un manual para la

utilización del software de síntesis (Design Compiler de Synopsys), el cual servirá de guía

para la aplicación de la herramienta en la síntesis de otros circuitos integrados diseñados

por la Escuela de Ingeniería Eléctrica.

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas

de Synopsys

3

1.1 Objetivos

●

Síntesis y Optimización de la CPUCR en la librería AMI 0.5 micrones, utilizando las

herramientas de Synopsys.

1.1.1 Objetivos Específicos:

●

Generación de documentos y manuales de utilización de las herramientas en el flujo de

diseño de circuitos integrados.

●

Concreción del diseño del microprocesador CPUCR.

1.2 Metodología

Tal y como se desprende de los objetivos del proyecto, este cuenta de dos partes

esenciales, la creación de un manual o guía para la utilización de la herramienta

(software) de Synopsys y la síntesis en sí de la CPUCR, éste último sería poner en

práctica el primero.

Para el primer punto, se requiere realizar una investigación de la herramienta y aplicarla

en el flujo de diseño de circuitos integrados, esto se procederá a documentar paso a paso

de manera tal que sirva como guía para futuras experiencias con la misma.

Para el segundo punto, sería poner en práctica los resultados del punto uno en el flujo de

diseño, ahora sí, específicamente de la CPUCR. De igual forma se necesita documentar

el procedimiento, pero esta vez ya se cuenta con la información registrada en el punto

anterior.

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas

de Synopsys

4

CAPÍTULO 2: Marco teórico

2.1 Diseño en VLSI

Desde el comienzo de la electrónica moderna con el descubrimiento de los transistores

primitivos hasta el día de hoy, los científicos se han centrado en la disminución del

tamaño de los mismos para su posterior integración junto con millones más en los

circuitos integrados, con el fin de hacerlos más versátiles, compactos y baratos. De esta

premisa viene lo que se conoce como VLSI (Very Large Scale Integration)2, que es un

nivel de integración que comprende de arreglos de más de 2000 a 20000 compuertas3.

Para esto, normalmente se utiliza la tecnología CMOS (Complementary Metal Oxide

Silicon)4, basada en transistores MOSFET (Metal Oxide Semiconductor Field Effect

Transistors)5. Aunque hay otras familias de transistores más rápidas, los arreglos que se

obtienen con los MOSFET consumen menos potencia y son más fáciles de fabricar. Su

bajo consumo de potencia se debe a que prácticamente sólo consumen potencia durante

los períodos de transición de un estado en alto a uno en bajo o viceversa.

ERA

FECHA

COMPLEJIDAD

Transistor sencillo

1959

menos de 1

Unidad lógica (una compuerta)

1960

1

Multifunción

1962

2-4

Función compleja

1964

5 - 20

Integración a mediana escala

1967

20 - 200

(MSI)

Integración a gran escala

1972

200 - 2000

(LSI)

Integración a muy gran escala

1978

2000 - 20000 (VLSI)

Integración a ultra gran escala

1989

20000 - ?

(Número de compuertas lógicas por CHIP)

(ULSI)

Figura 2.1. Evolución de la complejidad lógica en circuitos integrados3.

2

Integración a muy gran escala

http://lsiwww.epfl.ch/LSI2001/teaching/webcourse/ch01/ch01.html

4

Silicio complementario óxido metálico

5

Transistores de efecto de campo de semiconductor óxido metálico

3

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas

de Synopsys

5

Los circuitos integrados VLSI juegan un papel clave en el desarrollo de sistemas

electrónicos. Desde 1960 el número de transistores de los circuitos integrados se ha

duplicado aproximadamente cada dos años. Gracias a esta ciencia es que los circuitos

integrados han ido evolucionando, claro ejemplo de ello se da en los microprocesadores

modernos, los cuales contienen más de 40 millones de transistores integrados en un solo

chip. Aunque a esto se le conoce como ULSI o ultra large scale integration, es claro que

esta se deriva de la VLSI. Todo este fenómeno fue predicho por la ley de Moore, la cual

se puede ver más claro en la figura 1. Gordon Moore expuso en 1965 que la densidad de

los circuitos integrados se duplicaba cada 18 meses.

Figura 2.2. Ilustración de la ley de Moore6.

Las metas de esta técnica, están en aumentar la confiabilidad y reducir el costo de

sistemas digitales complejos. El desafío está en diseñarlos en tiempos cada vez más

cortos. Para ello se cuenta con programas especialmente creados para la síntesis de los

modelos dados; claros ejemplos de la tecnología CAD (Computer Aided Design)7. Estos

6

7

http://www.ee.duke.edu/~krish/teaching/Lectures/Intro.pdf

Diseño asistido por computadora

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas

de Synopsys

6

tipos de programas son también ampliamente utilizados en otras ramas de la ingeniería.

En otras palabras, los programas tipo CAD ayudan, en el caso particular del diseño de

circuitos integrados, a pasar de un modelo lógico computacional, a un modelo estructural,

y por último llegar al diseño físico, como se ilustra en figura 2.

Figura 2.3. Inversor y sus perspectivas.

Para lograr este paso de un modelo a otro, se debe seguir una cierta jerarquía de diseño, la

cual se puede observar en la tabla 2.1.

Tabla 2.1 Pasos del diseño en VLSI.

1

Especificaciones del

↔ Concepto inicial.

sistema

2

Modelo abstracto en

↔ Diseño y verificación del sistema.

HDL

3

Síntesis Lógica

↔ Diseño y verificación de la lógica: Se convierte el diseño

a compuertas y modelos primitivos.

4

Diseño del circuito

↔ Diseño y verificación CMOS: Se transfiere el diseño a

través de transistores.

5

Diseño físico

↔ Diseño y verificación lógica en silicio: Se crean las

diferentes capas del silicio.

6

Manufactura

7

CHIP

↔ Producción en masa, prueba y ensamblaje

↔ Mercadeo

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas

de Synopsys

7

2.1.1 Métodos de diseño en VLSI

Hay varios estilos de diseño en VLSI, caracterizados esencialmente por el medio en que

se desarrollan. Tenemos los siguientes métodos:

a) Circuitos integrados programables

Principalmente se utilizan “Field Programmable Gate Arrays” (FPGA),

los chips FPGA contienen miles de compuertas lógicas sin conectar, las

cuales se conectan de acuerdo a la función que se requiere.

b) Circuitos integrados “semi custom8”

Entre estos destacan los “Gate Arrays” (GA), los cuales se producen con

máscaras estándar en obleas de silicio, pero sin definir sus conexiones

metálicas, las cuales se pueden definir luego para realizar la función

requerida por el chip.

c) Circuitos integrados “full custom9”

En este método destacan dos tendencias:

•

Diseño a base de celdas estándar: Este método se basa en la

realización de máscaras nuevas a partir de librerías de celdas ya

establecidas y caracterizadas.

•

Diseño completo: A diferencia del anterior, en este se parte de

cero, caracterizando las celdas que se van a requerir para la

realización del circuito.

8

9

Diseño usando máscaras estándar

Diseño total, incluyendo el diseño de las máscaras

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas

de Synopsys

8

Figura 2.4. Visualización de los métodos de diseño en VLSI10.

En las síntesis de la CPUCR anteriores, se ha utilizado el método empleando los FPGA,

esto debido a su bajo costo de producción así como su disponibilidad.

Este proyecto está enfocado en la síntesis lógica de la CPUCR utilizando el método del

diseño total del circuito a nivel de transistores a base de celdas estándar usando la librería

AMI 0.5 micrones. Por esto, es importante estudiar con más detalle este punto. De aquí

en adelante, se toma como válido el diseño en Verilog propuesto por el profesor Roberto

Rodríguez, el cual a su vez está basado en el diseño descrito por Roberto Arellano y José

Antonio Cruz.

2.1.2 Síntesis lógica

La síntesis lógica provee un enlace entre un HDL (Verilog o VHDL) y una descripción

del circuito en términos de una librería basada en una tecnología específica de manera

análoga a como un compilador C enlaza al código C con el lenguaje de máquina.

10

http://lsiwww.epfl.ch/LSI2001/teaching/webcourse/ch01/Figure-1.26.mini.gif

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas

de Synopsys

9

El lenguaje HDL no fue diseñado para su uso con herramientas de síntesis lógica, sino

que fue diseñado como un lenguaje de simulación y el VHDL como un lenguaje de

documentación y descripción. Estos lenguajes fueron desarrollados a principios de los

ochenta, mucho antes de la comercialización de los programas de síntesis lógica. Debido

a que estos formatos se han expandido hacia la síntesis, y no sólo a la simulación, el

conjunto de instrucciones sintetizables de un HDL es más bien un subconjunto del total

de instrucciones simulables. Además, no existe un estándar acerca de las instrucciones

que son sintetizables, por lo tanto, cada sintetizador define ese subconjunto, por lo que

todos los sintetizadores son ligeramente diferentes.

Para realizar la síntesis lógica de un sistema, primero un diseñador debe crear un modelo

por comportamiento del sistema. Puede ser una máquina de estados como en la CPUCR,

en HDL, el cual no contiene ninguna referencia acerca de la lógica de celdas a utilizar en

la síntesis del mismo.

Una vez que este modelo en HDL está completo, con sus

respectivas pruebas, se requieren dos herramientas: un sintetizador lógico (software y

documentación), para nuestro caso usamos herramientas de Synopsys, y una librería de

celdas, que en este caso sería la librería AMI 0.50 micrones. Una vez definidas estas

herramientas, se utiliza el sintetizador lógico para generar un netlist, que es un modelo

estructural, el cual contiene referencias a la lógica de celdas. Después de creado el

modelo, este se vuelve a simular y el resultado se debe comparar con la simulación

obtenida con la versión por comportamiento.

2.2 Herramientas de Synopsys

Uno de los principales fabricantes de programas para el diseño con semiconductores es

Synopsys Incorporated. Dentro de esta línea de programas se encuentran el Design

Compiler11 (DC) y el Design Analyzer12 (DA), los cuales han sido desarrollados para la

síntesis lógica del diseño.

11

12

Compilador del diseño

Analizador del diseño

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 10

de Synopsys

El DC, traduce el modelo por comportamiento en HDL a una visualización a nivel de

compuertas y posteriormente de transistores. Una vez con este nuevo modelo, el DC

permite hacer optimizaciones de temporización, de potencia, de área y de las rutas de

datos. Todo esto se puede observar en el flujo de diseño de la figura 2.4. Además, se

utilizan diferentes librerías de tecnologías de transistores de acuerdo a las

especificaciones que se requieran.

Esto permite el cambio de un mismo diseño a

diferentes tecnologías con tan sólo variar la librería.

Figura 2.5. Design Compiler dentro del flujo de diseño13.

El Design Analyzer, es la interfaz gráfica para muchas de las herramientas de síntesis de

Synopsys, entre ellas el Design Compiler. Gracias a esto, Design Analyzer tiene las

siguientes características14:

a. Dar valores de variable de sistema como el nombre de la biblioteca de

tecnología.

13

14

http://www.synopsys.com

Synopsys online documentation. Volume 1

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 11

de Synopsys

b. Leer y escribir diseños en múltiples formatos como EDIF, PLA, Verilog y

VHDL.

c. Elegir constantes y atributos gráficos en diseños, celdas, pines, buses y relojes.

d. Trabajar con diseños jerárquicos:

o Ver y moverse a través de las jerarquías.

o Ver diseños y subdiseños como cajas negras con puertos con

etiquetados.

o Agrupar gráficamente celdas y subdiseños.

e. Sintetizar circuitos digitales:

o Definir las condiciones de operación de los circuitos.

o Sintetizar circuitos jerárquicos, manteniendo las fronteras del diseño y

subdiseño mientras se hacen optimizaciones globales.

o Extraer máquinas de estado finitas de la lógica secuencial, definir

orden y codificaciones del estado, hacer optimizaciones de las

máquinas de estado y sintetizar un circuito secuencial equivalente.

f. Generar, ver y dibujar esquemáticos.

g. Mostrar la temporización de todos los elementos.

h. Resaltar rutas en esquemáticos.

i. Generar una variedad de reportes.

2.2.1 Librerías de celdas

Tal y como se ha mencionado anteriormente, las librerías de celdas son parte fundamental

a la hora de la síntesis del modelo del sistema. Estas consisten en familias de celdas, por

ejemplo compuertas NAND, inversores, NOR, o más complicadas como Flip-Flops, todas

debidamente caracterizadas y relacionadas con algún proceso de fabricación, esto con el

fin de acelerar el proceso de diseño de un circuito integrado.

Entre las principales propiedades descritas en los modelos de las celdas se encuentran:

•

La función que realizan (NAND, NOR, NOT, etc.)

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 12

de Synopsys

•

Todo tipo de características de temporización, tales como retardos, tiempos de

subida, tiempos de bajada, etc.

•

Potencia (Estática y dinámica)

•

Capacitancias

•

Área

Además de estas propiedades, también podemos encontrar otras características en los

modelos:

•

Esquemáticos del circuito

•

Un icono para cada celda

•

Un modelo físico

Ahora bien, las librerías son llamadas de acuerdo a la compañía que hizo la

caracterización, así como al proceso al que está dirigida. Entonces, para este caso, la

librería AMI 0.5 significa que fue realizada por la compañía AMI Semiconductor para el

proceso de fabricación a 0.5 micrómetros (micrones), este último número es mejor

conocido como el doble de λ. Este número λ, indica la mitad de la distancia mínima entre

la fuente y el drenaje del transistor para la cual el fabricante garantiza que no habrá un

cortocircuito entre la fuente y el drenaje, en la figura 2.7 se ilustra esta distancia. En

otras palabras, este valor de 0.5 micrones, garantiza que la distancia eficaz entre la fuente

y el drenaje después del proceso de fabricación será mayor a cero. Esto pues, durante el

proceso de fabricación, el chip se ve envuelto en una serie de pasos que requieren altas

temperaturas, lo que produce un cambio físico en el material con que se hace el drenaje y

la fuente, como se detalla en la figura 2.8, donde la distancia eficaz está denotada como

Leff.. Para la figura 2.7:

λ = L/2

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 13

de Synopsys

Figura 2.6. Ilustración de un transistor NMOS15.

Figura 2.7. Ilustración de la Leff15.

Para poder tener una mejor idea de lo que se incluye en las librerías de celdas, se puede

observar en el anexo 1 la representación de la compuerta Flip-Flop tipo D en la librería

AMI 0.5.

Entre las principales características16 de esta librería se encuentran:

•

Voltaje de operación: 3 V, 5 V y 12 V

•

Soporta de 2 a 3 capas de metal

•

Utiliza polisilicio de alta resistencia

•

Abarca un promedio de 4200 compuertas por mm2

•

Puede operar de -55 a 125 °C de temperatura

Los archivos de la librería vienen en varios formatos, entre estos se encuentran los

archivos con extensión “.lef” el cual contiene información física de las compuertas

(dimensiones, área, materiales) y otro con extensión “.tlf” que contiene información más

específica de las características de funcionamiento de la tecnología.

El archivo de la librería con extensión “.db” es el que se utiliza a la hora de llamar a esta

desde el Design Analyzer.

15

16

http://www.ee.duke.edu/~krish/teaching/Lectures/MOS-theory-2004.pdf

http://www.amis.com/pdf/C5_process_spec.pdf

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 14

de Synopsys

CAPÍTULO 3: Guía para el uso de Design Analyzer en la

síntesis de circuitos integrados

3.1

Ventana del Design Analyzer

Como ya se ha mencionado antes, el Design Analyzer es la interfaz gráfica de varias

herramientas de Synopsys incluyendo al Design Compiler.

Figura 3.1. Ilustración de la ventana del Design Analyzer.

Para iniciar el Design Analyzer, primero se debe iniciar una interfaz gráfica para el

sistema operativo Linux. Una vez realizado este paso se puede iniciar el programa de dos

maneras:

•

Abrir una ventana de comandos y digitar “design_analyzer”

•

Se busca, por medio de un manejador de archivos, el directorio donde se

encuentra el archivo ejecutable de design analyzer, una vez encontrado,

ejecutarlo dando doble clic al mouse.

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 15

de Synopsys

Una vez que se ejecute el programa, se abrirá una ventana como la mostrada en la figura

3.1. La ventana principal del design analyzer consiste en una barra de menú, cuatro

botones de vista, dos botones de nivel, dos barras de movimiento, un área de texto y una

ventana.

3.1.1 Barra de menú

La barra de menú cuenta con ocho submenúes; los cuales contienen la mayoría de las

funciones del design analyzer con lo que se facilita el uso del programa.

Los submenúes se ilustran en la figura 3.2. Las funciones de cada submenú se describen

a continuación:

SETUP (Configuración)

•

Definir los caminos de búsqueda, las librerías asociadas.

•

Ajustar variables del sistema:

a. En este submenú se encuentran todas las variables del DA,

para activar o desactivar una variable se debe definir su

estado en true (verdadero) o false (falso).

b. Todas las variables tienen una definición por defecto,

algunas se encuentran en verdadero y otras en falso. Esto

para realizar síntesis básicas; cuando se requiera se pueden

modificar.

•

La ejecución de scripts.

•

Desplegar la ventana de comandos.

FILE (Archivo)

•

Leer archivos de descripción del diseño.

•

Analizar y elaborar archivos y diseños HDL.

•

Importar información física y de temporización de un cluster.

•

Salvar el diseño en distintos formatos.

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 16

de Synopsys

•

Salvar la información de las restricciones, temporización y configuración para

herramientas externas.

•

Dibujar diseños.

•

Salir del design analyzer.

EDIT (Editar)

•

Insertar almohadillas (pads) en diseños en FPGA.

•

Editar la jerarquía del diseño creando y modificando los subdiseños.

•

Unificar las instancias del diseño.

•

Remover todos los atributos y constantes.

•

Encontrar objetos en el diseño según su función, tales como puertos, celdas,

redes o pines.

VIEW (Vista)

•

Ver la jerarquía del diseño, sus símbolos mostrando los puertos y sus

esquemáticos.

•

Cambiar la vista del diseño.

•

Cambiar las hojas del diseño.

•

Crear una nueva ventana de vista.

•

Recrear y refrescar un esquemático.

ATTRIBUTES (Atributos)

•

Especificar los relojes y sus propiedades.

•

Especificar:

Retardos en la entrada y salida

Carga

Condiciones de operación

Carga de las conexiones

Rango de tiempo

Características varias

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 17

de Synopsys

•

Especificar constantes de diseño (metas) incluyendo área, potencia y

velocidad.

•

Caracterizar un subdiseño en el contexto del diseño actual.

•

Especificar opciones y directrices para las herramientas de síntesis del design

compiler.

ANALYSIS (Análisis)

•

Asociar al diseño actual.

•

Revisar los errores del diseño actual.

•

Actualizar las estimaciones de temporización usando el timing analyzer, el

cual es otro programa de Synopsys que viene incluido en el paquete.

•

Mostrar valores de temporización.

•

Resaltar los caminos (paths) máximo, mínimo y críticos.

•

Obtener diferentes tipos de reportes del diseño actual.

TOOLS (Herramientas)

•

Sintetizar y optimizar el diseño.

•

Crear y optimizar un diseño de una máquina de estados finita.

•

Crear y optimizar diseños en FPGA.

•

Añadir estructuras de prueba y obtener reportes de estas pruebas.

HELP (Ayuda)

•

Obtener descripciones de la funciones del design analyzer.

•

Ver documentación en línea.

Figura 3.2. Submenú de atributos resaltado17.

17

Material de referencia de Synopsys

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 18

de Synopsys

3.2 Síntesis de un nuevo proyecto

Una vez que se cuenta con un diseño en un lenguaje de descripción de hardware,

entonces se procede a utilizar al DA para la síntesis del mismo, para esto se pueden

seguir dos caminos:

•

Manual: Ejecutando paso a paso las instrucciones requeridas para la síntesis

de acuerdo a nuestro criterio. Este camino a su vez tiene dos posibilidades:

Utilizar las instrucciones que vienen dadas en los submenúes

del Design Analyzer.

•

Escribir las instrucciones una a una en la ventana de comandos.

Por medio de un script18: Elaborando un script con las instrucciones que

deseamos, al igual que se hace con la barra de comandos, sólo que este nos

queda para volverlo a correr ahorrando el tiempo de la ejecución paso a paso,

una y otra vez.

3.2.1 Síntesis manual

Como la utilización de los submenúes del DA con sus respectivas opciones requieren que

el usuario conozca la función de las instrucciones, se puede decir que si el usuario sabe

utilizar la ventana de comandos, podrá entender fácilmente los comandos que vienen en

los submenúes.

3.2.1.1 Ventana de comandos

Para la ejecución de instrucciones, se debe invocar a la ventana de comandos a través del

submenú SETUP en la barra de menú. Aparecerá una ventana idéntica a la de la figura

3.3. Sobre el cuadro que le sigue a la frase “design_analyzer >” es donde se escriben los

comandos a emplear.

Aparte de ejecutar los comandos, la ventana de comandos también despliega gran

cantidad de información relacionada con cada instrucción ejecutada. Esta información

queda almacenada en la ventana dando lugar a una bitácora de la síntesis. Entre esta

18

Script es un programa ejecutable con extensión “.scr”

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 19

de Synopsys

información destacan los mensajes de advertencia y error, los cuales vienen con una

breve descripción del problema seguida de una abreviatura con un número. Este código

permite buscar la violación incurrida en los discos de referencia de Synopsys.

Figura 3.3. Ventana de comandos.

El Design Analyzer cuenta con cientos de comandos y variables lo cual hace tedioso el

aprenderse la forma correcta del uso de cada uno, por esto, en el submenú “AYUDA”, en

la opción “Comandos”, el DA ofrece una guía de cada comando señalando su función,

sus opciones y su forma correcta de uso. Esta guía también está contenida en los discos

de referencia de Synopsys.

La mejor manera para llevar un diseño ordenado, es utilizando el esquema de la figura

3.4, en el cual se parte del modelo del sistema a sintetizar en alguno de los lenguajes de

descripción de hardware (HDL).

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 20

de Synopsys

Esquema para la

síntesis

Especificar las librerías

Leer el diseño

Definir el entorno

Definir las

restricciones

Optimizar el diseño

Analizar y resolver

los problemas de

diseño

Salvar la base de

datos del diseño

Figura 3.4. Esquema para la síntesis de un proyecto en el Design Analyzer.

3.2.1.2 Especificación de la librería

Una vez que se cuenta con el modelo HDL, el siguiente paso es especificar la tecnología

que vamos a emplear por medio de las librerías de celdas, para esto se utilizan las

siguientes instrucciones:

•

“link_library”: Especifica la librería a enlazar.

•

“target_library”: Especifica la librería de la tecnología a utilizar en el diseño.

•

“symbol_library”: Especifica la librería de los símbolos a utilizar en el

esquemático.

El DA, también da la opción de definir preferencias entre celdas que implementen la

misma función pertenecientes a una misma librería, esto se logra mediante el comando

“set_prefer” seguido de: (nombre de la librería)/(nombre de la celda).

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 21

de Synopsys

Cuando no se especifica alguna librería, el DA automáticamente interpreta que debe

utilizar una librería genérica (sin caracterizar), esta librería está ubicada en el mismo

programa.

Además, se debe definir un directorio de trabajo que actuará como librería del diseño a

realizar, para esto se emplea la instrucción “define_design_lib” seguida del nombre del

directorio y su ubicación.

3.2.1.3 Lectura del diseño

Durante la lectura, el DA lee el archivo HDL y lo traduce al formato “.db”,

almacenándolo en la memoria interna asociada al DC.

Para esto se utiliza el comando “read” seguido del formato a leer y por último el nombre

del archivo.

También se puede utilizar los comandos:

•

“analyze”: Analiza los archivos HDL y los almacena en el formato intermedio

para la descripción en HDL en la librería especificada.

•

“read_file”: Lee el diseño o librerías hacia la memoria interna del Design

Compiler.

•

“elaborate”: Construye un diseño desde el formato intermedio. Elabora el

esquemático.

Una vez leído el archivo, se puede definir un nombre para el diseño en ejecución, para

esto se emplea el comando “current_design” seguido del nombre del módulo de mayor

jerarquía dentro del archivo HDL.

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 22

de Synopsys

3.2.1.4 Definición del entorno

El entorno abarca todas aquellas variables que se encuentran fuera del diseño en sí, tales

como:

•

Carga que se va a suplir

•

Temperatura de operación

•

El tipo de proceso de fabricación

•

El voltaje de operación

Las últimas tres, se conocen como condiciones de operación; estas se pueden definir por

la instrucción “set_operation_conditions”.

Las condiciones de operación vienen en

librerías, por lo que el comando “set_operation_conditions” lo que hace es hacer un

enlace entre el diseño y la librería que contiene las condiciones.

Por ejemplo, si tenemos la librería:

“Operating_conditions (“BBB”) {

Process: 0.6;

Temperature: 20;

Voltage: 5.25;

}”

Luego, para implementar esta librería se emplearía el comando:

Set_operation_conditions BBB

Para definir las cargas en un puerto o red, se utiliza el comando “set_load” seguido del

valor de la carga y del nombre del puerto.

3.2.1.5 Definir las restricciones

Las restricciones son los límites que el diseñador fija como constantes para su diseño, tal

como puede ser una potencia máxima, un reloj mínimo o un área máxima.

Estas se pueden clasificar en dos grupos:

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 23

de Synopsys

•

Restricciones de reglas de diseño: en general, este tipo de restricciones son

aquellas restricciones específicas de la tecnología que deben ser alcanzadas

para que el diseño funcione correctamente.

Entre estas destacan la

capacitancia máxima, el máximo tiempo de transición y el máximo número de

salidas o “fanout” que puede alimentar. Para estas se utilizan los comandos

“set_max_transition”,

“set_max_capacitance”

y

“set_max_fanout”

respectivamente. Igualmente se utilizan los mismo comandos pero cambiando

max por min, en cuyo caso restringen los casos mínimos en vez de los

máximos.

•

Restricciones de optimización del diseño: estas restricciones reflejan metas de

diseño menos críticas que son deseables pero no cruciales para el

funcionamiento del diseño. Dentro de estas la principal es la definición del

reloj. Además se pueden contar los retardos de entrada (“set_input_delay”) y

salida

(“set_output_delay”), así como la optimización del área o

“set_max_area”.

El definir el máximo tiempo de transición permisible previene la posibilidad de

transiciones muy lentas en conexiones largas, lo cual produciría retardos mayores.

Para el reloj, comúnmente se utilizan los siguientes comandos:

•

“create_clock”: Sirve para crear un reloj, se utiliza create_clock nombre del

puerto –name nombre del reloj –period período del reloj en nanosegundos.

•

“set_dont_touch_network”: Se utiliza para que el compilador no modifique el

“fanout” de una red, esto con el fin de que no modifique la del reloj.

•

“set_clock_skew”: Se utiliza para definir las diferencias de temporización

entre varias “copias” de un mismo reloj, por ejemplo, “set_clock_skew –

rise_delay 1”, lo cual estaría definiendo la diferencia del retardo de subida del

reloj en un nanosegundo.

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 24

de Synopsys

3.2.1.5 Optimización del diseño

Para la optimización del diseño se utiliza la instrucción “compile”. Esta realiza una

síntesis a nivel de lógica y compuertas, a la vez que realiza una optimización del diseño

en ejecución basado en las restricciones definidas por el usuario. La compilación del DA

siempre, por regla, trata de dar el diseño más pequeño y rápido posible. Existen varias

banderas relacionadas con la función compile, entre ellas destacan:

•

-map_effort: Define el grado de esfuerzo del programa para realizar el arreglo

estructural del diseño, esta se puede definir como low (bajo), medium

(mediano) o high (alto).

•

-incremental_mapping: Especifica que sólo se hagan optimizaciones de forma

incremental.

Las partes del diseño que ya han sido optimizadas no se

modifican.

•

-ungroup_all: Une a todos los niveles de jerarquía en el diseño excepto a

aquellos que han sido protegidos por el atributo “dont_touch”.

Además del comando compile, hay otros comandos de uso menos frecuente que también

ayudan a optimizar un diseño desde otros puntos de vista. Un ejemplo de estos es el

comando “set_flatten” el cual reduce toda la red de lógica a una representación de suma

de productos de dos niveles (compuertas “Y” y “O”) al remover variables intermedias,

esto es lo que se conoce como aplanar al diseño.

3.2.1.6 Análisis y resolución de problemas de diseño

El Design Analyzer realiza una comprobación del diseño para asegurar que sea

consistente. Cuando el DA encuentra inconsistencias, estas se reflejan en mensajes de

advertencias o errores. Las advertencias son de carácter informativo y no necesariamente

indican problemas en el diseño, sin embargo, es muy recomendable su investigación para

saber el origen de la misma. Por otra parte, los mensajes de error señalan problemas

graves que impiden la compilación del diseño. Como se mencionó anteriormente, las

advertencias y los errores van seguidos de una abreviatura con el fin de buscar su

descripción en la referencia de Synopsys.

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 25

de Synopsys

Se utiliza el comando “check_design” normalmente sin más argumentos, pero también se

cuenta con algunas opciones para esta instrucción, tales como:

•

-no_warnings: esto indica que se supriman los mensajes de advertencias,

entonces sólo se muestran los mensajes de errores.

•

-summary: este argumento le indica al DA que muestre, en un solo mensaje,

un sumario de las advertencias, en vez de un mensaje por advertencia.

Además, también el DA genera varios reportes con el fin que el usuario obtenga toda la

información necesaria para el análisis del diseño. Para generar dichos reportes, se utiliza

el comando “report” seguido de una “_” y a continuación el tipo de reporte que se quiere,

por ejemplo report_area. El DA genera más de 30 tipos diferentes de reportes, los de

mayor relevancia son:

•

Area: Reporta el área total utilizada por todo el diseño. Además, también

reporta el número total de celdas, puertos y referencias usadas en el diseño.

Las referencias son las celdas de la librería utilizadas.

•

Power: Hace un reporte de la potencia tanto estática como dinámica del

diseño.

•

Cell: Reporta las celdas de la librería utilizadas en el diseño.

•

Timing: Señala el camino con la temporización más lenta y a su vez determina

el tiempo que dura algún dato desde que entra a esta hasta que sale.

•

Clock: Muestra todas las características del reloj del diseño.

•

Constraint: Reporta todas las restricciones definidas en el diseño.

Para que el DA guarde los reportes en archivos que se puedan leer, se debe hacer uso de

la siguiente sintaxis:

report_(tipo de reporte) > (nombre aleatorio del archivo).rep

El formato “.rep” indica que el archivo es un reporte, y es de fácil lectura en cualquier

programa editor de textos de Windows o Linux.

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 26

de Synopsys

3.2.1.7 Salvar la base de datos del diseño

Una vez que se llega a este punto, lo que se quiere es guardar la síntesis obtenida por la

herramienta. Para esto se utiliza el comando “write”, el cual escribe el netlist o el

esquemático del diseño en un archivo. El design analyzer soporta varios formatos, para

ello se puede observar la tabla 3.1.

El formato por defecto es el “.db”, el cual es un formato interno de Synopsys. Este

formato puede ser utilizado para ser usado en cualquier otra herramienta de Synopsys.

Tabla 3.1. Formatos aceptados por el Design Analyzer.

Formato

Descripción

Extensión

Database

Formato interno de base de datos de Synopsys

.db

EDIF

Formato de intercambio de diseño electrónico

.edif

Equation

Formato de ecuación de Synopsys

.eqn

LSI

Formato de netlist de la corporación LSI Logic

.NET

Mentor

Formato NETED de Mentor (sólo de escritura)

.neted

MIF

Formato intermedio de Mentor

.mif

PLA

Formato PLA de Berkeley

.pla

State table

Formato de tabla de estados de Synopsys

.st

TDL

Formato netlist del lenguaje de diseño Tegas

.tdl

Verilog

Lenguaje de descripción de hardware

.v

XNF

Formato de netlist de Xilinx

.xnf

VHDL

Lenguaje de descripción de hardware VHSIC

.vhdl

Existe cierto tipo de información que el DA por defecto no escribe en los archivos antes

citados.

Para definir ciertos parámetros sobre la información que se guarda en los

archivos tipo “v” o “vhdl”, se utilizan los comandos “verilogout_(argumento)” y

“vhdlout_(argumento)”. Entre los argumentos para los archivos “.v”, se encuentran:

•

Mostrar los pines sin conexión: “show_unconnected_pins”.

•

Mostrar los pines de poder: “show_power_pins”.

•

Mostrar los archivos incluidos en el diseño: “include_files”.

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 27

de Synopsys

•

Declarar las redes de tercer estado como “wire19” en lugar de “tr20i”:

“no_tri”.

3.2.2 Síntesis por medio de un script

Al tener un esquema básico para la síntesis de un diseño, en este se definen los comandos

generales a utilizar en la síntesis. Siguiendo este esquema, se puede editar un script que

contenga a estos comandos, el cual se puede ejecutar posteriormente en el Design

Analyzer.

La principal ventaja de este script radica en la reducción del tiempo necesario en la

digitación de los comandos para varias modificaciones de un mismo diseño; pues si se

requiere cambiar algún argumento de un comando, se cambia este en el script y se vuelve

a correr la síntesis en el DA, evitando así el tener que volver a digitar cada uno de los

comandos necesarios para la síntesis. Además, es una manera ordenada de llevar un

registro de las instrucciones ejecutadas en el DA, ya que aunque la ventana de comandos

lleva este registro, viene en forma desordenada, mientras que en el script todas las

instrucciones se encuentran fácilmente.

Es importante tener en cuenta que el design analyzer ejecuta al script de manera serial y

no en paralelo, esto quiere decir que las instrucciones son ejecutadas en el mismo orden

en el que se encuentran en el script. En el caso de la síntesis, esto es de gran relevancia,

pues, por ejemplo, no es lo mismo primero utilizar la función “compile” y luego definir el

reloj, que primero definir el reloj y luego hacer la compilación. Esto pues la compilación

trata de hacer la optimización del diseño con las restricciones dadas, así, si al ejecutar

“compile” no se tiene la restricción del reloj, esta no se optimiza.

La ejecución del script por parte del DA se realiza instrucción por instrucción, gracias a

esto, a la hora de presentarse errores, el DA interrumpe la ejecución del script y abre una

19

20

Esta declaración le asigna el atributo de cable a una señal en formato Verilog.

La declaración “tri” se refiere a un búfer de tercer estado en formato Verilog.

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 28

de Synopsys

pequeña ventana con el mensaje de “error”, seguido de una explicación del mismo, y a la

vez, le pregunta al usuario si desea continuar la ejecución del script. Así pues, queda a

discreción del usuario la gravedad del error. Las advertencias, al no ser tan críticas como

los errores, no tienen el mismo procedimiento, sino que estas aparecen en la ventana de

comandos en la bitácora de la síntesis que realiza el DA, tal como se explicó en la sección

3.2.1.1. A la hora de hacer un script, este debe hacerse siguiendo los pasos de la guía

dada en el esquema de la figura 3.4.

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 29

de Synopsys

CAPÍTULO 4: Síntesis de la CPUCR con el Design

Analyzer

Siguiendo los pasos sugeridos en el capítulo anterior, se trató de sintetizar el diseño por

comportamiento de la CPUCR dado por el profesor Roberto Rodríguez, con nombre

cpucr_rarr.v, el cual incluye a su vez al archivo Dec_Inst.v que define los valores de las

instrucciones de la CPUCR. Ambos archivos se encuentran en el apéndice F.

Para este fin se creó un archivo tipo script para luego ejecutarlo en el Design Analyzer y

poder hacer esta síntesis. El contenido de este archivo se puede observar claramente en el

apéndice A.

Para nuestro diseño, utilizamos como base un script suministrado por el profesor Enrique

Coen realizado por Johannes Grad, el cual se puede observar en el apéndice B.

A este último script, se le realizaron las siguientes modificaciones para adaptarlo a la

síntesis de nuestro diseño:

a) Se le agregó un reloj.

b) Se incrementó el esfuerzo de mapeo en la instrucción compile de medium

a high, para realizar una compilación más exhaustiva.

c) Se eliminaron las líneas para crear los pads del diseño, pues no se

requieren.

d) Para escribir el formato en lenguaje de hardware, se cambió el formato de

“.vh” a “.v” para facilitar la simulación en Verilogger21.

e) Se agregó el reporte de área.

f) Se eliminó el comando “quit”, pues este le indica al Design Analyzer que

se desea cerrar el programa, lo cual no es cierto, por lo que simplemente se

omitió este comando y el DA de forma automática deja de ejecutar el

script cuando ya no lee más instrucciones.

21

Verilogger es una herramienta de simulación de hardware de la compañía Synapticad.

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 30

de Synopsys

Se le agregó el reloj utilizando las siguientes instrucciones:

“create_clock CLK –name RELOJ –period 6

set_dont_touch_network RELOJ”

Para llegar al periodo de 6 nanosegundos mostrado, primero se realizaron pruebas

comenzando desde 1 nanosegundo y aumentando de uno en uno hasta llegar a 6, el cual

era el mínimo que cumplía con la meta de tiempo. Esto se hizo gracias a los reportes de

temporización, los cuales indican si el modelo sintetizado cumple con las expectativas de

tiempo.

Una vez llegado al resultado antes mencionado, se comprobó por medio de la hoja de

características de la tecnología dada por el fabricante22 que el reloj recomendado para

esta librería es de 6 nanosegundos.

4.1 Problemas en la síntesis de la CPUCR

Dentro de los problemas en la síntesis de la CPUCR, se incluyen los problemas que

impidieron una síntesis correcta del diseño, o sea, sin errores ni advertencias. Entre estos,

errores en el código que impiden la correcta interpretación del diseño por parte del

compilador.

Para los significados de las instrucciones propias de la CPUCR referirse al apéndice C.

El primer problema encontrado luego de realizar la primera síntesis fue la inferencia de

flip-flops genéricos por parte del compilador en el registro del estado presente llamado

“EstPresente”. El código de transferencia del registro de la máquina de estados, utilizada

en el modelo de la CPUCR que se suministró originalmente, se muestra a continuación:

22

http://www.amis.com/databooks/ami500xxxxREV_2.book.pdf

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 31

de Synopsys

“always @(negedge CLK or negedge RPS)

begin

if (!RPS)

EstPresente <= Estado_0;

else

EstPresente <= ProxEst;

end”

Esta forma de código infiere flip-flops tipo D de flanco negativo con reset asíncrono

activado en bajo por la señal de reposición (RPS). La librería AMI 0.5 con la que cuenta

el Departamento de Automática y Sistemas Digitales de la Escuela de Ingeniería Eléctrica

de la UCR, no cuenta con flip-flops con reset de ningún tipo. De hecho solo cuenta con

flip-flops tipo D comunes, activados por flanco sea positivo o negativo.

Para la solución de este problema, lo que se hizo fue cambiar el código para que el

compilador interpretara el registro de la máquina de estados como flip-flops D contenidos

en la librería, a expensas del cambio en el funcionamiento. Este cambio consistió en

quitar la señal RPS de la lista de sensitividad y de este modo generar un reset sincrónico.

El código modificado se simuló en Verilogger en su versión 7.2 para comprobar que el

diseño modificado se ajustara al funcionamiento del original. El resultado fue idéntico al

obtenido con el código original desde el principio, excepto que la señal de reposición

(RPS) debe mantener su señal válida por lo menos hasta que pase un flanco negativo del

reloj, quedando por lo tanto con reposición sincrónica.

Al realizar la síntesis del nuevo modelo con reset sincrónico, se generó un estructural

completo hecho con todas las celdas de la librería AMI 0.5. En la simulación del

comportamiento de éste se encontró que no se comporta como el conductual ya que

generaba errores de valores indeterminados, en todas sus salidas, a partir de cierto punto.

Además se obtuvieron ciertas advertencias, las cuales indican errores de sintaxis del

código de la CPUCR.

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 32

de Synopsys

Se presentaron advertencias con respecto a la directiva “//synopsys parallel_case”, esta

directiva afecta la forma como se genera la lógica para la declaración case. Una

declaración case genera la lógica de un decodificador de prioridad; al usar la directiva

“parallel_case“se fuerza al compilador HDL a generar una lógica de multiplexor. Se

dieron advertencias en los case donde se evalúa el registro RI, ya que para usar esta

directiva los branches23 del case deben ser mutuamente excluyentes y estos al parecer no

lo son. Esto se eliminó de varias formas:

1. Suprimiendo esta directiva del código.

2. Desactivando la variable “hdlin_check_user_parallel_case”. Ésta variable

lo que hace es que el compilador reconozca o no la directiva //synopsys

parallel_case.

3. Sustituyendo el case por una serie de “if-else” anidados. Esta forma es un

poco tediosa, pero el resultado es el mismo que en los case no paralelos.

También se generó otra advertencia en uno de los case que evalúa al registro RI, ubicado

en el Estado_2. Se dio el error “statement unreachable”24, la cual se da debido a un

pequeño error en el código pues en el mismo case se tenía repetidas dos instrucciones: la

de salto indirecto (JMPind) y la de salto a subrutina (JSRind). Al eliminar esta repetición

de instrucciones la advertencia desapareció.

Otra advertencia señalaba que la señal HALT debía ir dentro de la lista de sensitividad de

la lógica combinacional que cambia las señales de salida de control de la CPUCR. Esta

señal debía incorporarse a esta lista de sensitividad en el código del modelo por

comportamiento en Verilog de la siguiente forma:

“always @(EstPresente or INT or SDMA or WAIT or RI or S[2] or HALT)”

Con solo esta inclusión se logró eliminar este problema.

23

24

Ramas del case

Declaración inalcanzable

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 33

de Synopsys

Se generaron advertencias que indicaban que el DA había deshabilitado automáticamente

un arco de tiempo entre los pines de una celda (U6) para eliminar un lazo de tiempo.

Esto no genera ningún problema, y no afecta en nada la síntesis. Se puede decir que esta

advertencia es de carácter informativa.

Luego de cada uno de los cambios antes mencionados se procedió a simular en

Verilogger para comprobar el correcto funcionamiento de la lógica de la nueva versión

conductual, y en todos los casos no se presentó ningún cambio con respecto al

comportamiento original.

La realización de todas las pruebas en Verilogger se lograron gracias a la utilización de

los programas de prueba hechos por Ernesto Guevara Víquez en su proyecto

“Implementación de un ensamblador para la CPUCR en PERL”, los cuales se encuentran

en el anexo 2.

4.2 Problemas del código de la CPUCR conductual

Una vez que se logró una síntesis sin ningún error ni advertencia significativa que pudiera

afectar el comportamiento lógico del modelo estructural, se procedió a hacer las pruebas

respectivas al modelo estructural obtenido para poder comparar los resultados de ambos

modelos.

Al realizar las simulaciones, tanto del modelo conductual como del modelo estructural, se

presentó un nuevo problema, pues en algunos programas de prueba ambos modelos

fallaban, pues no coincidía el resultado de la simulación con las instrucciones dadas en el

programa. Por esto, se procedió a buscar algún otro modelo conductual de la CPUCR

con el fin de analizar posibles errores en el modelo conductual utilizado.

Se encontró un modelo conductual hecho por Roberto Arellano y José Cruz, por lo que se

procedió a la simulación y comparación entre ambos modelos conductuales,

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 34

de Synopsys

encontrándose un incongruencia entre los resultados, pues el modelo de Arellano y Cruz

si simulaba correctamente. Debido a esto, se revisó el código una vez más, pero no sólo

de manera que sintetizara bien, sino que funcionara toda la lógica.

Al revisar el código, se encontró que la instrucción STA no se encontraba en la lista de

instrucciones que contiene el case del Estado_2, del proceso de la máquina de estados.

Esto se reconoció porque en varios programas que utilizan dicha instrucción se daba una

oscilación en la salida de la señal HALT, lo cual indica que se tenía una instrucción no

reconocida, pues si esto se da, se va al estado 31, el cual pone a oscilar a la señal HALT.

Se corrigió el problema de comportamiento simplemente al incluir esta instrucción en la

lista, de esta forma el modelo conductual realizó los programas sin ningún problema.

Después de corregidos todos estos problemas se sintetizó un modelo estructural de la

CPUCR, el cual teóricamente debía funcionar, pero lamentablemente, aunque mejoró, no

mostró un comportamiento adecuado.

Los diagramas de tiempo de las pruebas

realizadas, el código conductual modificado y el código del modelo estructural obtenido

gracias al DA se muestran en el apéndice D, G y H respectivamente.

4.2.1 Descripción de los problemas en las simulaciones

Programa 1 y 2

Estos programas simulan bien, contienen instrucciones de tipo: inmediatas, relativas y de

control, no hay problemas con las instrucciones de salto condiconal, además no se hace

ninguna escritura a memoria ni a la pila.

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 35

de Synopsys

Figura 4.1. Simulación programa de prueba 1.

Figura 4.2. Simulación programa de prueba 2.

Programa 3

Después de una instrucción de PLS va a la pila pero carga un dato con algunos bits en

alta impedancia y otros en cero, después se pierde el procesador cuando se encuentra una

instrucción BVC.

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 36

de Synopsys

Figura 4.3. Simulación programa de prueba 3.

Programa 4

Al igual que el anterior se hace un PLS luego se va a la pila pero el dato en el bus de

datos tiene algunos bits en alta impedancia y el resto en cero. Se pierde cuando llega a

una instrucción BPL. Antes de esto se dan operaciones en las cuales se escribe en la

memoria con la instrucción PHA absoluto.

Figura 4.4. Simulación programa de prueba 4.

Programa 5

Al hacer un LDA absoluto se va a la dirección pero carga un dato con bits en alta

impedancia. Al hacer una AND absoluta el bus de datos también tiene bits en alta

impedancia. Finalmente el procesador se pierde al encontrar un BNE. Antes de esto se

dan operaciones en las cuales se escribe en la memoria con STA absoluto.

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 37

de Synopsys

Figura 4.5. Simulación programa de prueba 5.

Programa 6

Primero se da un LDA inmediato el cual tiene varios bits en alta impedancia, después el

procesador se pierde con un BNE. Antes de esto se dan operaciones en las cuales se

escribe en la memoria STA absoluto.

Figura 4.6. Simulación programa de prueba 6.

Programa 7

Similar al caso anterior.

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 38

de Synopsys

Figura 4.7. Simulación programa de prueba 7.

Programa 8

Con un LDA absoluto se va a la dirección y se obtiene un operando con bits en alta

impedancia. Luego con un STA indirecto cuando carga la parte alta de la dirección

efectiva el bus de datos esta en alta impedancia. Luego con un SUB absoluto va a la

dirección y finalmente se pierde con un BNE.

Figura 4.8. Simulación programa de prueba 8.

Programa 9

Similar al anterior, con un LDA indirecto que carga la parte alta de la dirección efectiva

con valores en alta impedancia.

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 39

de Synopsys

Figura 4.9. Simulación programa de prueba 9.

De este mismo modo se dieron errores similares en los programas restantes. Para mayor

claridad se puede consultar el apéndice D, en el cual aparecen los diagramas de

temporización obtenidos de la simulación de todos los programas.

4.3 Análisis de resultados

Después de preparar el script, con todos los comandos, restricciones y reportes, y tras

realizar la síntesis de la CPUCR, solucionando los problemas que se presentaron con el

código y las advertencias del DA, se realizaron las pruebas de simulación de la misma y

con estos resultados se hizo un análisis crítico del comportamiento que presentó el

modelo estructural sintetizado, así como de las posibles soluciones a los errores

generados.

Pudo notarse que hay cierto patrón de comportamiento en los programas. Si se da un

error con una instrucción que aparezca varias veces en un mismo programa, éste se repite

de forma idéntica.

Se notó que hay un fallo en la lógica que controla el bus de datos. Ya que en muchos

casos se presentan bits en alta impedancia al leer de este bus, cuando se dan instrucciones

de tipo absolutas e indirectas, o en aquellas en las cuales se varía al registro de status. Es

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 40

de Synopsys

como si se bloqueara el acceso a lo datos de memoria, dejando en alta impedancia ciertos

bits los cuales debieron tener un valor lógico de uno. Aún cuando se dio este tipo de

errores, no se perdió el curso de la lógica que calcula la próxima dirección, excepto

cuando se carga una dirección con datos con algunos bits en alta impedancia, caso en el

cual se dirige a una posición indeterminada para luego volver a la siguiente instrucción.

El procesador se perdió definitivamente (poniendo todas sus salidas en valores

indeterminados), cuando se encuentra alguna instrucción de salto condicional que causa

que la siguiente dirección sea indeterminada, provocando el colapso del proceso del

programa. Esto parece lógico ya que los saltos condicionales dependen de las banderas

del registro status, que a su vez dependen de la condición del acumulador, de modo que si

el acumulador tiene un valor indeterminado, al ser leído con algunos bits en alta

impedancia o en cero, se va a afectar el efecto de las instrucciones de salto.

Por otro lado se obtuvo el reporte de inferencia de dispositivos del DA, y se construyó la

tabla 4.1. Esta muestra todos los dispositivos que el compilador infirió a partir de la

síntesis, la bitácora completa obtenida se incluyó en el apéndice E. Estos nombres se

usan para declarar las celdas del modelo estructural, y se generan a partir de los nombres

dados a los registros de la versión conductual. Se notó que todos los registros inferidos

concuerdan con los utilizados en el proceso de transferencia de registros del código. Lo

mismo sucede con la inferencia de los buffers de tercer estado.

Además, no se generaron latches indeseados. De modo que la síntesis en este sentido

pudo considerarse como satisfactoria.

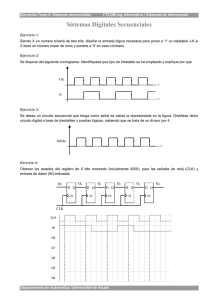

Tabla 4.1. Dispositivos inferidos por el Design Analyzer.

Nombre del registro

Tipo

Número de bits

Temp_reg

Flip-flop

1

LE_PA_reg

Flip-flop

1

P_reg

Flip-flop

8

PC_reg

Flip-flop

16

RI_reg

Flip-flop

8

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 41

de Synopsys

LE_reg

Flip-flop

1

RDR_tri_enable_reg Flip-flop

16

RDR_reg

Flip-flop

16

Temp1_reg

Flip-flop

1

TB_reg

Flip-flop

8

BUSPC_reg

Flip-flop

16

S_reg

Flip-flop

8

LE_S_reg

Flip-flop

1

A_reg

Flip-flop

8

LE_PB_reg

Flip-flop

1

LE_A_reg

Flip-flop

1

LE_tri_enable_reg

Flip-flop

1

EstPresente_reg

Flip-flop

5

BUSDAT_tri

Tri-State Buffer25 8

BUSDAT_tri2

Tri-State Buffer

8

BUSDAT_tri3

Tri-State Buffer

8

BUSDAT_tri4

Tri-State Buffer

8

CM_tri

Tri-State Buffer

1

M_tri

Tri-State Buffer

1

RDR_tri

Tri-State Buffer

16

LE_tri

Tri-State Buffer

1

4.3.1 Posibles problemas

Como se indicó anteriormente, la lógica de manejo y control del bus de datos está

fallando. Esto puede ser debido a que el compilador interpretó una lógica a partir del

código, la cual genera buffers de tercer estado que bloquean las lecturas de la memoria o

de la pila. La tabla 4.1 muestra los dispositivos que infirió el compilador al hacer la

síntesis. En ésta tabla se notó la presencia de cuatro buffers de tercer estado de ocho bits:

25

Buffer de tercer estado.

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 42

de Synopsys

BUSDAT_tri, BUSDAT_tri2, BUSDAT_tri3 y BUSDAT_tri4, los cuales como su

nombre lo indica tienen que ver con el manejo del bus de datos. Son cuatro debido a que

en el código se asignó al bus de datos los valores como se muestra a continuación:

“assign BUSDAT = LE_A ¿ 8’hzz:A;

assign BUSDAT = LE_S ¿ 8’hzz:S;

assign BUSDAT = LE_PB ¿ 8’hzz:BUSPC[7:0];

assign BUSDAT = LE_PA ? 8’hzz :BUSPC[15 :8] ;”

La cual es una forma válida de obtener buffers de tercer estado. Pero la forma que infiere

la lógica de tercer estado es con buffers sencillos, que son controlados con los registros:

LE_A, LE_S, LE_PB y LE_PA. La figura 4.10 muestra un ejemplo de la lógica inferida

con el comando assign para dos datos A y B controlados por SELA y SELB

respectivamente.

Figura 4.10. Lógica de tercer estado inferida con el comando assign.

En el caso de la lógica de la CPUCR los controladores de los buffers son registros que

cambian dependiendo del registro que está en el bus de datos.

Como los problemas de la simulación se presentan por bits en alta impedancia cuando

debían ser unos, la posible causa de esto puede ser la forma del código que controla el

BUS de datos. Hay un esquema de programación que permite que se infiera el registro

para la señal de control sin ponerlo explícitamente, esto se muestra en el siguiente

código:

module ff_3state (DATA, CLK, THREE_STATE, OUT1);

input DATA, CLK, THREE_STATE;

output OUT1;

Diciembre del 2004

IE-0502 Síntesis y optimización de la CPUCR en la librería AMI 0.5 micrones con herramientas 43

de Synopsys

reg OUT1;

always @ (posedge CLK) begin

if (THREE_STATE)

OUT1 = 1’bz;

else

OUT1 = DATA;

end

endmodule

De este modo se consigue la lógica de registro para el dato así como para el controlador

del buffer. El circuito inferido por el compilador se muestra en la figura 4.11.

Figura 4.11. Lógica de buffer de tercer estado con registros.

Se recomienda cambiar el código de la CPUCR de modo que se pueda inferir la lógica

de buffers con registros, para tratar de corregir los problemas de la síntesis. Esto se puede