Clase lab 2

Anuncio

LAB 2

Laboratorio de Sistemas Digitales

ELO212

Primer Semestre de 2008

Objetivos Generales

• Usar un osciloscopio de señal mixta

– sincronización, disparo, nivel de disparo, y

base de tiempo

•

•

•

•

Realizar un diseño digital

Aplicar prueba estática y dinámica

Usar parámetros y macros en Verilog.

Medir tiempos de retardo en componentes

Agilent 54621D

Sincronización (1)

Sincronización (2)

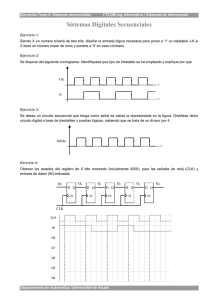

FlipFlop JK (1)

CLR’

J

K

Q(k+1)

Q’(k+1)

0

x

x

0

1

1

0

0

Q(k)

Q’(k)

1

1

0

1

0

1

0

1

0

1

1

1

1

Q’(k)

Q(k)

FlipFlop JK (2)

module flipflopJK(J, K, CLK, CLRn, Q, Qn);

input J, K, CLK, CLRn;

output Q, Qn;

reg Q, Qn;

always @(negedge CLRn or negedge CLK)

begin

if (!CLRn) begin Q <= 0; Qn <= 1; end

else

case ({J,K})

1: begin Q <= 0; Qn <= 1; end

...

default: begin Q <= Q; Qn <= Qn; end

endcase

end

endmodule

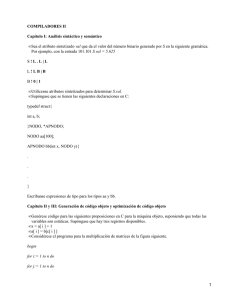

Contador (1)

CLK

CLR

QA

QB

QC

QD

Contador (2)

Contador M bits

module counter(CLK, CLR, Q);

parameter M = 3;

input CLK, CLR;

output reg [M:0] Q;

// fill in

endmodule

Circuito Activado por Cuentas

(1)

Cuenta:

Salida:

0

1

2

3

4

5

6

7

Circuito Activado por Cuentas

(2)

module actcuenta(x, w);

parameter M = 3;

parameter A = 3;

parameter B = 5;

input [0:M] x;

output w;

// fill in

endmodule

En el Laboratorio

•

•

Verificar (vía ModelSim) circuitos

diseñados en la parte previa

Medir retardos de compuertas

– FlipFlop JK

– Inversor 7404

•

Implementar el circuito activado por

cuentas

– Usar ecuaciones reducidas!!!

![Duración 2:00 h 1.- [3 puntos] Inicialmente el registro A del circuito](http://s2.studylib.es/store/data/006054581_1-5bf5edf798f4d3df94d79777115bdac4-300x300.png)