Sistemas con Microprocesadores I

Anuncio

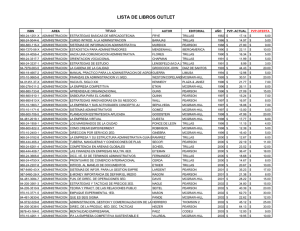

Sistemas con Microprocesadores I 1 2 3 Procesador Primitivo Micro-operaciones aritméticas Unidad aritmética Suma y resta aritmética en representación de punto fijo Suma y resta aritmética Números binarios con signo Representación gráfica binaria sin signo y con signo Substracción con números sin signo Sobreflujo en suma y resta con signo Ejemplo de sumas y restas con y sin signo Procesador Primitivo Unidad aritmética (continuación) Unidad aritmética y lógica Unidad de corrimiento La ALU 4 La instrucción: NOP 5 Laminillas complementarias Unidad aritmética y lógica Mauricio López V. (Ingenierı́a) Arquitectura Junio, 2016 1 / 96 Procesador Primitivo Micro-operaciones aritméticas Micro-operaciones aritméticas Se continúa con la implementación de la ALU (Unidad Aritmética y Lógica) Primero se realiza un resumen de las señales de control y de la arquitectura para generar micro-operaciones de transferencia entre registros generales entrada y salida de datos por los puertos unidad lógica y carga inmediata Mauricio López V. (Ingenierı́a) Arquitectura Junio, 2016 2 / 96 Procesador Primitivo Micro-operaciones aritméticas Resumen de arquitectura Slo2 , Slo1 y Slo0 : Selectores de función lógica Sci : Selector de carga inmediata o de registro del arreglo de registros Sf r : Selector de salida de función lógica o la establecida por Sci Mauricio López V. (Ingenierı́a) Arquitectura Junio, 2016 3 / 96 Procesador Primitivo Micro-operaciones aritméticas Resumen de arquitectura Sep : Habilitador de salida a puertos Sin : Selector de entrada externa al arreglo de registros generales Ser : Habilitador de carga a los registros generales Mauricio López V. (Ingenierı́a) Arquitectura Junio, 2016 4 / 96 Procesador Primitivo Micro-operaciones aritméticas Resumen de arquitectura DR: Habilita escritura en registro destino (tres bits) SRA: Establece el registro A fuente (tres bits) SRB: Establece el registro B fuente (tres bits) Mauricio López V. (Ingenierı́a) Arquitectura Junio, 2016 5 / 96 Procesador Primitivo Micro-operaciones aritméticas Micro-operaciones aritméticas Se procede a implementar la Unidad Aritmética Micro-operaciones aritméticas: A más complemento a uno de B Suma: F ← A + B F ← A + B Complemento a dos de B Substarcción F ← A + B + 1 F ← B + 1 Transferir B: Incremento de B: F ← B F ← B + 1 Suma con acarreo Decremento de B F ← A + B + 1 Mauricio López V. (Ingenierı́a) F ← B + (−1) Arquitectura Junio, 2016 6 / 96 Procesador Primitivo Micro-operaciones aritméticas Micro-operaciones aritméticas Suma: F ← A + B El circuito lógico que forma una suma aritmética de dos bits y su acarreo es llamado un sumador completo (FA: Full-Adder ). Circuito sumador completo (donde Ai y Bi son las entradas): Ci : acarreo de entrada. Ci+1 : acarreo de salida. Mauricio López V. (Ingenierı́a) Arquitectura Junio, 2016 7 / 96 Procesador Primitivo Micro-operaciones aritméticas Micro-operaciones aritméticas Sumador completo de 4 bits: Diagrama a bloques del sumador paralelo binario: Mauricio López V. (Ingenierı́a) Arquitectura Junio, 2016 8 / 96 Procesador Primitivo Micro-operaciones aritméticas Micro-operaciones aritméticas Operaciones aritméticas con un sumador paralelo: Nota: No se incluye el acarreo de salida, se entiende que está presente. Mauricio López V. (Ingenierı́a) Arquitectura Junio, 2016 9 / 96 Procesador Primitivo Micro-operaciones aritméticas Micro-operaciones aritméticas Operaciones aritméticas con un sumador paralelo (continúa): Nota: No se incluye el acarreo de salida, se entiende que está presente. Mauricio López V. (Ingenierı́a) Arquitectura Junio, 2016 10 / 96 Procesador Primitivo Micro-operaciones aritméticas Micro-operaciones aritméticas Para llevar a cabo las micro-operaciones de suma de A y B, y la suma de A y el complemento a uno de B (B), se requiere incluir hardware al sumador paralelo (sin acarreo). Mauricio López V. (Ingenierı́a) Arquitectura Junio, 2016 11 / 96 Procesador Primitivo Micro-operaciones aritméticas Micro-operaciones aritméticas Para llevar a cabo las micro-operaciones de substracción de A y B, y la suma de A y B mas uno, se requiere incluir hardware al sumador paralelo (con acarreo) Mauricio López V. (Ingenierı́a) Arquitectura Junio, 2016 12 / 96 Procesador Primitivo Micro-operaciones aritméticas Micro-operaciones aritméticas Para llevar a cabo las micro-operaciones de transferencia de B, y el incremento de B, se requiere incluir hardware al sumador paralelo (sin y con acarreo) Mauricio López V. (Ingenierı́a) Arquitectura Junio, 2016 13 / 96 Procesador Primitivo Micro-operaciones aritméticas Micro-operaciones aritméticas Para llevar a cabo las micro-operaciones de complemento a dos de B, y el decremento de B, se requiere incluir hardware al sumador paralelo (con y sin acarreo) Mauricio López V. (Ingenierı́a) Arquitectura Junio, 2016 14 / 96 Procesador Primitivo Unidad aritmética Unidad aritmética Srg : Selector de registro A. Sun : Selector de unos. Scu : Selector de complemento a uno. Sac : Selector de acarreo. Mauricio López V. (Ingenierı́a) Arquitectura Junio, 2016 15 / 96 Procesador Primitivo Unidad aritmética Unidad aritmética Otra operación que se desea que lleve a cabo la unidad aritmética: La salida del sumador/restador con resultado todos en unos Mauricio López V. (Ingenierı́a) Arquitectura Junio, 2016 16 / 96 Procesador Primitivo Unidad aritmética Unidad aritmética Srg : Selector de registro A. Sun : Selector de unos. Sbp : Selector de registro B. Scu : Selector de complemento a uno. Sac : Selector de acarreo. Mauricio López V. (Ingenierı́a) Arquitectura Junio, 2016 17 / 96 Procesador Primitivo Unidad aritmética Unidad aritmética Srg : Selector de registro A. Sun : Selector de unos. Sbp : Selector de registro B. Scu : Selector de complemento a uno. Sac : Selector de acarreo. Mauricio López V. (Ingenierı́a) Arquitectura Junio, 2016 18 / 96 Procesador Primitivo Unidad aritmética Unidad aritmética Se incluye un decodificador con señales de control Sar2 , Sar1 y Sar0 Mauricio López V. (Ingenierı́a) Arquitectura Junio, 2016 19 / 96 Procesador Primitivo Unidad aritmética Unidad aritmética El análisis de las banderas de estado (acarreo, C, y sobreflujo, V ) se realiza a continuación. Mauricio López V. (Ingenierı́a) Arquitectura Junio, 2016 20 / 96 Suma y resta aritmética en representación de punto fijo Suma y resta aritmética Suma y Resta aritmética Suma aritmética: Resta aritmética (con préstamo): Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 21 / 96 Suma y resta aritmética en representación de punto fijo Números binarios con signo Números binarios con signo Los números utilizados en el cálculos cientı́fico se designan por un signo, éste muestra si el número es positivo o negativo El signo de un número puede considerarse como un conjunto de dos elementos más y menos Para representar un número binario con signo en un registro se necesitan n + 1 bits n bit para el número un bit para el signo (posición más a la izquierda del registro) Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 22 / 96 Suma y resta aritmética en representación de punto fijo Números binarios con signo Números binarios con signo Cuando un número binario es positivo, el signo se representa por un 0 y el resto del número como la magnitud del número binario Ejemplo (+9): 0 0001001 Cuando un número binario es negativo, el signo se representa por un 1 y el resto del número puede representarse por una de las siguientes maneras: La representación de magnitud con signo La representación del complemento a uno con signo La representación del complemento a dos con signo Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 23 / 96 Suma y resta aritmética en representación de punto fijo Números binarios con signo Números binarios con signo Cuando un número binario es positivo, el signo se representa por un 0 y el resto del número como la magnitud del número binario Ejemplo (+9): 0 0001001 Cuando un número binario es negativo, el signo se representa por un 1 y el resto del número puede representarse por una de las siguientes maneras: La representación de magnitud con signo Ejemplo (−9): 1 0001001 La representación del complemento a uno con signo Ejemplo (−9): 1 1110110 La representación del complemento a dos con signo Ejemplo (−9): 1 1110111 Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 23 / 96 Suma y resta aritmética en representación de punto fijo Números binarios con signo Números binarios con signo Cuando un número binario es positivo, el signo se representa por un 0 y el resto del número como la magnitud del número binario Ejemplo (+9): 0 0001001 Cuando un número binario es negativo, el signo se representa por un 1 y el resto del número puede representarse por una de las siguientes maneras: La representación de magnitud con signo Ejemplo (−9): 1 0001001 La representación del complemento a uno con signo Ejemplo (−9): 1 1110110 La representación del complemento a dos con signo Ejemplo (−9): 1 1110111 Note que la cadena de bits 11001 (para 4 bits y su signo) representa el equivalente binario: 25 cuando se considera un número sin signo −9 cuando se considera un número con signo (representación de magnitud con signo) Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 23 / 96 Suma y resta aritmética en representación de punto fijo Números binarios con signo Números binarios con signo Cuando un número binario es positivo, el signo se representa por un 0 y el resto del número como la magnitud del número binario Ejemplo (+9): 0 0001001 Cuando un número binario es negativo, el signo se representa por un 1 y el resto del número puede representarse por una de las siguientes maneras: La representación de magnitud con signo Ejemplo (−9): 1 0001001 La representación del complemento a uno con signo Ejemplo (−9): 1 1110110 La representación del complemento a dos con signo Ejemplo (−9): 1 1110111 Note que la cadena de bits 11001 (para 4 bits y su signo) representa el equivalente binario: 25 cuando se considera un número sin signo −9 cuando se considera un número con signo (representación de magnitud con signo) Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 23 / 96 Suma y resta aritmética en representación de punto fijo Números binarios con signo Ejemplos del complemento a dos de números binarios de 8 bits Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 24 / 96 Suma y resta aritmética en representación de punto fijo Números binarios con signo Suma y resta con representación de magnitud con signo Operaciones con la representación de magnitud con signo Ejemplo: Suma de +23 y −35 1. Al de la magnitud mayor restarle el de magnitud menor 2. Utilizar el signo del número más grande como el signo del resultado +23 + (−35) = −(35 − 23) = −12 Las operaciones con la representación de magnitud con signo requieren: Comparar sus signos si los dos signos son los mismos, se suman las magnitudes si los signos no son los mismos, se compara la magnitud relativa de los números y se le resta al mayor el valor menor determinar el signo del resultado Un hardware con una larga secuencia de decisiones de control ası́ como circuitos que puedan comparar, sumar y restar números Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 25 / 96 Suma y resta aritmética en representación de punto fijo Números binarios con signo Suma y resta con representación de magnitud con signo Operaciones con la representación de magnitud con signo Ejemplo: Suma de +23 y −35 1. Al de la magnitud mayor restarle el de magnitud menor 2. Utilizar el signo del número más grande como el signo del resultado +23 + (−35) = −(35 − 23) = −12 Las operaciones con la representación de magnitud con signo requieren: Comparar sus signos si los dos signos son los mismos, se suman las magnitudes si los signos no son los mismos, se compara la magnitud relativa de los números y se le resta al mayor el valor menor determinar el signo del resultado Un hardware con una larga secuencia de decisiones de control ası́ como circuitos que puedan comparar, sumar y restar números Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 25 / 96 Suma y resta aritmética en representación de punto fijo Números binarios con signo Suma y resta con representación del complemento a dos con signo Una expresión binaria de m = n + 1 bits, en una representación del complemento a dos con signo, abarca el intervalo de valores de −(2m−1 ) a +(2m−1 − 1). Para un registro de 4 bits Si x ≥ 0 (sin signo), x ∈ [0 . . . 15] Si x ≥ 0 (con signo), x ∈ [0 . . . 7] Si x < 0 (con signo), x ∈ [−8 . . . − 1] Para un registro de 8 bits Si x ≥ 0 (sin signo), x ∈ [0 . . . 255] Si x ≥ 0 (con signo), x ∈ [0 . . . 127] Si x < 0 (con signo), x ∈ [−128 . . . − 1] Comparando: Mientras que una expresión binaria de m bits sin signo abarca el intervalo de valores de 0 a +(2m − 1). Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 26 / 96 Suma y resta aritmética en representación de punto fijo Representación gráfica binaria sin signo y con signo Representación gráfica sin signo y con signo (complemento a 2), 4 bits Expresión binaria de 4 bits: Sin signo: Mauricio López V. (Ingenierı́a) Con signo: Sistema numérico Junio, 2016 27 / 96 Suma y resta aritmética en representación de punto fijo Representación gráfica binaria sin signo y con signo Representación gráfica con signo (complemento a 2), para 5 bits Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 28 / 96 Suma y resta aritmética en representación de punto fijo Representación gráfica binaria sin signo y con signo Suma binaria de punto fijo sin signo (4 bits): Sumando 4 + 3 Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 29 / 96 Suma y resta aritmética en representación de punto fijo Representación gráfica binaria sin signo y con signo Suma binaria de punto fijo sin signo (4 bits): Sumando 4 + 5 El resultado siempre es correcto mientras la suma no exceda el intervalo de valores del sistema numérico: x ∈ [0 . . . 15] Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 30 / 96 Suma y resta aritmética en representación de punto fijo Representación gráfica binaria sin signo y con signo Resta binaria con signo (4 bits): 7 - 5 (Suma: 7 + 11) La suma de dos números con signo con números negativos representados en complemento a 2 se obtiene de la suma de los dos números (1110 = 10112 ) Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 31 / 96 Suma y resta aritmética en representación de punto fijo Representación gráfica binaria sin signo y con signo Resta binaria con signo (4 bits): 7 - 8 (Suma: 7 + 8) El resultado siempre es correcto mientras la suma no exceda el intervalo de valores del sistema numérico: x ∈ [−8 . . . −1, 0 . . . 7] Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 32 / 96 Suma y resta aritmética en representación de punto fijo Representación gráfica binaria sin signo y con signo Resta binaria de punto fijo con signo (4 bits) resta 7 7 7 7 7 7 7 - 1 2 3 4 5 6 7 suma equivalente 7 + 15 7 + 14 7 + 13 7 + 12 7 + 11 7 + 10 7+9 Mauricio López V. (Ingenierı́a) debido a que -1 ⇔ 15 -2 ⇔ 14 -3 ⇔ 13 -4 ⇔ 12 -5 ⇔ 11 -6 ⇔ 10 -7 ⇔ 9 Sistema numérico Junio, 2016 33 / 96 Suma y resta aritmética en representación de punto fijo Representación gráfica binaria sin signo y con signo Resta binaria de punto fijo con signo (4 bits) resta 7 7 7 7 7 7 7 - 1 2 3 4 5 6 7 suma equivalente 7 + 15 7 + 14 7 + 13 7 + 12 7 + 11 7 + 10 7+9 Mauricio López V. (Ingenierı́a) debido a que -1 ⇔ 15 -2 ⇔ 14 -3 ⇔ 13 -4 ⇔ 12 -5 ⇔ 11 -6 ⇔ 10 -7 ⇔ 9 Sistema numérico Junio, 2016 34 / 96 Suma y resta aritmética en representación de punto fijo Substracción con números sin signo Substracción binaria con números sin signo La substracción binaria sin signo: juega un papel importante en computación y en el diseño de la arquitectura de una computadora es utilizada para comparar dos números, permitiendo tomas de decisiones, con la posibilidad de crear micro-instrucciones de salto Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 35 / 96 Suma y resta aritmética en representación de punto fijo Substracción con números sin signo Substracción binaria con números sin signo La substracción de dos números sin signo de n-dı́gitos, M − N , en binario puede llevarse a cabo como sigue: Sumar el complemento a dos del substraendo N al minuendo M Si M > N , la suma origina un acarreo final. Se descarta el acarreo final, produciendo el resultado M − N Si M < N , la suma no origina un acarreo final y el resultado es el complemento a dos de M − N colocando un signo menos en el resultado, −(N − M ) Si el hardware incluye un bit de acarreo (carry, C) se puede preguntar por éste para saber cuál de los dos números es mayor (M − N ): Si el carry es uno, C = 1, M > N , resultado positivo Si el carry es cero, C = 0, M < N , resultado negativo Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 36 / 96 Suma y resta aritmética en representación de punto fijo Substracción con números sin signo Substracción binaria con números sin signo La substracción de dos números sin signo de n-dı́gitos, M − N , en binario puede llevarse a cabo como sigue: Sumar el complemento a dos del substraendo N al minuendo M Si M > N , la suma origina un acarreo final. Se descarta el acarreo final, produciendo el resultado M − N Si M < N , la suma no origina un acarreo final y el resultado es el complemento a dos de M − N colocando un signo menos en el resultado, −(N − M ) Si el hardware incluye un bit de acarreo (carry, C) se puede preguntar por éste para saber cuál de los dos números es mayor (M − N ): Si el carry es uno, C = 1, M > N , resultado positivo Si el carry es cero, C = 0, M < N , resultado negativo Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 36 / 96 Suma y resta aritmética en representación de punto fijo Sobreflujo en suma y resta con signo Sobreflujo en suma y resta con signo Si una operación de suma produce un resultado que excede el intervalo de valores del sistema numérico, este resultado es incorrecto y se dice que hay un sobreflujo (para 4 bits x ∈ [−8 . . . −1, 0 . . . 7]) Ejemplos de resultados incorrectos La computadora debe detectar y señalar la ocurrencia de un sobreflujo La suma de dos números con diferente signo nunca puede producir sobreflujo Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 37 / 96 Suma y resta aritmética en representación de punto fijo Sobreflujo en suma y resta con signo Suma sin sobreflujo con signo Ejemplos de suma que no produce sobrefljo La computador necesita el mismo hardware para la suma y resta con singo y sin signo El usuario decide cuándo los números son con signo o sin signo El usuario debe interpretar el resultado de la suma o de la resta Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 38 / 96 Suma y resta aritmética en representación de punto fijo Sobreflujo en suma y resta con signo Detección del sobreflujo en suma o resta con signo La condición de sobreflujo se detecta al comparar el acarreo de entrada de la posición del bit de signo y el acarreo de salida de la posición del bit de signo Si estos dos acarreos son diferentes, ha ocurrido un sobreflujo Si estos dos acarreos son iguales, no ha ocurrido un sobreflujo Circuito: Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 39 / 96 Suma y resta aritmética en representación de punto fijo Ejemplo de sumas y restas con y sin signo Suma de dos números binarios de punto fijo (4 bits) Ejemplo: Lleve a cabo las operaciones mostradas en la siguiente tabla, indique si se produce (para números binarios de 4 bits): un sobreflujo para la suma o resta sin signo (C) un sobreflujo para la suma o resta con signo (V) un resultado igual a cero (Z) Operation 2+2 4+4 12 + 12 8+8 7−7 Mauricio López V. (Ingenierı́a) C V Z Sistema numérico Junio, 2016 40 / 96 Suma y resta aritmética en representación de punto fijo Ejemplo de sumas y restas con y sin signo Suma de dos números binarios de punto fijo (4 bits) Resultado de las banderas C, V y Z después de llevar a cabo las operaciones: Operation 2+2 4+4 12 + 12 8+8 7−7 C 0 0 1 1 1 V 0 1 0 1 0 Z 0 0 0 1 1 prof prof prof prof prof cont Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 41 / 96 Suma y resta aritmética en representación de punto fijo (sin signo) Mauricio López V. (Ingenierı́a) Ejemplo de sumas y restas con y sin signo 2 + 2 Sistema numérico C= 0yZ= 0 Junio, 2016 42 / 96 Suma y resta aritmética en representación de punto fijo (con signo) Ejemplo de sumas y restas con y sin signo 2 + 2 <===> 2 + 2 C = 0, V = 0 y Z = 0 ret Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 43 / 96 Suma y resta aritmética en representación de punto fijo (sin signo) Mauricio López V. (Ingenierı́a) Ejemplo de sumas y restas con y sin signo 4 + 4 Sistema numérico C= 0yZ= 0 Junio, 2016 44 / 96 Suma y resta aritmética en representación de punto fijo (con signo) Ejemplo de sumas y restas con y sin signo 4 + 4 <===> 4 + 4 C = 0, V = 1 y Z = 0 ret Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 45 / 96 Suma y resta aritmética en representación de punto fijo (sin signo) Mauricio López V. (Ingenierı́a) Ejemplo de sumas y restas con y sin signo 12 + 12 Sistema numérico C= 1yZ= 0 Junio, 2016 46 / 96 Suma y resta aritmética en representación de punto fijo (con signo) Ejemplo de sumas y restas con y sin signo −4 + −4 <===> 12 + 12 C = 1, V = 0 y Z = 0 ret Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 47 / 96 Suma y resta aritmética en representación de punto fijo (sin signo) Mauricio López V. (Ingenierı́a) Ejemplo de sumas y restas con y sin signo 8 + 8 Sistema numérico C= 1yZ= 1 Junio, 2016 48 / 96 Suma y resta aritmética en representación de punto fijo (con signo) Ejemplo de sumas y restas con y sin signo −8 + −8 <===> 8 + 8 C = 1, V = 1 y Z = 1 ret Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 49 / 96 Suma y resta aritmética en representación de punto fijo (sin signo) Mauricio López V. (Ingenierı́a) Ejemplo de sumas y restas con y sin signo 7 − 7 Sistema numérico C= 1yZ= 1 Junio, 2016 50 / 96 Suma y resta aritmética en representación de punto fijo (con signo) Ejemplo de sumas y restas con y sin signo 7 + −7 <===> 7 + 9 C = 1, V = 0 y Z = 1 ret Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 51 / 96 Procesador Primitivo Unidad aritmética (continuación) Unidad aritmética Se retoma la implementación de la arquitectura del procesador primitivo al incluir la unidad aritmética con micro-operaciones: Incremento, IN C Pone todos a unos, SET Decremento, DEC Suma, ADD (los dos operandos son contenidos de los registros generales) y ADDI (uno de los operandos es una constante) Substracción SU B (los dos operandos son contenidos de los registros generales) y SU BI (uno de los operandos es una constante) Transferencia Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 52 / 96 Procesador Primitivo Unidad aritmética (continuación) Unidad aritmética Srg : Selector de registro A. Sun : Selector de unos. Sbp : Selector de registro B. Scu : Selector de complemento a uno. Sac : Selector de acarreo. Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 53 / 96 Procesador Primitivo Unidad aritmética (continuación) Unidad aritmética Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 54 / 96 Procesador Primitivo Unidad aritmética (continuación) Unidad aritmética Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 55 / 96 Procesador Primitivo Unidad aritmética (continuación) Unidad aritmética Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 56 / 96 Procesador Primitivo Unidad aritmética (continuación) Unidad aritmética Arquitectura de operaciones aritméticas Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 57 / 96 Procesador Primitivo Unidad aritmética (continuación) Unidad aritmética Arquitectura de operaciones lógicas Mauricio López V. (Ingenierı́a) Sistema numérico Junio, 2016 58 / 96 Procesador Primitivo Unidad aritmética y lógica Unidad aritmética y Unidad lógica Una sola micro-operación se puede realizar a la vez Se ejecuta una micro-operación lógica o una aritmética, pero no ambas al mismo tiempo Se pueden utilizar las mismas señales de control para la unidad aritmética y para la unidad lógica Estas señales de control pueden ser definidas como Sal2 (para controlar Sar2 y Slo2 ), Sal1 (para controlar Sar1 y Slo1 ) y Sal0 (para controlar Sar0 y Slo0 ) Se incluye otra señal de control, Stu , para seleccionar la salida del tipo de función (micro-operación aritmética o lógica) Mauricio López V. (Ingenierı́a) ALU Junio, 2016 59 / 96 Procesador Primitivo Unidad aritmética y lógica Unidad aritmética y Unidad lógica Sal2 , Sal1 y Sal0 : Selectores del tipo de micro-operación (aritmética y lógica) Stu : Selector del tipo de función (micro-operación aritmética o lógica) Mauricio López V. (Ingenierı́a) ALU Junio, 2016 60 / 96 Procesador Primitivo Unidad aritmética y lógica Unidad aritmética y Unidad lógica Mauricio López V. (Ingenierı́a) ALU Junio, 2016 61 / 96 Procesador Primitivo Unidad aritmética y lógica Unidad aritmética y Unidad lógica El bloque de la unidad aritmética/lógica permite transferir una de sus entradas a la salida (en particular B ó K), por lo que no requiere el multiplexor controlado por la señal de control Sf r . Mauricio López V. (Ingenierı́a) ALU Junio, 2016 62 / 96 Procesador Primitivo Unidad aritmética y lógica Unidad aritmética y Unidad lógica Ahora se determina la tabla de verdad para las señales de control a partir del código de operación. Mauricio López V. (Ingenierı́a) ALU Junio, 2016 63 / 96 Procesador Primitivo Unidad aritmética y lógica Unidad aritmética y Unidad lógica Ser = 1 para micro-operaciones cuyo resultado se almacena en el arreglo de registros generales y Ser = 0 en otros casos. Mauricio López V. (Ingenierı́a) ALU Junio, 2016 64 / 96 Procesador Primitivo Unidad aritmética y lógica Unidad aritmética y Unidad lógica Sep = 1 para micro-operaciones de transferencia con puertos de salida y Sep = 0 en otros casos. Mauricio López V. (Ingenierı́a) ALU Junio, 2016 65 / 96 Procesador Primitivo Unidad aritmética y lógica Unidad aritmética y Unidad lógica Sin = 1 para micro-operaciones de transferencia con puertos de entrada, no importa el valor de Sin cuando Sep = 0 y Sin = 0 en otros casos. Mauricio López V. (Ingenierı́a) ALU Junio, 2016 66 / 96 Procesador Primitivo Unidad aritmética y lógica Unidad aritmética y Unidad lógica Sci = 1 para micro-operaciones que involucren un valor de carga inmediata, Sci = 0 en micro-operaciones que involucren al registro fuente SRB, y en los otros casos no importa el valor de Sci (incluyen CLR, COM y SET ). Mauricio López V. (Ingenierı́a) ALU Junio, 2016 67 / 96 Procesador Primitivo Unidad aritmética y lógica Unidad aritmética y Unidad lógica De la tabla de verdad de las micro-operaciones aritméticas y lógicas Se obtiene (vea la siguiente lamina) Mauricio López V. (Ingenierı́a) ALU Junio, 2016 68 / 96 Procesador Primitivo Unidad aritmética y lógica Unidad aritmética y Unidad lógica Mauricio López V. (Ingenierı́a) ALU Junio, 2016 69 / 96 Procesador Primitivo Unidad aritmética y lógica Unidad aritmética y Unidad lógica Sal2 , Sal1 , Sal0 y Stu tienen los valores de la instrucción T ransf er, cuando se requiere que el operando controlado por la señal Sci no se vea alterado por la unidad aritmética/lógica, y no importan sus valores para los casos restantes. Mauricio López V. (Ingenierı́a) ALU Junio, 2016 70 / 96 Procesador Primitivo Unidad aritmética y lógica Unidad aritmética y Unidad lógica Mauricio López V. (Ingenierı́a) ALU Junio, 2016 71 / 96 Procesador Primitivo Unidad aritmética y lógica Unidad aritmética y Unidad lógica DR: Habilita escritura en registro destino (tres bits) SRA: Establece el registro A fuente (tres bits) SRB: Establece el registro B fuente (tres bits) Mauricio López V. (Ingenierı́a) ALU Junio, 2016 72 / 96 Procesador Primitivo Unidad aritmética y lógica Unidad aritmética y Unidad lógica Ejercicio 16: Se desea desarrollar un programa que primero capture un dato presente en el puerto de entrada F. Una vez capturado el dato extraiga los bits del nibble bajo y súmele el valor 30h. Para hacerlo, primero aplique una máscara al dato capturado del puerto para mantener sin alterar los bits del nibble bajo. Para finalizar decremente en una unidad el resultado anterior y muéstrelo en los LED conectados en el puerto de salida B. infor La solución debe considerar los siguientes puntos: El pseudocódigo El diagrama de flujo El programa utilizando mnemónicos El diagrama del contenido de la memoria en binario y en hexadecimal Mauricio López V. (Ingenierı́a) ALU Junio, 2016 73 / 96 Procesador Primitivo Unidad de corrimiento Unidad de corrimiento (4 bits): izquierda y derecha Ssh : Selector del tipo de corrimiento (derecha o izquierda; un bit) Sdt : Selector de dato (un bit) Sstc : Selector para involucrar al carry (dos bits) La condición 2 en Sstc no modifica el valor del carry, permaneciendo con su valor original Mauricio López V. (Ingenierı́a) ALU Junio, 2016 74 / 96 Procesador Primitivo Unidad de corrimiento Unidad de corrimiento (4 bits): izquierda y derecha dere Mauricio López V. (Ingenierı́a) izqui ALU cont Junio, 2016 75 / 96 Procesador Primitivo Unidad de corrimiento Unidad de corrimiento (4 bits): derecha Después: Antes: Mauricio López V. (Ingenierı́a) ALU Junio, 2016 76 / 96 Procesador Primitivo Unidad de corrimiento Unidad de corrimiento (4 bits): derecha con carry Después: Antes: ret Mauricio López V. (Ingenierı́a) ALU Junio, 2016 77 / 96 Procesador Primitivo Unidad de corrimiento Unidad de corrimiento (4 bits): izquierda Después: Antes: Mauricio López V. (Ingenierı́a) ALU Junio, 2016 78 / 96 Procesador Primitivo Unidad de corrimiento Unidad de corrimiento (4 bits): izquierda con carry Después: Antes: ret Mauricio López V. (Ingenierı́a) ALU Junio, 2016 79 / 96 Procesador Primitivo Unidad de corrimiento Unidad de corrimiento Mauricio López V. (Ingenierı́a) ALU Junio, 2016 80 / 96 Procesador Primitivo Unidad de corrimiento Unidad de corrimiento Mauricio López V. (Ingenierı́a) ALU Junio, 2016 81 / 96 Procesador Primitivo La ALU Unidad aritmética/lógica y de corrimiento Sshf : Selector de unidad de corrimiento Mauricio López V. (Ingenierı́a) ALU Junio, 2016 82 / 96 Procesador Primitivo La ALU Unidad aritmética/lógica y de corrimiento Mauricio López V. (Ingenierı́a) ALU Junio, 2016 83 / 96 Procesador Primitivo La ALU Unidad aritmética/lógica y de corrimiento Mauricio López V. (Ingenierı́a) ALU Junio, 2016 84 / 96 Procesador Primitivo La ALU Unidad aritmética/lógica y de corrimiento Mauricio López V. (Ingenierı́a) ALU Junio, 2016 85 / 96 Procesador Primitivo La ALU Unidad aritmética/lógica y de corrimiento Ahora se determina la tabla de verdad para las señales de control a partir del código de operación. Mauricio López V. (Ingenierı́a) ALU Junio, 2016 86 / 96 Procesador Primitivo La ALU Unidad aritmética/lógica y de corrimiento Para ello, considere que: Ser = 1 para micro-operaciones cuyo resultado se almacena en el arreglo de registros generales y Ser = 0 en otros casos. Sep = 1 para micro-operaciones de transferencia con puertos de salida y Sep = 0 en otros casos. Sin = 1 para micro-operaciones de transferencia con puertos de entrada, no importa el valor de Sin cuando Sep = 0 y Sin = 0 en otros casos. Sci = 1 para micro-operaciones que involucren un valor de carga inmediata, Sci = 0 en micro-operaciones que involucren al registro fuente SRB, y en los otros casos no importa el valor de Sci (incluyen CLR, COM , SET , SHR, SHRC, SHL ySHLC). Sal2 , Sal1 , Sal0 y Stu tienen los valores de la instrucción T ransf er, cuando se requiere que el operando controlado por la señal Sci no se vea alterado por la unidad aritmética/lógica. Sshf = 1 para micro-operaciones de corrimiento, Sci = 0 para micro-operaciones que requieren que el operando controlado por la señal Sci no se vea alterado por la unidad aritmética/lógica (M OV , OU T y LODI) y micro-operaciones aritméticas y lógicas, y en los otros casos no importa el valor de Sci (IN ). Mauricio López V. (Ingenierı́a) ALU Junio, 2016 87 / 96 Procesador Primitivo La ALU Unidad aritmética/lógica y de corrimiento Además, de las dos siguientes tablas de verdad Mauricio López V. (Ingenierı́a) ALU Junio, 2016 88 / 96 Procesador Primitivo La ALU Unidad aritmética/lógica y de corrimiento Se obtiene (vea la siguiente lamina) Mauricio López V. (Ingenierı́a) ALU Junio, 2016 89 / 96 Procesador Primitivo La ALU Unidad aritmética/lógica y de corrimiento Mauricio López V. (Ingenierı́a) ALU Junio, 2016 90 / 96 Procesador Primitivo La ALU Unidad aritmética/lógica y de corrimiento Mauricio López V. (Ingenierı́a) ALU Junio, 2016 91 / 96 La instrucción: NOP La instrucción: NOP Una operación N OP se caracteriza por el hecho de que no modifica ninguno de los registros del sistema. Esta condición se cumple con el código de operación ′ 00000′ de la tabla anterior. Entonces se le asignará a este último código de operación la instrucción: N OP . Vea la siguiente lamina Mauricio López V. (Ingenierı́a) ALU Junio, 2016 92 / 96 La instrucción: NOP La instrucción: NOP Mauricio López V. (Ingenierı́a) ALU Junio, 2016 93 / 96 Laminillas complementarias Laminillas complementarias Laminillas complementarias Mauricio López V. (Ingenierı́a) Arquitectura Junio, 2016 94 / 96 Laminillas complementarias Unidad aritmética y lógica Unidad aritmética y Unidad lógica DR: Habilita escritura en registro destino (tres bits) SRA: Establece el registro A fuente (tres bits) SRB: Establece el registro B fuente (tres bits) Mauricio López V. (Ingenierı́a) Arquitectura Junio, 2016 95 / 96 Laminillas complementarias Unidad aritmética y lógica Unidad aritmética y Unidad lógica return Mauricio López V. (Ingenierı́a) Arquitectura Junio, 2016 96 / 96