UNIDAD 3 : Aritmética de las computadoras

Anuncio

UNIDAD 3: Aritmética de las computadoras.

3.1. Introducción

Hasta el momento hemos estudiado algunas métricas para la obtención del rendimiento

(segundos, ciclos, instrucciones). También estudiamos el concepto de abstracción y en

particular nos interesamos por la abstracción que vincula al hardware con el software de

mas bajo nivel, a esta abstracción le denominamos: Arquitectura del repertorio de

instrucciones o simplemente Arquitectura de Computadoras.

Ya repasamos el repertorio de instrucciones MIPS, que como observamos, es lo

suficientemente completo como para implementar cualquier programa.

En esta sección iniciaremos con la implementación del hardware, en particular en esta

unidad se revisará la aritmética de las computadoras para obtener una Unidad Aritmético

Lógica personalizada al repertorio de instrucciones previamente estudiando. Además

estudiaremos el mecanismo para realizar multiplicaciones y divisiones con base en nuestra

unidad aritmético lógica.

Finalmente daremos un repaso a la representación de los números en punto flotante y

revisaremos las operaciones de suma y producto en punto flotante. Esbozaremos el

hardware que realiza estas operaciones, sin entrar en detalles de la implementación

completa.

3.2. Números con signo y sin signo

Los humanos preferimos representar a los números en base 10, sin embargo para las

computadoras lo mas adecuado es utilizar el sistema binario (base 2).

Si para una secuencia de dígitos en cualquier base numérica, se quiere obtener su valor en

base 10, debe multiplicarse cada dígito por la base elevada a la posición del dígito dentro

del número, de manera que su valor sería

d x basei

donde i corresponde a la posición de un dígito dentro del número. La posición 0 es la que

está mas a la izquierda (menos significativa). Por ejemplo, si tenemos el número 1011dos, en

base 10 nos representa a:

(1 x 23) + (0 x 22) + (1 x 21) + (1 x 20) diez

= (1 x 8) + (0 x 4) + (1 x 2) + (1 x 1) diez

= 8 + 0 + 2 + 1 diez

= 11diez

Sin embargo los números en MIPS utilizan 32 bits, por lo que el número 1011dos, quedaría

representado como:

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12

11 10 9 8

7 6 5 4

3 2 1 0

0 0 0 0

0 0 0 0

0 0 0 0

1 0 1 1

0 0 0 0

0 0 0 0

0 0 0 0 0 0 0 0

(32 bits de ancho)

Los números los representamos colocando el menos significativo a la derecha (posición 0) y

al mas significativo a la izquierda (posición 31).

Como se utilizan 32 bits para representar un número, entonces podemos representar 232

números diferentes, desde el número 0 hasta el 232 – 1 (4, 294, 967, 295diez) :

0000

0000

0000

. .

1111

1111

1111

0000

0000

0000

. .

1111

1111

1111

0000

0000

0000

. .

1111

1111

1111

0000

0000

0000

. .

1111

1111

1111

0000

0000

0000

. .

1111

1111

1111

0000

0000

0000

. .

1111

1111

1111

0000

0000

0000

. .

1111

1111

1111

0000dos

0001dos

0010dos

. .

1101 dos

1110 dos

1111 dos

=

0diez

=

1diez

=

2diez

. .

= 4, 294, 967, 293diez

= 4, 294, 967, 294diez

= 4, 294, 967, 295diez

Es importante tener en mente que los patrones de bits contienen una representación de los

números, en realidad tenemos un conjunto infinito de números; solo que es necesario tener

una representación para poder operarlos aritméticamente a través de sumas, restas,

productos, etc. Puede ocurrir que el resultado de una operación no alcance en los 32 bits

dedicados a cada número, cuando eso ocurre, se generará una señal de sobreflujo

(overflow), y el sistema operativo o el programa determinarán lo que deben hacer.

Los programas de computadora realizan cálculos sobre números positivos y negativos, de

manera que necesitamos una representación que haga la distinción de los positivos de los

negativos.

Una solución obvia consistiría en dedicar uno de los bits para que determine el signo,

dejando los 31 bits restantes para la magnitud. A esta representación se le conoce como

magnitud y signo, tiene diferentes inconvenientes. En principio, a donde se colocaría el

signo, a la derecha o a la izquierda de la magnitud, existen las dos posibilidades. Luego, el

hardware que trabaja con números usando magnitud y signo, requiere de un paso extra para

la evaluación del signo y la determinación anticipada del signo del resultado. Finalmente,

se contaría con dos representaciones para el cero, lo cual se refleja en la programación, por

ejemplo en un ciclo repetitivo, si el ciclo termina cuando una variable alcanza el valor de

cero, será necesaria una doble comparación. Debido a estos inconvenientes, la idea de

representar a los números usando magnitud y signo ha sido descartada.

En la búsqueda de otras alternativas se utilizó el complemento de los números positivos

para obtener el correspondiente negativo (complemento 1), esta representación tiene la

ventaja de que la clasificación de los números es bastante simple, un número positivo

tendrá un cero en su bit mas significativo y un número negativo tendrá un uno. Además, al

sumar un número con su correspondiente negativo, se tendrá una cadena de 1’s que

corresponderá al 0 (0 negativo). Pero se mantiene la desventaja de contar con dos

representaciones para el cero.

La solución para obtener una representación coherente consiste en sumar 1 a la

representación de complemento a 1 (complemento 2), de manera que solo se tendrá una

representación para el cero, el bit mas significativo nos indicará el signo del número y la

simple operación de sumar un número con su correspondiente negativo nos producirá el

número 0.

Esta representación es la que actualmente usa la mayoría de computadoras, y funciona

correctamente, aunque no está balanceada, porque existe un número negativo más debido a

la presencia del cero. Con los 32 bits dedicados a la representación de cada número, la

representación en complemento a dos es:

0000

0000

0000

. .

0111

0111

0111

1000

10000

10000

. .

1111

1111

1111

0000

0000

0000

. .

1111

1111

1111

0000

0000

0000

. .

1111

1111

1111

0000

0000

0000

. .

1111

1111

1111

0000

0000

0000

. .

1111

1111

1111

0000

0000

0000

. .

1111

1111

1111

0000

0000

0000

. .

1111

1111

1111

0000

0000

0000

. .

1111

1111

1111

0000

0000

0000

. .

1111

1111

1111

0000

0000

0000

. .

1111

1111

1111

0000

0000

0000

. .

1111

1111

1111

0000

0000

0000

. .

1111

1111

1111

0000

0000

0000

. .

1111

1111

1111

0000dos

0001dos

0010dos

. .

1101dos

11110dos

1111dos

0000dos

0001dos

0010dos

. .

1101 dos

1110 dos

1111 dos

=

0diez

=

1diez

=

2diez

. .

= 2, 147, 483, 645diez

= 2, 147, 483, 646diez

= 2, 147, 483, 647diez

= - 2, 147, 483, 648diez

= - 2, 147, 483, 647diez

= - 2, 147, 483, 646diez

. .

=

- 3diez

=

- 2diez

=

- 1diez

La mitad de los números, del 0 al 2, 147, 483, 645diez (231 – 1), usa la representación

mostrada anteriormente (cuando no se había considerado el signo). El siguiente patrón

(1000. . .000dos) representa al número mas negativo (- 2, 147, 483, 648diez) y es seguido por

un conjunto decreciente de números negativos: - 2, 147, 483, 647diez (1000. . .0001 dos)

hasta el –1 (1111. . .1111 dos).

Esta representación no esta balanceada por que el número - 2, 147, 483, 648diez no tiene un

número positivo correspondiente. Este hecho llega a ser una preocupación de los

desarrolladores de software, en contraparte con la representación de magnitud y signo que

además preocupaba a los desarrolladores de hardware.

El hecho de que el bit mas significativo indique el signo del número, hace que este bit se

comporte como un auténtico bit de signo, de manera que si se quiere obtener el valor en

base 10 de cualquier número representado en complemento a 2, el bit de la posición 31 se

deberá multiplicar por –231 y los restantes 31 bits seguirán el mismo tratamiento que los

números sin signo (su valor lo obtendrán de acuerdo con su posición).

Ejemplo: Conversión de Binario a Decimal

¿Cuál es el valor decimal del siguiente número en complemento a 2?

1111 1111 1111 1111 1111 1111 1111 1100dos

Respuesta:

Considerando la posición de cada bit tenemos:

(1 x -231) + (1 x 230) + (1 x 229) + . . . + (1 x 22) + (0 x 21) + (0 x 20) diez

= -231 + 230 + 229 + . . . + 22 + 0 + 0diez

= - 2,147,483,648 + 2,147,483,644diez

= - 4diez

Cuando se manejan números en complemento a dos, puede generarse una señal de

sobreflujo si el signo del resultado de una operación no corresponde con el signo esperado,

por ejemplo, si sumamos dos números positivos relativamente grandes, si el resultado no se

puede representar en el conjunto de números positivos, éste tomará una representación que

corresponda a un número negativo.

En algunos casos, como en el manejo de direcciones de memoria, no es posible usar

números negativos, las direcciones de memoria inician en 0 y crecen hacia una dirección

mayor. Entonces, los programas en ocasiones manejarán variables que puedan tomar

valores positivos o negativos, y en otras ocasiones sólo se requerirán valores positivos. Para

hacer esa distinción, los lenguajes de programación incorporan modificadores a los tipos de

datos para que puedan ser tratadas adecuadamente; por ejemplo en el lenguaje C, el tipo int

es para tratar enteros con signo y el tipo unsigned int es para tratar números sin signo.

Las comparaciones tratan con esta dicotomía, si un número tiene un 1 en su bit mas

significativo y es tratado en complemento a 2, será un numero negativo y por lo tanto será

menor que todos aquellos que tengan 0 en su bit mas significativo. Pero si el mismo

número es interpretado como entero sin signo, será mayor que todos aquellos que tengan 0

en su bit mas significativo.

Estas situaciones deben resolverse a nivel de hardware, en el caso de MIPS se consideran

diferentes variantes de la instrucción slt (set on less than), tanto slt como slti trabajan con

enteros sin signo, pero sltu (set on less than unsigned) y sltiu (set on less than immediate

unsigned) trabajan con enteros sin signo.

Ejemplo: Comparación con signo y sin signo

Supongamos que el registro $s0 tiene el número binario

1111 1111 1111 1111 1111 1111 1111 1111dos

y que el registro $s1 tiene el número binario

0000 0000 0000 0000 0000 0000 0000 0001dos

¿Cuáles son los valores de los registros $t0 y $t1 después de las instrucciones?

slt

$t0, $s0, $s1

sltu

$t1, $s0, $s1

Respuesta:

Para la instrucciones slt los números se consideran en complemento 2, de manera que $s0

tiene un número negativo (-1), que es menor al número 1 contenido en $s1, por lo que $t0

tendrá 1.

Pero para la instrucciones sltu los números son tratados sin signo, entonces $s0 tiene al

número positivo 4, 294, 967, 295diez, que definitivamente es mayor que 1, entonces $t1

tendrá 0.

Cuando se trabaja en complemento a 2, para obtener la versión negativa (o positiva) a partir

de un número positivo (o negativo), la forma mas simple para hacerlo consiste en

complementar cada uno de los bits (cambiar 1’s por 0’s y 0’s por 1’s) y luego sumar 1. Esta

idea se justifica por el hecho de que cuando sumamos un número con su complemento

obtenemos una cadena de 32 unos (que representa al –1).

De manera que x + x’ = -1 que es equivalente a x + x’ + 1 = 0, de donde obtenemos

- x = x’ + 1

que nos indica que el negado de un número es igual al complemento del mismo mas 1.

Ejemplo: Negación.

Negar el 2diez y verificar el resultado negando –2diez

Respuesta:

2diez = 0000 0000 0000 0000 0000 0000 0000 0010dos

Para negarlo lo complementamos y luego le agregamos 1:

1111 1111 1111 1111 1111 1111 1111 1101 dos

+

1 dos

=

1111 1111 1111 1111 1111 1111 1111 1110 dos

=

- 2diez

En la otra dirección:

- 2diez =

1111 1111 1111 1111 1111 1111 1111 1110 dos

Primero lo complementamos y luego de agregamos 1:

0000 0000 0000 0000 0000 0000 0000 0001 dos

+

1 dos

=

0000 0000 0000 0000 0000 0000 0000 0010 dos

=

2diez

Otra idea que habrá que considerar durante la implementación es la siguiente, en el

repertorio estudiado se consideraron instrucciones que manejan constantes de 16 bits.

Cuando estas constantes son operadas por medio de la ALU con otro operando de 32 bits,

que ocurre con los 16 bits que completan a la constante, ¿Cuál debe ser su valor?

Si se trabajan números en complemento a 2, su valor dependerá del bit mas significativo de

la constante (el bit 15) si este bit es 0 no hay problema, se completa con 0’s y la magnitud

se conserva (los 0’s a la derecha no tienen valor), pero si se trata de un 1, al completar con

1’s, ¿también se conservará la magnitud?

Si, se conserva la magnitud por que al extender a 32 bits se debe seguir manteniendo el

hecho de que un número sumado a su complemento debe generar una cadena de 32 unos,

de manera que si en un número positivo se tiene una cantidad infinita de 0’s a su derecha,

en un número negativo se debe tener un número infinito de 1’s a su derecha.

Finalmente, en ocasiones resulta mas fácil utilizar al sistema octal o al hexadecimal para la

representación y manipulación de los números, esto por que la cantidad de símbolos

existentes en estas bases corresponde a una cantidad exacta de combinaciones de 3 y 4 bits

respectivamente. Las bases octal y hexadecimal pueden considerarse como una forma

abreviada de representar a los números en binario, cada dígito en octal corresponderá a 3

bits y cada dígito en hexadecimal tendrá una correspondencia de 4 bits. Y viceversa, por

cada 3 bits puede obtenerse un dígito octal y por cada 4 uno hexadecimal.

3.3.Suma y resta

Las sumas en binario se realizan de la misma manera en que las realizamos en base 10, es

decir, de derecha a izquierda se va sumando dígito a dígito y si se el resultado es mayor al

dígito mas grande (9 en base 10 y 1 en base 2), se produce un acarreo que debe sumarse en

el dígito siguiente.

Entonces, al sumar dos bits debe tomarse en cuenta un posible acarreo en la entrada o bien

la generación de un acarreo en la salida. En la tabla 3.1 se muestran todas las posibles

combinaciones que pueden ocurrir al sumar un dígito a con un dígito b, el resultado de la

suma se coloca en el dígito s, también se considera la presencia de un acarreo en la entrada

y la generación de un acarreo de salida.

a

0

0

0

0

1

1

1

1

b

0

0

1

1

0

0

1

1

cin

0

1

0

1

0

1

0

1

s

0

1

1

0

1

0

0

1

cout

0

0

0

1

0

1

1

1

Tabla 3.1 Comportamiento de la suma

Al sumar dos palabras de 32 bits, solo se va aplicando la tabla de derecha a izquierda, y los

acarreos generados se suman al siguiente bit mas significativo:

La resta también podría realizarse de derecha a izquierda, bit a bit, considerando que

algunas veces será necesario “tomar prestado un 1 del dígito mas significativo”, cuando el

minuendo es menor que el sustraendo. Sin embargo a nivel de hardware esto es mas díficil,

lo mas simple es obtener la versión negativa del número a restar, y después realizar una

suma.

Ejemplo: Suma y resta binaria.

Sumar 37diez + 45diez en binario y después restar 37diez de 45diez.

Respuesta:

+

=

0000 0000 0000 0000 0000 0000 0010 0101dos = 37diez

0000 0000 0000 0000 0000 0000 0010 1101dos = 45diez

0000 0000 0000 0000 0000 0000 0101 0010 dos = 82diez

Para la resta, emplearemos el complemento 2 de 37diez (para obtener – 37diez) y luego lo

sumaremos al 45diez :

+

1111 1111 1111 1111 1111 1111 1101 1010dos

1dos

1111 1111 1111 1111 1111 1111 1101 1011dos = - 37diez

+

0000 0000 0000 0000 0000 0000 0010 1101dos = 45diez

1111 1111 1111 1111 1111 1111 1101 1011dos = - 37diez

1 0000 0000 0000 0000 0000 0000 0000 1000dos = 8diez

El 1 que aparece mas a la izquierda se ignora, por que el resultado debe quedar en 32 bits,

no es un sobreflujo o desbordamiento.

Cuando se realizan sumas o restas, solo en algunos casos tiene sentido hablar de sobreflujo.

Sobre todo cuando se trabaja en complemento a 2, por ejemplo, si sumamos dos números

positivos grandes, esperamos que el resultado sea positivo, pero si la cantidad de bits no es

suficiente para la representación del resultado, entonces se desbordará hacia un número

negativo. En la tabla 3.2 se muestra un resumen de los casos en los que si se considera la

existencia de un sobreflujo.

Operación

Operando A

Operando B

A+B

A+B

A–B

A–B

0

<0

0

<0

0

<0

<0

0

Resultado

(Indicación de sobreflujo)

<0

0

<0

0

Tabla 3.2 Situaciones de sobreflujo

El diseñador de la máquina debe por lo tanto proporcionar una forma para ignorar el

sobreflujo en algunos casos y reconocerlo en otros. La solución para MIPS es contar con

dos clases de instrucciones aritméticas para reconocer estas dos posibilidades:

La suma (add), la suma inmediata (addi) y la resta (sub) producen una excepción si

ocurre un sobreflujo.

La suma sin signo (addu) , la suma inmediata sin signo (addiu) y la resta sin signo

(subu) no producen excepciones debidas a los sobreflujos.

Puesto que en el lenguaje C se ignoran los desbordamientos, los compiladores para MIPS

siempre generarán las versiones sin signo de las instrucciones aritméticas addu, addiu y

subu no importa el tipo de las variables. Los compiladores MIPS de Fortran, sin embargo,

seleccionan las instrucciones aritméticas apropiadas, dependiendo del tipo de operando.

Un sobreflujo en MIPS producirá una excepción, algunas veces también conocida como

interrupción en muchas computadoras. Una excepción o interrupción es esencialmente una

llamada a un procedimiento que no estaba proyectada. La dirección de la instrucción en la

que ocurrió el sobreflujo es almacenada en un registro, y se produce un salto a una

dirección predefinida para invocar al procedimiento encargado de manejar la excepción. La

dirección en la que ocurrió la excepción se salva de manera que sea posible continuar con

la ejecución del programa después de ejecutar algún código correctivo.

En MIPS se incluye a un registro llamado contador del programa para las excepciones

(EPC) el cual contendrá la dirección de la instrucción que ocasionó la excepción. También

se cuenta con la instrucción mover desde el control del sistema (mfc0) que sirve para copiar

el contenido del registro EPC en un registro de propósito general de manera que el software

tiene la opción de regresar a la instrucción infractora a través de un salto a registro.

3.4. Operaciones lógicas

Aunque las primeras computadoras se centralizaron sobre palabras completas, pronto llego

a ser claro que es útil operar sobre campos de bits dentro de una palabra o aún sobre los bits

individuales. Un ejemplo lo encontramos al manipular caracteres dentro de una palabra,

debido a que cada carácter utiliza ocho bits, se observa que se requiere de instrucciones por

medio de las cuales sea posible empaquetar y desempaquetar los bits dentro de las palabras.

Una clase de estas operaciones son los desplazamientos (shifts). Con ellos se mueven todos

los bits de una palabra a la izquierda o derecha, llenando los bits vacíos con 0s. Por

ejemplo, si el registro $s0 contiene

0000 0000 0000 0000 0000 0000 0000 1101dos

y una instrucción de un desplazamiento a la izquierda por ocho es ejecutada, el nuevo valor

que tomará esta palabra será

0000 0000 0000 0000 0000 1101 0000 0000dos

El dual de un desplazamiento a la izquierda es un desplazamiento hacia la derecha. En

MIPS las instrucciones para los desplazamientos son sll – desplazamiento lógico a la

izquierda ( shift left logical ) y srl – desplazamiento lógico a la derecha (shift right

logical). La instrucción para realizar la operación anterior, suponiendo que el resultado se

almacenará en el registro $t0, es

sll

$t0, $s0, 8

# reg $t0 = reg $s0 << 8 bits

En la sección 2.3 (Representación de instrucciones), para las instrucciones Tipo – R se

mencionó la existencia del campo shamt (shift amount) pero no consideramos su uso. Este

campo solo es utilizado por las instrucciones de desplazamientos e indica la cantidad de

desplazamiento. Para estas instrucciones el registro rs es ignorado y se llena con 0s, rt es el

registro que será desplazado y rd es el registro destino. La instrucción anterior tendría la

siguiente representación:

op

rs

rt

rd

shamt

0

0

16

8

8

El campo de funct debe tener 0 para sll y 2 para srl.

funct

0

Otras operaciones útiles son la AND y la OR, estas operaciones se aplican bit a bit.

La AND es comúnmente utilizada para aplicar una máscara a un registro, puesto que la

AND va a colocar un 1 en el bit resultante si los dos bits sobre los que se aplica tienen 1s.

La máscara se realiza colocando 1s en aquellas posiciones que se quiera dejar pasar, y 0s en

los bits que se van a eliminar (contendrán 0s).

Por ejemplo, si el registro $t0 contiene:

1010 0011 0011 1001 1100 1100 1110 1101dos

y si el registro $t1 contiene

0000 0000 1111 1111 1111 1111 0000 0000dos

Al realizar la operación:

and

$t2, $t1, $t0

El registro $t1 esta funcionando como una máscara que deja pasar los 16 bits intermedios y

oculta al resto. El resultado en $t2 será:

0000 0000 0011 1001 1100 1100 0000 0000dos

En el caso de la OR, en el resultado se obtendrá un 1 si alguno de los bits sobre los que se

aplica tiene 1. La operación:

or

$t2, $t1, $t0

dejará en $t2:

1010 0011 1111 1111 1111 1111 1110 1101dos

En la tabla 3.3 se muestran las operaciones lógicas y su correspondiente instrucción MIPS.

Debido a que las constantes también son utilizadas en operaciones lógicas, se incluyen

versiones inmediatas para la AND y la OR.

Operación Lógica

Desplazamiento a la izquierda

Desplazamiento a la derecha

AND bit a bit

OR bit a bit

Operador en C

<<

>>

&

|

Instrucción MIPS

sll

srl

and, andi

or, ori

Tabla 3.3 Las operaciones lógicas y sus correspondientes operaciones en C y MIPS

El lenguaje C permite definir campos de bits dentro de palabras, permitiendo empaquetar

diversos objetos dentro de una palabra para que exista compatibilidad con algunos

dispositivos I/O. Los campos pueden tener la longitud de un bit, y el compilador debe

colocarlos dentro palabras utilizando las operaciones lógicas: and, or, sll y srl.

Ejemplo: Campos de Bits.

El siguiente código C ubica tres campos dentro de una palabra etiquetada receiver: Un

campo de 1 bit denominado ready, un campo de un bit denominado enable, y un campo de

8 bits denominado receivedByte. Se copia receivedByte dentro de data, se ajusta ready a 0,

y se ajusta enable a 1.

int

data;

struct {

unsigned int ready:

unsigned int enable:

unsigned int receivedByte:

} receiver;

1;

1;

8;

...

data = receiver.receivedByte;

receiver.ready = 0;

receiver.enable = 1;

¿Cuál es el correspondiente código MIPS? Suponga que data y receiver están ubicados en

$s0 y $s1.

Respuesta:

C alinea los campos a la derecha:

31

.....

10

9

2

receivedByte

1

enable

0

ready

Primero se debe copiar el campo de 8 bits (receivedByte) a data y aislarlo:

slr

andi

$s0, $s1, 2

$s0, $s0, 0x00ff

Luego se realizan los ajustes:

andi $s1, $s1,0xfffe

ori

$s1, $s1,0x0002

# Se desplaza y copia en data

# Se usa una máscara que elimina la información

# no deseada

# Bit 0 ajustado a 0

# Bit 1 ajustado a 1

Las instrucciones addi y ori trabajan con números con signos, de manera que para poder

operar en una ALU de 32 bits, las constantes se extienden a 32 bits extendiendo el bit de

signo.

3.5. Construcción de una Unidad Aritmético-Lógica

La Unidad Aaritmético-Lógica (ALU) es la fuerza física de la computadora, el dispositivo

que realiza las operaciones aritméticas como la suma y resta; y operaciones lógicas como la

AND y OR. En esta sección construiremos una ALU basada en los 4 componentes

mostrados en la figura 3.1, los componentes enumerados con 1, 2 y 4 tienen dos entradas,

en ocasiones tal vez sea necesario ampliar el numero de entradas, por lo que habrá que

expandir la tabla del comportamiento.

Fig. 3.1 Los cuatro componentes en los que se fundamentará la construcción de la ALU

Debido a que MIPS trabaja con palabras de 32 bits, la ALU a construir deberá contar con

operandos de 32 bits, para ello primero se realizará el diseño de una ALU de 1 bit, para

después utilizar 32 bloques basados en esa ALU de 1 bit.

ALU de 1 Bit

Iniciemos con una unidad lógica que incluya las operaciones AND y OR, en la figura 3.2 se

muestra que para las entradas a y b es posible seleccionar una operación lógica por medio

de la entrada de operación en el multiplexor, si operación es igual a 0, en la salida

tendremos a AND b, pero si operación es igual con 1, la salida tendrá a OR b.

Fig. 3.2 Unidad lógica con AND y OR

La siguiente función a incluir es la suma. En la tabla 3.1 se mostró el comportamiento de un

sumador completo, de manera que el sumador lo podemos ver como un bloque con 3

entradas y dos salidas, como se muestra en la figura 3.3. En este bloque, tanto la salida sum

como la salida CarryOut se producen con dos circuitos combinacionales, revisaremos el

circuito correspondiente a CarryOut.

Fig. 3.3 Bloque sumador de 1 Bit.

La señal CarryOut es verdadera

mostrarlas en la tabla 3.4:

a

0

1

1

1

en 4 ocasiones, que tomaremos de la tabla 3.1, para

b

1

0

1

1

CarryIn

1

1

0

1

CarryOut

1

1

1

1

Tabla 3.4 Comportamiento de CarryOut

Utilizando el símbolo + para la operación lógica OR y el para la AND, se tienen que:

CarryOut = (bCarryIn) + (aCarryIn) + (ab) + (abCarryIn)

Si (abCarryIn) es verdadero, entonces todos los demás términos son verdaderos, de

manera que podemos olvidarnos de este término, que corresponde a la cuarta línea de la

tabla 3.4 para simplemente tener:

CarryOut = (bCarryIn) + (aCarryIn) + (ab)

Esta expresión requiere de una compuerta OR de tres entradas y 3 compuertas AND de dos

entradas, su implementación es:

Fig. 3.4 Hardware para la señal CarryOut del sumador de 1 bit

La expresión para la suma se puede obtener de la tabla 3.1 y es:

Sum = (ab’CarryIn’) + (a’bCarryIn’) + (a’b’CarryIn) + (abCarryIn)

Donde a’ es igual a NOT(a); la implementación del circuito para la suma es parte de la

tarea. Manejando al sumador como un bloque, se implementa a la ALU de 1 Bit, como se

muestra en la figura 3.5, la cual realiza las operaciones de AND, OR y ADD. El

multiplexor en figura 3.5 es de 3 entradas, de manera que requiere de dos líneas de

operación, de las cuales hasta el momento solo se utilizarán tres combinaciones.

Fig. 3.5 ALU de 1 bit, capaz de realizar las operaciones AND, OR y ADD.

ALU de 32 Bits

El bloque mostrado en la figura 3.5 puede repetirse 32 veces para la construcción de una

ALU de 32 bits, la señal de acarreo generada como salida en el bloque i va a corresponder

al acarreo de entrada en el bloque i + 1. Esta forma de conectar las señales de acarreo nos

produce un sumador poco eficiente conocido como Sumador de acarreo extendido (ripple

carry adder). Mas adelante mostraremos otra técnica en la que se buscará generar al

acarreo de manera mas rápida. Todos los bloques comparten las señales de operación.

Fig. 3.6 ALU de 32 bits, capaz de realizar las operaciones AND, OR y ADD.

La resta equivale a la suma con el negado del segundo operando, así es como el hardware

realiza las restas. De manera que para realizar una resta se sumará el complemento a 2 del

segundo operando. Para eso es necesario un inversor con el que se obtenga el complemento

y un multiplexor para seleccionar entre el operando o su complemento. En la figura 3.7 se

muestra al inversor que se agrega para obtener el complemento de b. Pero además es

necesario sumar 1, esto simplemente se hace colocando 1 al acarreo de entrada del bit

menos significativo.

Fig. 3.7 ALU de 1 bit, con la entrada Binvert se selecciona entre b y su complemento.

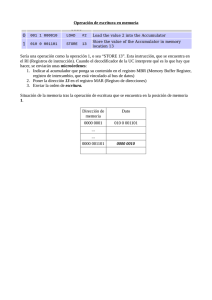

Otra instrucción importante que se incorpora en MIPS es slt (set on less than), esta

instrucción requiere de tres argumentos (slt reg1, reg2, reg3) y coloca un 1 en reg1 si

resulta que reg2 es menor que reg3. Reg1 = 1 si reg2 < reg3, que es equivalente a reg2 reg3 < 0. Lo que indica que una buena opción para la comparación consiste en realizar la

resta reg2 – reg3 y luego evaluar el resultado; en el resultado no importa la magnitud, lo

que importa es saber si es o no menor que 0, lo cual queda directamente determinado por el

bit mas significativo. Si el bit mas significativo tiene 1, el resultado de la operación slt

deberá ser 1, y si es 0 el resultado deberá ser 0.

La instrucción slt es otra operación mas para la ALU, de manera que el multiplexor de la

salida deberá incrementarse con una entrada mas. Estas ideas se muestran en la figura 3.8,

en donde el multiplexor se ha incrementado y la nueva entrada se incorpora desde fuera del

bloque de la ALU (la entrada etiquetada como less) (fig. 3.8 a). Sin embargo para el bit 31

(el más significativo) se genera una salida (etiquetada como set) que corresponde al bit de

signo del resultado (fig. 3.8 b). Esta salida se retroalimentará a la entrada less del bit 0,

mientras que para los otros bits (del 1 al 31), la entrada less estará conectada directamente a

tierra, para que mantenga un cero en forma permanente. En la figura 3.9 se muestra la

retroalimentación de set a la entrada less del bit menos significativo, así como los 0s en las

demás entradas less.

Otra idea interesante que se presenta en la figura 3.8 (b) es la presencia de la unidad de

detección de sobreflujo, el objetivo de este bloque es generar una bandera (señal de 1 bit)

que indique la existencia de un sobreflujo, para ello es necesario conocer los signos de los

operandos ( a31 y b31 ), el tipo de operación (Binvert), el signo del resultado y tal vez la

existencia de un acarreo en el bit mas significativo. El comportamiento de este circuito

puede basarse en el comportamiento de la suma descrito en la tabla 3.2.

Binvert

Operation

CarryIn

a

0

1

Result

b

0

2

1

Less

3

a.

CarryOut

Binvert

Operation

CarryIn

a

0

1

Result

b

0

2

1

Less

3

Set

Overflow

detection

Overflow

b.

Fig. 3.8 El valor del bit mas significativo se usará para la instrucción slt,

en a) se muestra la estructura de los 31 bits menos significativos y

en b) la estructura del bit mas significativo

En la figura 3.9 se muestra la conexión de las 32 ALUs de 1 bits, las primeras 31 tienen la

misma construcción, la última difiere un poco por la presencia de la unidad de detección de

sobreflujo y por que de ahí se toma la salida set que se retroalimenta al bit 0.

Binvert

CarryIn

a0

b0

CarryIn

ALU0

Less

CarryOut

a1

b1

0

CarryIn

ALU1

Less

CarryOut

a2

b2

0

CarryIn

ALU2

Less

CarryOut

Operation

Result0

Result1

Result2

CarryIn

a31

b31

0

CarryIn

ALU31

Less

Result31

Set

Overflow

Fig. 3.9 ALU de 32 Bits, capaz de realizar sumas, restas, AND, OR y slt.

También puede indicar la existencia de un sobreflujo.

El acarreo de entrada sólo se ocupa para las restas, y su comportamiento es el mismo que el

de la entrada Binvert, si la entrada Binvert tiene 1, indica que se realizará una resta, y para

la obtención correcta del complemento 2, debe sumarse 1. Por lo que la entrada CarriIn del

sumador de los bits menos significativos debe tener 1. Pero si la entrada de Binvert es 0, se

trata de una suma, y para que el resultado sea correcto, la entrada CarryIn deberá tener 0.

Por lo tanto, las entradas Binvert y CarryIn pueden conectarse en una sola, a la cual se

llamaremos Bnegado como se muestra en la figura 3.10.

También en la figura 3.10 se muestra la generación de la bandera de zero, la cual será

verdadera (contendrá 1) si el resultado de cualquier operación es igual a 0. La idea de la

generación de esta bandera es bastante simple, cuando las 32 salidas de las ALUs de 1 bit

tengan 0, la OR que las une producirá un 0 y por lo tanto el inversor que le sigue lo

transformará a 1. Pero si alguna de las salidas tiene un valor 1, la OR generará un 1 y el

inversor lo transformará a 0.

Fig. 3.10 ALU de 32 Bits, capaz de realizar sumas, restas, AND, OR y slt.

Con banderas de zero y de sobreflujo.

La ALU mostrada en la figura 3.10 tiene 3 líneas de control, si concatenamos a la entrada

Bnegado con las entradas de operación (poniendo a la entrada Bnegado como bit mas

significativo), el comportamiento de la ALU lo podemos resumir como se muestra en la

tabla 3.5.

Líneas de Control de la ALU

000

001

010

110

111

Función

And

Or

Suma

Resta

Slt

Tabla 3.5 Comportamiento de la ALU

La ALU la representaremos con su símbolo tradicional, como se muestra en la figura 3.11,

donde las entradas a y b son de 32 bits, la entrada ALU Operación es de 3 bits, la salida

Result es de 32 bits, y las salidas Zero, Overflow y CarryOut son todas de 1 bit.

Fig. 3.10 ALU de 32 Bits, cuyo comportamiento se describe en la tabla 3.5

Anticipación del acarreo.

El sumador que se incorporó a la ALU de 32 bits (Sumador de acarreo extendido) es poco

eficiente debido a que la generación del último acarreo no se podrá hacer, mientras no se

hayan generado los 31 acarreos menos significativos. Por que el acarreo de cada bit se va

propagando hasta alcanzar al último bit. Esto es, el acarreo se va generando en forma

secuencial, en cada sumador de 1 bit.

Existe una variedad de esquemas que permiten la generación anticipada del acarreo, estos

esquemas son mas rápidos que el acarreo extendido por que viajan por menos compuertas.

Algunos resultados aceptables producen el acarreo en un orden log2 del número de bits a

sumar.

La anticipación de acarreo es posible, por que a diferencia del software, el hardware puede

trabajar en paralelo, mucha compuertas pueden compartir entradas y todas trabajaran

cuando existan cambios en tales entradas.

Acarreo rápido usando “Hardware Infinito”

De acuerdo con los principios del álgebra Booleana, cualquier función la podemos expresar

como una suma de productos, o bien como un producto de sumas, por lo que para su

implementación en ambos casos, requeriría de dos niveles de compuertas.

Por ejemplo, para el acarreo de entrada en el sumador 2, el cual es exactamente el acarreo

de salida del bit 1, se tendría:

CarryIn2 = (b1CarryIn1) + (a1CarryIn1) + (a1b1)

Similarmente, CarryIn1 está definido como:

CarryIn1 = (b0CarryIn0) + (a0CarryIn0) + (a0b0)

Usando solo c en lugar de CarryIn, podemos rescribir las dos expresiones anteriores como:

c2 = (b1c1) + (a1c1) + (a1b1)

c1 = (b0c0) + (a0c0) + (a0b0)

Sustituyendo el resultado encontrado para c1 en la expresión de c2 se tiene:

c2 = (b1( (b0c0) + (a0c0) + (a0b0)) ) + (a1(b0c0) + (a0c0) + (a0b0) ) +

(a1b1)

c2 = (a1a0b0) + (a1a0c0) + (a1b0c0) + (ba0b0) + (b1a0c0) + (b1b0c0)

+ (a1b1)

Esta expresión es sólo para el 2º. bit, pero la ecuación crece exponencialmente con el

número de bits, de manera que si se pretende usar este esquema, el costo de la

implementación de la unidad de anticipación de acarreo, debido a su gran número de

compuertas, será mayor que el costo del resto de la ALU.

Usando abstracciones en la obtención del acarreo, para Generar y Propagar.

En este esquema se complican un poco las ecuaciones con la finalidad de simplificar al

Hardware. Para el acarreo 2 se obtuvo la expresión:

c2 = (a1b1) + (a1 + b1)c1

y para acarreo 1:

c1 = (a0b0) + (a0 + b0)c0

En general el acarreo i + 1 depende del acarreo i de acuerdo a la expresión:

ci+1 = (aibi) + (ai + bi)ci

El primer término indica la generación de un acarreo en el bloque i, por lo que le

llamaremos gi; el segundo termino indica que el acarreo ci se va a propagar si su

coeficiente de propagación es verdadero, a este coeficiente le llamaremos pi. De manera

que:

gi = aibi

pi = ai + bi

Usando estas definiciones tenemos que:

ci+1 = gi + pici

Esta expresión indica que habrá un acarreo a la salida del bloque i, si éste fue generado

dentro del bloque o si este ya existía (en ci) y se dieron las condiciones para su

propagación.

Tomando las definiciones de generación y propagación como abstracciones, podemos

obtener de manera simplificada los primeros 4 acarreos:

c1 = g0 + (p0c0)

c2 = g1 + (p1 g0) + (p1p0c0)

c3 = g2 + (p2g1) + (p2p1g0) + (p2p1p0c0)

c4 = g3 + (p3g2) + (p3p2g1) + (p3p2p1g0) + (p3p2p1p0c0)

Estas ecuaciones representan el sentido común: CarryIni es 1 si algún sumador cercano lo

generó y todos los sumadores intermedios lo propagaron. Una analogía con una tubería de

agua se muestra en la figura 3.11 para dar claridad a estas ideas.

Fig. 3.11 Una tubería como analogía para mostrar la anticipación del acarreo para 1 bit, 2 bits y 4 bits.

El acarreo va a existir (existirá agua en la salida) si fue generado (se abrió alguna de las llaves g), o si existía

un acarreo inicial y se dieron las condiciones para su propagación (todas las llaves p se abrieron).

Otro nivel de abstracción para Acarreos rápidos.

Con las ecuaciones anteriores se demuestra que con un poco mas de Hardware, es posible

generar acarreos rápidos para sumadores de 4 bits. Si conectamos 4 sumadores como

bloques de un Sumador de acarreo extendido, obtendremos un sumador de 16 bits mas

rápido que si el acarreo se arrastrase por los 16 bits.

Para mejorarlo aún mas, es posible usar la anticipación en un nivel mas alto. Para obtener el

acarreo anticipado en sumadores de 4 bits, necesitamos generar y propagar señales en este

nivel mas alto. La propagación para bloques con sumadores de 4 bits será posible si todos

los bits dentro de un bloque la hacen posible, esto es:

P0 = p3p2p1p0

P1 = p7p6p5p4

P2 = p11p10p9p8

P3 = p15p14p13p12

Cada Pi representa una “súper” propagación en un sumador de 4 bits.

Para la generación debe considerarse que será verdadera si se generó en el bit mas

significativo, o si se generó en uno de los bits inferiores al mas significativo, y durante las

etapas intermedias se realizó su propagación.

G0 = g3 + (p3g2) + (p3p2g1) + (p3p2p1g0)

G1 = g7 + (p7g6) + (p7p6g5) + (p7p6p5g4)

G2 = g11 + (p11g10) + (p11p10g9) + (p11p10p9g8)

G3 = g15 + (p15g14) + (p15p14g13) + (p15p14p13g12)

Cada Gi representa una “súper” generación en un sumador de 4 bits. Una analogía con una

tubería, para estas nuevas versiones de generación y propagación, se muestra en la figura

3.12 para dar claridad a estas ideas.

Entonces, en un nivel de abstracción mas alto, es posible escribir las ecuaciones de los

acarreos de salida de cada bloque de 4 bits.

C1 = G0 + (P0c0)

C2 = G1 + (P1 G0) + (P1P0c0)

C3 = G2 + (P2G1) + (P2P1G0) + (P2P1P0c0)

C4 = G3 + (P3G2) + (P3P2G1) + (P3P2P1G0) + (P3P2P1P0c0)

Puede notarse que estas ecuaciones son iguales a las ecuaciones en minúsculas mostradas

anteriormente, excepto por que se trata de otro nivel de abstracción, en el cual cada Ci

corresponde al acarreo de un bloque de 4 bits. En la figura 3.13 se muestra un sumador de

16 bits (a bloques), resaltando el bloque por medio del cual se procesan los acarreos de

cada sumador de 4 bits, para generar el acarreo de los 16 bits.

Fig. 3.12 La tubería como analogía para mostrar la anticipación del acarreo, en otro nivel de abstracción. P0

estará abierto sólo si todas las pi ( i = 0 .. 3) están abiertas; además fluirá agua en G0 si al menos una gi esta

abierta y las pi permiten su propagación.

Fig. 3.13 Se utilizan ALUs de 4 bits para anticipar el acarreo de un sumador de 16 bits.

Tarea 6

1. Convertir 512diez, -1023diez y – 4 000 000diez en números binarios en complemento 2.

2. Qué números en decimal representan los números en complemento 2 siguientes:

1111 1111 1111 1111 1111 1110 0000 1100dos

1111 1111 1111 1111 1111 1111 1111 1111dos

0111 1111 1111 1111 1111 1111 1111 1111dos

3. ¿Por que MIPS no tiene una instrucción de resta inmediata?

4. Encontrar la secuencia mas corta de instrucciones MIPS para determinar si existió

acarreo de salida después de la suma de dos registros, supongamos que $t3 se sumó con

$t4 y el resultado se almacenó en $t5. Colocar 0 o 1 en $t2 el acarreo de salida es 0 o 1,

respectivamente (Sugerencia: Esto puede hacerse en dos instrucciones).

5. Dos amigos, Enrique y Beto están en desacuerdo. Enrique dice “Todos los enteros

mayores que cero y exactamente divisibles por 6 tienen exactamente dos 1s en su

representación binaria”. Beto no esta de acuerdo, él dice “No, pero tales números tienen

un número par de 1s en su representación”. Estas de acuerdo con Enrique, con Beto o

con ninguno de los dos?

6. Para el sumador completo de 1 bit (fig. 3.3), se desarrolló el hardware correspondiente a

CarryOut, muestre el hardware necesario para implementar la señal sum.

7. En la figura 3.8 b se muestra como un bloque a la Unidad de Detección de Sobreflujo,

obtenga el circuito por medio del cual se generaría la señal overflow, de acuerdo a su

comportamiento.

8. Esquema de Anticipación de acarreo. Se quiere sumar:

a: 0001 1010 0011 0011dos

b: 1110 0101 1110 1011dos

Determinar los valores de gi, pi, Pi y Gi con los dos números y encuentre CarryOut14

(C4).