CAPITULO II MARCO TEÓRICO 2.1

Anuncio

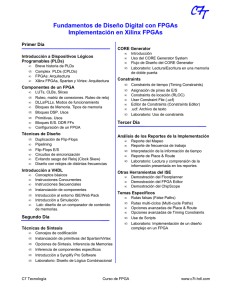

CAPITULO II MARCO TEÓRICO 2.1 Antecedentes. Pensar en la actualización y mejoras que se pueden aplicar a un laboratorio podrían considerarse de alto costo, sin embargo estudios realizados demuestran que si es posible implementar estos diseños, lo cual es corroborado por los argumentos expresos en las siguientes documentaciones. Titulo del trabajo: Diseño y construcción de un modulo de entrenamiento basado en el microcontrolador AT89C52 de la ATMEL Autor: Duran D. Nelson E. e Israel T. Medina C. Año: 2000. Departamento de Electrónica, Universidad Nacional Experimental del Táchira. En esta tesis se desarrollo un modulo de entrenamiento basado en el microcontrolador AT89C52, el cual permite la programación de microcontroladores de la familia 89C5X de ATMEL, por medio de seis circuitos diferentes que permiten el desarrollo de distintos proyectos para el microcontrolador. Se implementan dos aplicaciones, una codificada en labview y otra en lenguaje ensamblador para el microcontrolador 89C52, encargado de manejar las rutinas del programador, algunos de los periféricos que maneja el modulo son: monitores lógicos, convertidores análogos digital, displays, pantalla de cristal entre otros. Así mismo se desarrollo un modulo entrenador con diferentes submódulos para la implementación de prácticas didácticas para sistemas digitales. Titulo: diseño y construcción de un entrenador didáctico para microcontroladores de la familia MC68HC11. Autor: Guerrero M. Gloria E. e Guilarte O. Ivan R. Año: 2003. Departamento de Electrónica, Universidad Nacional Experimental del Táchira. En este trabajo se construyo un entrenador digital para el microcontrolador MC68HC11, el cual cuenta con un conjunto de periféricos que permitirán el desarrollo de aplicaciones en materias como: sistemas digitales y control de procesos. Adicionalmente contiene una serie de módulos para implementar diferentes aplicaciones de diseño en el laboratorio. De esta manera lo afirman sus autores: “Con este tipo de diseño se permite que varias personas utilicen diferentes módulos a un mismo instante. La escogencia de los microcontroladores motorola se baso en que este tipo de integrados son de gran aplicabilidad en cualquier área con gran eficiencia”. Otra herramienta de gran importancia es el estudio y desarrollo de las aplicaciones disponibles para las FPGA, uno de los trabajos que exponen información referente puede reflejarse en la siguiente investigación. Titulo: Diseño y fabricación de una placa didáctica basada en FPGA Autor: Arellano M. Francisco. e Somovilla T. Sergio. Año: 2005. Facultad de Informática Universidad Complutense de Madrid, España. Este diseño consiste en la realización de un prototipo de una placa la cual incluye módulos adicionales para el desarrollo de sistemas digitales, prototipo está basada en la FPGA XC2S100-5 de la familia Spartan-II de Xilinx, la cual permite la comunicación desde la placa hacia el ordenador por medio el software asistido ISE de Xilinx. 2.2 Bases teóricas. 2.2.1 Dispositivos Lógicos Programables. 2.2.1.1 Historia de los Dispositivos Lógicos Programables. Los Dispositivos Lógicos Programables (PLDs) fueron introducidos a mediados de los 70s. La idea era construir circuitos lógicos combinacionales que fueran programables. Al contrario de los microcontroladores, que pueden correr un programa y poseen un hardware fijo los PLDs permiten la modificación a nivel de hardware. En otras palabras, un PLD es un chip multi propósito cuyo hardware se puede reconfigurar para realizar tareas particulares. El primer PLD fue llamado Arreglo Lógico Programable (PAL). Los PAL solo utilizan compuertas lógicas sin Flip-Flops, por lo que solo permiten la implementación de circuitos combinacionales. Para superar esta limitación luego fueron creados los registered PLDs los cuales incluyen Flip-Flops en cada salida del circuito. Con estos dispositivos es posible implementar funciones secuenciales simples. A comienzos de los 80s, se fueron agregando circuitos lógicos adicionales a las salidas de los PLDs. La nueva celda de salida, llamada Macrocell, contiene a parte de Flip-Flops, puertas lógicas y multiplexores. La celda en si es programable, permitiendo varios modos de operación. Adicionalmente provee una señal de retorno o feedback desde la salida del cricuito al arreglo programable, lo que le da una mayor flexibilidad. Esta nueva estructura fue llamada generic PAL (GAL). Todos estos chips (PAL, PLA, registered PLD, GAL/PALCE) son conocidos en conjunto como SPLDs (Simple PLDs). La GAL/PALCE es la única que aun se fabrica en chips independientes. Luego de esto se fabricaron chips con muchas GAL en su interior utilizando una arquitectura mucho más sofisticada, mejor tecnología y muchas otras características adicionales como soporte para JTAG. Estas estructuras son conocidas como CPLD (Complex PLD). Los CPLD son bastante populares por su alta densidad de puertas, alto performance y bajo costo. Finalmente a mediados de los 80s fueron introducidas las FPGA, las cuales difieren de los CPLD en su arquitectura, tecnología y costos. Estos dispositivos fueron creados principalmente para la implementación de circuitos de alto rendimiento. Todos los PLDs son no volátiles. Pueden ser Programables Solo una Vez (OTP) en cuyo caso son utilizados fusibles o anti fusibles, con EEPROM o memoria FLASH. Las FPGA por otro lado son la mayoría volátiles puesto que utilizan SRAM para almacenar las conexiones en estos casos generalmente se utiliza un ROM externa para almacenar la configuración inicial al momento del encendido. 2.2.1.2 Definición de Dispositivos Lógicos Programables PLDs. Las iniciales PLD vienen del inglés Programmable Logic Device, que traducido a nuestro idioma significa Dispositivo Lógico Programable y son circuitos integrados que ofrecen a los diseñadores en un solo chip, un arreglo de compuertas lógicas y flip-flop’s, que pueden ser programados por el usuario para implementar funciones lógicas; y así, una manera más sencilla de reemplazar varios circuitos integrados estándares o de funciones fijas. Las ventajas que trae con respecto a los circuitos integrados de funciones fijas (series 74XX y 40XX ) son variadas, las más importantes son: PLD’s representan menor costo para los fabricantes. Pueden reemplazar funciones de otros dispositivos lógicos. Reducción de espacio en las tarjetas de circuito impreso. Simplificación del alambrado entre unos chips y otros. Disminución en los requerimientos de potencia. Realización de aplicaciones especiales no encontradas en circuitos integrados de funciones fijas. Puede reflejarse menor costo para el usuario al ver las ventajas de tener menor cantidad de circuitos integrados; por consiguiente, procesos de ensamblado más rápidos, menor probabilidad de que puedan ocurrir fallas, así como menores procedimientos en la detección de fallas cuando estas se presenten. Un PLD típico está compuesto de arreglos de compuertas lógicas, uno de ellos a base de compuertas AND al que se le denomina Plano AND y el otro de compuertas OR, denominado Plano OR; estos pueden ser programables y dependiendo del plano o los planos que lo sean, será la clasificación que reciba el PLD. Las variables de entrada tienen interconexiones hacia uno de los planos, a través de compuertas con salidas complementarias ( es decir con una salida inversora y una no-inversora ); y salidas de los planos, conectadas a las terminales externas del dispositivo, por elementos lógicos como pueden ser: inversores, compuertas OR y flip-flop’s; además, en algunos casos existe retroalimentación de las salidas hacia uno de los planos, para tomarlas como entradas nuevamente. La programación se lleva a cabo por medio de conexiones de fusibles; de tal forma que en una compuerta OR, una entrada con conexión fusible “Fundida o Quemada” ( fusible abierto ) funcione como un cero lógico y una conexión intacta como el valor de la(s) variable(s) de entrada. 2.2.1.3 Clasificación entre arquitecturas de los PLDs. La clasificación de los PLD’s, dependerá básicamente del plano o los planos que sean programables, la clasificación se muestra en la figura 1, se pueden determinar en tres grupos: Figura 1. Clasificación de los PLD’s., (Fuente: http://mcielectronics.wordpress.com) ROM Mask Read-Only Memory ( Memoria de Máscara Programable de Solo Lectura ), Dispositivo programado solamente por el fabricante y como se muestra en el esquema anterior este se subdivide en tres partes que son: PROM Programmable Read-Only Memory ( Memoria Programable de Solo Lectura ), Dispositivo programado por el usuario y no borrable o reprogramable. EPROM Erasable Programmable Read-Only Memory ( Memoria Programable y Borrable de Solo Lectura ); este tipo de Memorias se borran Mediante Luz ultravioleta; con la ventaja de que puede ser programada por el usuario. EEPROM Electrically Erasable Programmable Read-Only Memory, memoria Programable y Borrable Eléctricamente de Solo Lectura, al igual que puede ser programado por el usuario. PAL Programmable Array Logic (Lógica en un Arreglo Programable), la arquitectura de éste PLD está compuesta por un Plano AND programable y el Plano OR fijo. Este dispositivo es el intermedio entre una PROM y un PLA; debido a que, por cada entrada que se agregue no será necesario duplicar la cantidad de fusibles y el tener un plano fijo conduce a un menor retardo en la circuitería interna. También incluye la capacidad de programar la polaridad de salida. Este PLD puede incluir una serie de componentes a la salida del plano OR, como pueden ser: Inversores y Flip-Flops, que permitirán hacer del dispositivo, un PLD versátil. Existen dos tipos de PAL’s, uno de los cuales puede ser programado solamente una vez, por ejemplo: El PAL16R8 el cual es un dispositivo de 16 posibles entradas y con 8 salidas; todas con Flip-Flops. El otro PAL mejor conocido como GAL de Generic Array Logic (Lógica en Arreglo Genérico), combina las características de un PAL; pero además, agrega tecnología especial para ser borrado y programado eléctricamente. Este dispositivo que es el que nos ocupa, será descrito y analizado detalladamente en las páginas subsecuentes. PLA Programmable Logic Array (Arreglo Lógico Programable), este tipo de dispositivos resuelve el problema de las PROM; debido a que, tiene tanto el plano AND como el OR programables. De forma que solo se seleccionan los productos de términos necesarios para las diferentes aplicaciones; esto hace mucho más eficiente la matriz programable y al dispositivo más versátil. A este tipo de dispositivos, también se les conoce como Field Programmable Logic Array (Arreglos Lógicos Programables de Campo). Los FPLA o PLA aceptan más variables de entrada con mucho menor producto de términos que 2n. Estos PLD’s incluyen además la capacidad de programar la polaridad de salida, lo que permite trabajar con max-términos si se requieren; esto se logra a través de una ORExclusiva. Un ejemplo más es la serie “ MAPL ” Multiple Array Programmable Logic ( Lógica Programable en Arreglo Múltiple ), de National Semiconductor; que no son, más que arreglos de FPLAS como son: El MAPL128 y el MAPL144, algunos incluyen un arreglo PAL; como lo es el MAPL244. No obstante, los fusibles adicionales (debido a que hay dos planos programables), agregan un retardo mayor que los de un solo plano programable y una circuitería más compleja y al mismo tiempo la programación se vuelve más elaborada. Debido a la tecnología que utilizan también aumenta su costo. En la figura 2 se ilustran las diferencias entre las características de los PLDs. (a) (b) (c) Figura 2. Diferencias entre las características de los PLDs. (a). Diagrama esquemático de un PLD tipo PROM, (b). Diagrama esquemático de un PLD tipo PLA, (c). Diagrama esquemático de un PLD tipo PAL. (Fuente: http://proton.ucting.udg.mx/tutorial) 2.2.2 Dispositivo Lógico Programable FPGA (Field Programmable Gate Array). 2.2.2.1 Definición de los FPGA. Los FPGA (Field Programmable Gate Array) son circuitos lógicos programables directamente por el usuario, lo cual requiere de herramientas de costo relativamente bajo, como lo son el software de desarrollo y el dispositivo grabador. La grabación o programación de uno de estos dispositivos se puede llevar a cabo en milisegundos. Los FPGA son muy utilizados por fabricantes que producen tecnología a baja escala, como por ejemplo diseñadores de equipos de propósito específico, los cuales no pueden justificar la producción de ASICs por los bajos volúmenes de dispositivos que venden. Los FPGAs tienen una funcionalidad similar, a costos menores y con una velocidad ligeramente menor. Con el software de diseño se puede simular en hardware antes de mandar a fabricar el ASIC correspondiente. 2.2.2.2 Arquitectura de las FPGA. Las FPGA se caracterizan principalmente por su estructura lógica, tamaño (número de bloques lógicos y terminales de E/S), recursos especiales de procesamiento, almacenamiento y control y por su velocidad y consumo de energía. Los FPGAs de Xilinx constan de una cuadrícula de bloques lógicos programables CLBs, los bloques lógicos como la estructura de interconexión se pueden programar cargando desde una fuente externa valores a las celdas de configuración. Las celdas de configuración controlan la lógica y la interconexión que realizan la función de aplicación del FPGA. No hay un área de RAM separada en el chip, sino que las celdas de configuración están distribuidas en el chip. En los bordes, rodeando los bloques lógicos hay bloques de entrada/salida configurables (IOBs). Los bloques básicos que componen un FPGA de Xilinx son: CLBs (Configurable Logic Block): proporcionan los elementos funcionales para construir más lógica. IOBs (Input Output Block): proporcionan la interfaz entre el paquete pines y la lógica interna. Clock DLLs (Delay-Locked Loops): para la compensación de retraso de distribución de reloj y control de dominio de reloj. Bloques de RAM Estructura de interconexión o enrutamiento programable. En la figura 3 se muestra el diagrama de bloques básico de una FPGA Spartan II. Figura 3: Diagrama de bloques básico de la FPGA Spartan II. (Fuente: www.xilinx.com) Bloques Lógicos (CLBs): La estructura básica de un CLB es la celda lógica o LC (Logic Cell). Un LC incluye un generador de funciones (LUT) de 4 entradas, lógica de acarreo (Carry Logic), y un elemento de almacenaje. Cada CLB contiene cuatro LCs, organizados en dos trozos o Slices similares, tal como muestra la figura 4. Además de los cuatro LCs, un CLB contiene también una lógica adicional que hace posible la combinación de los generadores de función para que éstos puedan aceptar cinco o seis entradas. Por lo tanto, cuando se quiere estimar el número de compuertas de un dispositivo dado, cada CLB soporta hasta 4.5 LCs. Figura 4: Estructura interna de la CBLs Spartan II, (Fuente www.xilinx.com) Cada uno de los elementos que componen el CLB se describe en los siguientes puntos: Tabla de Look up (Look up Table – LUT): Los generadores de funciones están implementados como tablas de look up de 4 entradas. Además de trabajar como generadores de función, cada LUT puede funcionar como una RAM sincrónica de 16 x 1-bit. También dos LUTs dentro un Slice pueden ser combinadas para trabajar como una RAM sincrónica de 16 x 2-bits, de 32 x 1-bit o de 16 x 1-bit utilizando puerto dual. A parte de lo anterior, una LUT puede utilizarse como un registro de desplazamiento de 16-bits, que es ideal para capturar datos a altas velocidades. Esta característica es muy utilizada en aplicaciones de procesamiento de señales (DSP). Elementos de Almacenamiento: Los elementos de almacenamiento de un Slice pueden ser configurados como un flip-flop D. Las entradas pueden ser alimentadas por el generador de funciones o directamente de las entradas del Slice. Además, aparte de las señales de reloj y de habilitación del reloj (Clock Enable), cada Slice tiene señales sincrónicas de Set y Reset (SR y BY). SR fuerza a un elemento de almacenamiento a su estado de inicialización especificado en la configuración. Por otro lado, BY fuerza a dicho elemento de almacenamiento al estado opuesto. Alternativamente, ambas señales pueden configurarse para que trabajen en forma asincrónica. Todas las señales de control son invertibles en forma independiente, y son compartidas por los dos flip-flops dentro del Slice. Lógica Adicional: Cada Slice contiene un multiplexor que se utiliza para combinar las salidas de los generadores de funciones. Gracias a esta combinación se puede implementar un generador de funciones de 5 entradas, un multiplexor 4:1, o un seleccionador de funciones de hasta nueve entradas. De forma similar, otro multiplexor (llamado multiplexor F6) combina las salidas de los cuatro generadores de funciónes dentro de un CLB seleccionando una de las dos salidas del multiplexor F5. Esto permite la implementación de un generador de funciones de 6 entradas, un multiplexor 8:1, o un selector de funciones de hasta 19 entradas. Por lo tanto, la lógica adicional descrita hace que la funcionalidad de un CLB sea mucho más flexible y potente. Lógica Aritmética: Un acarreador lógico (carry logic) dedicado provee una rápida capacidad aritmética para aplicaciones que requieren un procesamiento de datos veloz. Cada CLB contiene dos cadenas de acarreadores (una cadena por Slice). La resolución de las cadenas de acarreadores es de dos bits por CLB. La aritmética lógica incluye además una compuerta XOR, la que permite la implementación de un sumador de 1-bit dentro de un LC. Además, se dispone de una compuerta AND dedicada que cumple la función de mejorar la eficiencia en la implementación de multiplicadores. Adicionalmente, los canales utilizados por los acarreadores pueden ser utilizados por los generadores de función para la implementación de funciones lógicas amplias. BUFTs: Cada CLB contiene dos buffers de 3 estados (BUFTs) utilizados para alimentar los buses internos del chip. Cada BUFT tiene un pin de control y de entrada independiente. Bloques de entrada/salida (IOB): Las entradas y salidas soportan muchos tipos de estándar de señalización, como TTL, CMOS, PCI, AGP, etc, que se diferencian en los niveles de voltaje que manejan. En la figura 5 se muestra el contenido de un IOB. Se pueden observar tres elementos de almacenamiento, los que pueden ser utilizados como flipflop D o como latches. Cada flip-flop tiene una señal de reloj compartida, con señales independientes de habilitación para el reloj (Clock Enable) y una señal compartida Set/Reset (SR). Para cada registro, esta señal puede configurarse independientemente como un Set sincrónico, un Reset sincrónico, un Preset asincrónico, o un Clear asincrónico. Figura 5: Estructura interna del bloque de entrada y salida IOB de Spartan II. (Fuente: www.xilinx.com) Un rasgo no mostrado en el diagrama de bloques, pero controlado por el software, es el control de polaridad. Los buffer de entrada y salida y todos las señales de control IOB tienen controles de polaridad independientes. Resistencias pull-up y pull-down opcionales y un circuito guardián-débil (weak-keeper) optativo son adjuntados a cada bloque I/O. Antes de la configuración se fuerzan todas las salidas no involucradas en la configuración a su estado de alta-impedancia. Las resistencias pull-down y los circuitos guardián-débil son inactivos, pero las entradas pueden convertirse en pull-up opcionalmente. La activación de la resistencias pull-up antes de la configuración es controlada en una base global por los pines de modo de configuración. Si las resistencias pull-up no son activadas, todos los pines flotarán. Por consiguiente, resistencias pull-up o pull-down externas debe ser proporcionada en los pines requeridos para un nivel de lógica bien definida antes de la configuración. Entradas: Cada entrada puede conectarse, a través de un buffer, directamente a la lógica interna del Spartan o a la entrada de un flip-flop (opcional). Otro componente opcional es un elemento de retardo (Programmable Delay), que elimina los problemas de tiempo en la entrada, haciendo coincidir el retardo interno que existe en las líneas de reloj del FPGA, y de esta manera minimizar la diferencia en tiempo entre la entrada y las señales internas. Cada buffer de entrada puede ser configurado para soportar cualquier estándar de señalización soportado por el dispositivo. En algunos casos, el buffer de entrada utiliza un voltaje umbral proporcionado por el usuario, V REF. La necesidad de proporcionar VREF impone restricciones en cuales normas pueden usarse en proximidades cercanas de el uno al otro. También se dispone de resistencias tipo pull-up y pull-down, para hacer más flexible aún el tipo de entrada. Por ejemplo, se puede configurar una entrada como pull-up para que pueda ser conectada a una salida de colector abierto. Salidas: Las salidas están precedidas por un buffer de 3 estados. La entrada de este buffer puede venir desde un flip-flop de salida o directamente desde la lógica interna, y a su vez, la entrada de control de este buffer puede venir directamente desde la lógica interna o desde un flip-flop. Al igual que las entradas, las salidas pueden ser configuradas individualmente para soportar los diferentes estándares de señalización. Cada buffer de salida tiene una capacidad de 24 [mA] de corriente, con un control del slew rate el cual, a costa de hacer un poco más lento la respuesta temporal del bloque de I/O, puede disminuir el efecto de oscilaciones que se pueden generar en la salida debido al cambio de un nivel lógico a otro. En la mayoría de los estándares de señalización, el nivel alto de tensión de salida depende de una referencia de tensión llamada VCCO, que debe ser suministrado en forma externa por el usuario. Bancos de Entrada/Salida: Algunos de los estándares de entrada y salida requieren de una tensión externa VCCO y/o una tensión de referencia VREF. Estas tensiones están conectadas a las entradas y salidas por grupos, llamados bancos. Es decir, si aplicamos un cierto estándar a una entrada o salida, ésta va a incluir también a las otras entradas o salidas que pertenecen al mismo banco. Por lo tanto existen ciertas restricciones al utilizar estos estándares. Ocho bancos de entrada/salida resultan de subdividir cada periferia del dispositivo en dos bancos. Cada banco tiene varios pines de V CCO, los cuales deben ser conectados al mismo nivel de tensión. El valor del nivel de tensión está especificado por el estándar utilizado. Dentro de un banco, los estándares pueden ser combinados sólo si utilizan el mismo valor para V CCO. En el caso de las entradas, se requiere de una tensión umbral VREF (suministrado externamente). Este valor se debe introducir en ciertos pines del dispositivo que son automáticamente asignados para este propósito. Dependiendo del caso, aproximadamente uno de seis pines de un banco es utilizado para este rol. Los pines de VREF dentro de un banco están interconectados internamente, lo que implica el uso de solo un nivel de V REF por banco, sin embargo pueden ser mezclados con pines del mismo banco que no requieren de esta tensión umbral. El número y lugar de los pines dedicados a VCCO y VREF dependen del tipo de FPGA Spartan II que se utilice. Bloques de RAM: La FPGA Spartan-II, incorpora varios bloques de memoria RAM. Los bloques de memoria RAM se organizan en columnas. Todos dispositivos Spartan-II contienen dos columnas. Estas columnas se extienden a lo largo del chip. Cada bloque de memoria es de cuatro CLB , en consecuencia, un dispositivo Spartan-II contiene ocho CLB, dos bloques de memoria por columna, para un total de cuatro bloques. Un bloque de RAM se ilustra en la Figura 6, es sincrónica de doble puerto con un control para cada puerto de manera independiente. Estos puertos se pueden configurar de forma independiente para proporcionar un bus más ancho de comunicación. Figura 6: Bloque de RAM sincrónica de doble puerto. (Fuente: www.xilinx.com) Matriz de Enrutamiento Programable: Corresponde a la ruta de mayor retardo que limita la velocidad en cualquier diseño. Es por esto que la arquitectura de enrutamiento trabaja en conjunto con el software dedicado a la localización y enrutamiento (place-and-route software), de tal manera de obtener el mínimo de retardo que se pueda producir en un diseño. Este software corresponde a un algoritmo que busca las mejores rutas según la implementación y el tipo de dispositivo. Los componentes de la matriz de enrutamiento programable se describen a continuación. Enrutamiento Local de las FPGA: Los recursos de enrutamiento local, tal como se muestra en la figura 7, suministran los siguientes tres tipos de conexiones: Interconexiones a lo largo de los LUTs, flip-flops y la GRM (Matriz General de Enrutamiento). Rutas internas retroalimentadas en los CLB, las cuales hacen posible una conexión de alta velocidad entre LUTs dentro de un mismo CLB, encadenadas entre ellas con un mínimo de retardo asociado. Rutas directas que hacen conexión entre CLBs horizontalmente adyacentes, a una alta velocidad, eliminando el retardo producido si se conectaran mediante la GRM. Figura 7: Enrutamiento local de una FPGA. (Fuente: www.xilinx.com) Enrutamiento de Propósito General: Es en este sistema de enrutamiento por donde viajan la mayoría de las señales, y por consiguiente, la mayoría de los recursos de interconexión están asociados a este tipo de enrutamiento. Los recursos de enrutamiento general están localizados en los canales horizontales y verticales, los que a su vez están asociados a las filas y columnas de los CLBs. Los recursos de enrutamiento son los siguientes: Adyacente a cada CLB se encuentra un GRM. El GRM es la matriz de interruptores por la cual los recursos de enrutamiento horizontal y vertical se conectan, y también es la responsable de que los CLBs tengan acceso al sistema de enrutamiento de propósito general. 24 líneas que rutean las señales provenientes de la GRM a otras GRMs en cada una de las cuatro direcciones. 96 x 6 líneas provistas de buffers encaminan las señales de una GRM a otras GRMs ubicadas a seis bloques de distancia de la primera, en cada una de las cuatro direcciones. Estas líneas están diseñadas para interconectar GRMs que se encuentran lejos, donde la distancia es de seis bloques. Sin embargo, también pueden conectar GRMs que se encuentran a 3 bloques de distancia. Se dispone de 12 líneas de longitud larga, conectadas a buffers, bidireccionales, utilizadas para distribuir señales a través del dispositivo en forma rápida y eficiente. Enrutamiento de Entrada/Salida: Este sistema de enrutamiento provee de recursos adicionales alrededor de la periferia para la conexión entre los bloques de IOBs y los CLBs. Este sistema de enrutamiento adicional llamado VersaRing, facilita el intercambio (pin-swapping) y localización de los pines (pin-locking), lo que es muy útil en el rediseño, ya que se pueden adaptar las entradas y salidas cuando el dispositivo está inserto en una placa. Enrutamiento Dedicado: Algunas señales son críticas en un diseño, por lo que necesitan de recursos dedicados para maximizar su desempeño. En la arquitectura Spartan II se dispone de dos tipos de enrutamiento dedicado para satisfacer dos clases de señales. Recursos de enrutamiento horizontal con buses de tres estados. Cuatro líneas de buses (que se pueden separar) se disponen por columna de CLBs, permitiendo múltiples buses dentro de una columna, tal como muestra la figura 8. Dos redes dedicadas por CLB propagan señales de tipo acarreo (carry signals) verticalmente a CLBs adyacentes. Figura 8: Conexiones de BUFT a las Líneas del Bus Horizontales Dedicadas. (Fuente: www.xilinx.com) Enrutamiento Global: Los recursos del enrutamiento global distribuyen las señales de reloj y otras señales con gran nivel de alimentación de salida (very high fanout) a través del dispositivo. Los dispositivos Spartan II contienen dos hileras de recursos globales de enrutamiento, llamados recursos globales de enrutamiento primario y secundario: Los recursos de enrutamiento global primario se componen de cuatro redes globales con pines de entrada dedicados, que están diseñadas para distribuir con un gran fanout las señales de reloj con un mínimo de skew (Skew se refiere a la distorsión que afecta a los pulsos cuando viajan a través de las líneas. Esta distorsión produce que los extremos del pulso tiendan a ser más oblicuos). Cada red global puede alimentar todos los pines de reloj de los bloques CLB, IOB, y RAM. La red primaria global puede ser alimentada sólo por los buffers globales, de los cuales existen cuatro, uno por cada red. Los recursos locales secundarios consisten en una médula de 24 líneas, 12 recorren la parte de arriba del chip, y 12 recorren la parte baja del chip. Los recursos locales secundarios son más flexibles de los globales primarios, ya que no están restringidos sólo a señales de reloj. Distribución de Reloj: La arquitectura Spartan II posee una distribución de reloj de alta velocidad, a través de los recursos globales primarios descritos anteriormente. Una red de distribución de reloj típica se muestra en la figura 9. Se disponen de cuatro buffers globales, dos arriba y al centro, y dos abajo y al centro del dispositivo. Estos alimentan las cuatro redes primarias globales que pueden conectarse a cualquier pin de reloj. Existen cuatro pines dedicados a señales de reloj, cada uno adyacente a cada buffer global. La entrada a los buffers globales es seleccionada desde estos pines o desde señales del enrutamiento de propósito general. Figura 9: Red de Distribución Global de Reloj. (Fuente: www.xilinx.com) Delay-Locked Loop (DLL): Un DLL realiza la misma tarea que los tradicionales PLLs (Phase Lock Loops), pero de una forma más robusta y menos susceptible a interferencias de ruido. Cada DLL de la familia Spartan II está asociado a una entrada del buffer de reloj, es completamente digital y elimina el retardo entre el pin de entrada y los pines internos de reloj a través del dispositivo. Cada DLL puede también alimentar dos redes globales de reloj. El DLL supervisa el reloj de la entrada y el reloj distribuído, y automáticamente ajusta un elemento de retraso de reloj (figura 10). Se introduce el retraso adicional de tal forma que los cantos del reloj alcanzan los flip-flops interiores exactamente un período del reloj después de que llegan a la entrada. Figura 10: Diagrama en bloques de un DLL. (Fuente: www.xilinx.com) 2.2.3 Herramientas de diseño para las FPGA. En el mercado se encuentran gran cantidad de herramientas para el diseño con FPGA y VHDL. Algunas de ellas son de uso público, otras cubren casi todos los dispositivos del mercado. Las más especificas son de las compañías de dispositivos, como las de Actel, Altera, Cypress y Xilinx. La mayoría de las herramientas funcionan sobre PC y algunas están disponibles para workstation. Ya que las herramientas específicas de cada compañía están optimizadas para las arquitecturas de sus dispositivos, además de cubrir toda la gama de posibilidades de diseño que sus FPGA ofrecen, desde la síntesis hasta el desarrollo de sistemas embebidos. 2.2.3.1 Herramientas de síntesis. La síntesis es uno de los pasos más esenciales en la metodología de diseño con FPGA, por lo que se necesitan utilizar las técnicas del estado del arte para generar la mejor representación lógica para el dispositivo seleccionado, a partir de la definición conceptual del diseño. Síntesis HDL y síntesis con enfoque físico: Las herramientas de síntesis que salieron al mercado a mediados de los 1980s, referidas como tecnología de síntesis HDL, toman una descripción RTL de un diseño ASIC junto con un conjunto de restricciones de tiempo y generan un netlist al nivel de puertas, en un proceso de minimización y optimización. A mediados de los 1990s, estas herramientas fueron extendidas para incluir las arquitecturas de las FPGA, para producir un netlist al nivel de LUTs y bloques lógicos configurables (LUT/CLB). En esa época, los chips eran diseñados con tecnología del estado sólido de baja resolución, por lo que el retardo de rutado tenía poco peso en el retardo de red. Por lo mismo, las herramientas de síntesis utilizaban modelos simples para evaluar los efectos de los retardos de rutado. En los chips actuales con tecnología de sub-micrones, donde el retardo de rutado representa hasta el 80% del retardo de red, estas herramientas no estimarían adecuadamente los tiempos del diseño. A partir de 1996 se consideraron herramientas de síntesis con enfoque físico en el flujo de diseño ASIC. El flujo de diseño de las FPGA también las adoptó a principios del 2000. Estas herramientas de síntesis utilizan información de emplazamiento de los elementos lógicos del diseño asociada al dispositivo objetivo, para estimar los retardos de rutado lo más pronto posible en el proceso de síntesis. Actualmente, las herramientas EDA inician el proceso de síntesis con un paso de síntesis HDL y continúan con un paso de síntesis con enfoque físico. Figura 11: Proceso moderno de síntesis para el flujo de diseño de las FPGA. (Fuente: C. Maxfield, “The Design Warrior´s Guide to FPGAs.pdf, P316,” Elsevier Newnes, USA, 2004. 2.2.3.2 Tecnología de síntesis de Xilinx. La empresa Xilinx ofrece el software ISE (ambiente de software integrado), que conjunta las herramientas de todas las etapas del flujo de diseño (especificación, realización, verificación y depuración del sistema), para las familias de FPGA y CPLD que tiene en el mercado (Virtex-5, Virtex4, Virtex-II PRO, Virtex-II, Virtex, Spartan- III, Spartan-II, CoolRunner-II, CoolRunner-XPLA3, XC9500, etc.). Además de incluir una tecnología de síntesis propietaria, el ISE proporciona una integración directa con los motores de síntesis de las compañías lideres (Leonardo Spectrum, Synplify Pro, Precision RTL Synthesis, etc.), facilitando el uso de múltiples herramientas para obtener el mejor resultado. La tecnología de síntesis de Xilinx (XST), sintetiza descripciones en VHDL, Verilog o una mezcla de ambos lenguajes, para crear un archivo netlist específico de Xilinx (NGC), el cual contienen los datos del diseño lógico y las restricciones que procesa el paso de traducción de la etapa de realización [XilinxISE]. El XST puede recibir núcleos IP en forma de archivos netlist en formato NGC o EDIF (Electronic Data Interchange Format) y a la vez genera un reporte de síntesis (archivo LOG) y los esquemas RTL (archivo NGR) y tecnológico del diseño (incluido en el archivo NGC) En el paso de análisis HDL del flujo de diseño XST, se verifica la escritura correcta del código HDL, reportándose cualquier error de sintaxis. En la síntesis, el XST analiza el código HDL e intenta inferir macros, tales como multiplexores, RAMs, sumadores y restadores, para los cuales se crean realizaciones tecnológicamente eficientes. Para reducir la cantidad de macros inferidos, el XST ejecuta un reconocimiento de recursos compartidos, lo que puede producir una reducción del área así como un incremento en la frecuencia del reloj. El reconocimiento de las máquinas de estado finito (FSM) forma parte del proceso de síntesis. El XST reconoce las FSM independientemente de su estilo de modelación. Para generar la realización más eficiente, el XST hace referencia a las propiedades del proceso de síntesis definidas por el usuario, como la meta y el esfuerzo de optimización, lo que define el algoritmo de codificación FSM más adecuado. Las restricciones controlan el proceso de síntesis HDL, las cuales pueden ser introducidas en el archivo HDL fuente (como atributos del VHDL o meta-comentarios del Verilog), por medio del archivo de restricciones de Xilinx (XCF) o por las propiedades del proceso de síntesis. En la optimización a bajo nivel, el XST transforma los macros inferidos y la lógica general en una realización específica a la tecnología. El proceso puede ser controlado por restricciones de tiempo, como periodo y desplazamiento. Debido a la complejidad del mapeo, no todas las características de la FPGA son utilizadas. 2.2.3.3 Herramientas de verificación. La verificación es la operación con la que se comprueba si la realización de un producto se ajusta a las normas o especificaciones técnicas establecidas, o si posee las condiciones de funcionamiento exigidas. En el ambiente de los diseños electrónicos, la verificación se realiza en diferentes fases del flujo de diseño, para comprobar el cumplimiento de la funcionalidad y rendimiento. Pero mientras las tareas de diseño crecen linealmente con la complejidad, el proceso de verificación crece exponencialmente, consumiendo cada vez más tiempo y recursos. Los chips complejos emplean bloques funcionales, procesadores, periféricos, protocolos e interfaces múltiples, etc., por lo que la verificación debe probar cada elemento y su interacción con los demás, en todas las combinaciones y modos de operación posibles. La verificación incluye la realización de un ambiente de verificación, crear un banco de prueba (test bench), realizar la simulación lógica, analizar los resultados para detectar y aislar los problemas, etc. La verificación es un parte integral de todo proyecto de diseño con FPGA. Gran cantidad de modelos de verificación tradicionales ya no son apropiados para los nuevos diseños con dispositivos de millones de puertas y los métodos modernos deben ser estudiados para determinar su efecto en el tiempo al mercado del producto. 2.2.4 Herramienta de diseño Xilinx-ISE Webpack. La herramienta Xilinx-ISE (Software de desarrollo integrado) es una herramienta de diseño de circuitos profesional que permite realizar esquemáticos y su posterior simulación. La herramienta consta de dos partes: Project Navigator: donde se realizará el diseño del circuito, bien mediante un esquemático o utilizando un lenguaje específico de diseño. ModelSim: donde podrá realizarse la simulación del funcionamiento del circuito y de este modo comprobar si funciona según las especificaciones establecidas. 2.2.4.1 Descripción del entorno de desarrollo ISE Webpack. El entorno de diseño de Xilinx ISE consiste en una herramienta que permite realizar un diseño completo basado en lógica programable, es decir que incluye las etapas necesarias para implementar un diseño, estas etapas son: La entrada de diseño, bien a través de captura esquemática, lenguajes de descripción de hardware como ABEL, VHDL o Verilog, o representación grafica de diagramas de estado (stateCAD/State Bencher). Herramienta de verificación para la obtención de una simulación del sistema, tanto a nivel funcional como de estimación de retardos. La herramienta empleada se denomina ModelsimXE. Por otro lado, también se facilita la generación de banco de prueba para la verificación mediante la herramienta HDL Bencher. Herramientas de implementación donde se permite la especificación de restricciones o indicaciones para realizar una implementación optima sobre el dispositivo lógico programable especificado. Esta herramienta incluye tres etapas principales de diseño: Translate, Map, Place & Route. Herramientas de programación, para permitir descargar el diseño sobre el dispositivo físico, ya sea en una placa de evaluación o bien en la placa definitiva mediante la programación in-siti (en sistema) a través de la programación JTAG. De este modo, es posible probar y depurar el sistema sobre el hardware de forma rápida y flexible, permitiendo tantos cambios como sean necesarios. El entorno de desarrollo posee un aspecto similar a los de los entornos de programación actuales, como puede ser Visual Basic o Visual C, es decir, posee diversas ventanas para la visualización de tareas especificas sobre cada una de ella. En este caso existen cuatro tipos de ventanas: 1. Ventanas de ficheros fuente. En esta ventana se muestran los ficheros fuente utilizados en el diseño y la dependencia de entre ellos. También es aquí donde se elije el tipo de dispositivo donde se desea implementar el diseño, esta ventana posee diversas solapas para visualizar diferentes tipos de información relativa a las fuentes de diseño empleadas. 2. Ventana de procesos. Esta ventana muestra todos los procesos necesarios para la ejecución de cada etapa de diseño. La lista de procesos se modifica dinámicamente dependiente del tipo de fuente seleccionada en la ventana de ficheros fuente. 3. Ventana de edición. Al hacer doble clic sobre un fichero fuente de la ventana de ficheros se abre una ventana de edición para modificar el fichero (en caso de lenguaje HDL), o bien se ejecuta el programa que permite editar el diseño (en caso de diseños esquemáticos o maquinas de estado). 4. Ventana de información, situada en la parte inferior. Muestra los mensajes de error, avisos o información emitida por la ejecución de programas de compilación, implementación, etc. Figura 12: Ventana principal de Xilinx ISE webpack. (Fuente: www.xilinx.com) 2.2.5 Tarjetas de desarrollo para las FPGA. Estas tarjetas han sido diseñadas para ofrecer un sinfín de opciones, de bajo costo para los diseñadores que necesitan de una plataforma flexible para los dispositivos Spartan, o para aquellos que necesitan rápidamente prototipos basados en diseños FPGA. 2.2.5.1 Arquitectura de la tarjeta Digilab II de Digilent. El desarrollo de la tarjeta Digilab II (D2), proporciona un bajo costo y cuenta con una plataforma expandible para el diseño y implementación de circuitos digitales de todo tipo, las características de la tarjeta son: Un FPGA Xilinx XC2S200 Dos reguladores integrados de 2.5 y 3.3 volts cada uno de 1.5 miliamperios cada uno. Un oscilador interno de 50 Megahertz. Un puerto paralelo con base JTAG para la programación y transferencia de datos del usuario. Un puerto serial RS232. Un led de estado y un pulsador de entrada salida. Seis conectores de expansión IDE de 40 pines. La tarjeta D2 ha sido diseñado específicamente para trabajar con Xilinx ISE herramientas de CAD, incluyendo las herramientas libres disponibles en el sitio web Xilinx. En la figura 13 se puede observar el diagrama de bloques de una tarjeta D2 de la Xilinx. Figura13: Diagrama de bloques de una tarjeta Digilab II. (Fuente: www.digilentinc.com) La tarjeta D2 ofrece sólo los dispositivos de apoyo esencial para la Spartan 2, y las rutas de todas las señales de FPGA a habilitados a los conectores de expansión estándar. La D2 incluye dos reguladores de voltaje 2.5VDC y 3.3VDC, un circuito de configuración JTAG que utiliza un cable estándar paralelo, puertos básicos de comunicación, incluyendo un puerto paralelo mejorado y el puerto serie, un oscilador de 50MHz, un pulsador y LED para identificación de I / O. 2.2.5.2 Conectores de expansión. La tarjeta D2 ha sido diseñada para servir como base de diversas tarjetas periféricas. Los conectores de expansión de la placa de la D2, son estándar de 40 pines, ofrecen la tensión de alimentación no regulada (VU), de 3,3 V, GND, y 37 señales FPGA para las uniones periféricas. Figura 14: Conectores de expansión IDE de placa Digilab II. (Fuente: www.digilentinc.com) La tarjeta dispone de seis conectores de expansión, cada uno cuenta con un pin de GND (Pin 1), uno de alimentación no regulada (Pin 2), y un pin encaminado hacia la clavija de 3.3 vol. (Pin 3). Los pines del 4 al 40 están directamente enrutados a la FPGA. Los conectores están organizados en pares A & B, C& D, and E & F, y están conectados en el borde de la tarjeta, los pares A & E y B & F comparten conexiones de pin idénticos a el FPGA, los conectores C & D tiene todos los pines enrutados por separado hacia el FPGA, el PQ208 enruta 122 señales hacia los conectores de expansión. En la figura 15 se muestran las conexiones del empaquetado PQ208 para los conectores de expansión. Figura 15: Detalle de los conectores de expansión en la tarjeta Digilab II. (Fuente: www.digilentinc.com) El diagrama de bloques de las conexiones entre la Spartan II y los conectores de expansión de la Digilab 2 se muestran a continuación. Figura 16: Arquitectura en bloques de la tarjeta Digilab II. (Fuente: www.digilentinc.com) 2.2.5.3 Puerto paralelo. La tarjeta de desarrollo Digilab 2 utiliza un conector de puerto paralelo DB-25 para enviar las señales de programación, este conector enruta los pines del puerto paralelo del computador hacia a la FPGA, siguiendo el protocolo EPP (puerto paralelo mejorado) contenida en el estándar IEEE 1284. Un buffer de tres estados, controlado por un interruptor, determina si el puerto JTAG o el puerto EPP están activados. Con este circuito, la FPGA se pueden configurar mediante el protocolo JTAG en el cable paralelo. El mismo cable puede ser utilizado para mover datos entre la tarjeta y el ordenador utilizando el protocolo EPP de alta velocidad. El puerto paralelo EPP sigue las especificaciones de la IEEE 1284, las conexiones del JTAG y del PPE se muestra en la figura 17. . Figura 17: Señales y conexiones del puerto paralelo. (Fuente: www.digilentinc.com) 2.2.5.4 Oscilador La tarjeta D2 contiene un oscilador de 50 MHz, permitiendo trabajar con frecuencias de reloj en el sistema desde DC hasta 350MHz (esto se logra usando los DLL interno con que cuenta los FPGA Spartan II). El oscilador está conectado de manera permanente al pin GCK0 (pin 80). 2.2.6 Dispositivos electrónicos. 2.2.6.1 Diodo emisor de luz. El LED (Light-Emitting Diode: Diodo Emisor de Luz), es un dispositivo semiconductor que emite luz incoherente de espectro reducido cuando se polariza de forma directa la unión PN en la cual circula por él una corriente eléctrica . Este fenómeno es una forma de electroluminiscencia, el LED es un tipo especial de diodo que trabaja como un diodo común, pero que al ser atravesado por la corriente eléctrica, emite luz. Este dispositivo semiconductor está comúnmente encapsulado en una cubierta de plástico de mayor resistencia que las de vidrio que usualmente se emplean en las lámparas incandescentes. Aunque el plástico puede estar coloreado, es sólo por razones estéticas, ya que ello no influye en el color de la luz emitida. Usualmente un LED es una fuente de luz compuesta con diferentes partes, razón por la cual el patrón de intensidad de la luz emitida puede ser bastante complejo. 2.2.6.2 Puente rectificador. Un puente rectificador o puente de diodos, es un circuito integrado que contiene cuatro diodos interconectados, formando un cuadrado con los vértices accesibles. Este circuito sirve para rectificar corriente alterna. En la figura 18 se puede ver el esquema del circuito, el aspecto exterior y el modo de funcionamiento. Figura 18: Funcionamiento del puente rectificador. (Fuente: http://www.tecnologiaseso.es) En el semiciclo positivo de la señal alterna de entrada, conducen los diodos de la parte superior del cuadro y desvían la corriente hacia el positivo de la salida. En el semiciclo negativo, los dos diodos de la parte inferior desvían la corriente hacia el negativo. 2.2.6.3 Display de 7 segmentos. El “display de 7 segmentos” es un dispositivo usado para presentar información de forma visual, específicamente un dígito decimal del 0 (cero) al 9 (nueve), el display consta de 7 LED's (Light Emisor Diode), uno por cada segmento, que se encenderán o apagarán dependiendo de la información que se les envíe. La disposición de los segmentos se muestra en la figura 19. Un led tiene dos extremos, ánodo y cátodo, como en total el display tiene 8 leds, debería tener 16 extremos (8 ánodos y 8 cátodos), sin embargo el encapsulado solo tiene 10. Esto se hace para reducir el tamaño del encapsulado y se logra de la siguiente manera. Los 8 led se interconectan internamente de tal forma que solo se pueda acceder a uno de los dos extremos de cada led. El extremo sobrante de cada led se conecta internamente con los demás, y este punto de unión se encuentra disponible desde el exterior del encapsulado, por tanto existen dos tipos de display de 7 segmentos: 1. Ánodo Común: es aquel donde los ánodos de todos los leds se conectan internamente al punto de unión U y los cátodos se encuentran disponibles desde afuera del integrado. 2. Cátodo Común: es aquel donde los cátodos de todos los leds se conectan internamente al punto de unión U y los ánodos se encuentran disponibles desde afuera del integrado. Figura 19: Disposición de los segmentos en el display. (Fuente: www.tecnoface.com) 2.2.6.4 Convertidor análogo digital A/D. Los convertidores A/D son dispositivos electrónicos que establecen una relación uno a uno, entre el valor de la señal en su entrada y la palabra digital obtenida en su salida. La relación se establece en la mayoría de los casos, con la ayuda de una tensión de referencia. La conversión analógica a digital tiene su fundamento teórico en el teorema de muestreo y en los conceptos de cuantificación y codificación. Una primera clasificación de los convertidores A/D, es la siguiente: Conversores de transformación directa. Conversores con transformación (D/A) intermedia, auxiliar. 2.2.6.5 Teclado matricial. Un teclado matricial es un simple arreglo de botones conectados en filas y columnas, de modo que se pueden leer varios botones con el mínimo número de pines requeridos. Un teclado matricial 4x4 solamente ocupa 4 líneas de un puerto para las filas y otras 4 líneas para las columnas, de este modo se pueden leer 16 teclas utilizando solamente 8 líneas de un micro controlador. Si asumimos que todas las columnas y filas inicialmente están en alto (1 lógico), la pulsación de un botón se puede detectar al poner cada fila a en bajo (0 lógico) y checar cada columna en busca de un cero, si ninguna columna está en bajo entonces el 0 de las filas se recorre hacia la siguiente y así secuencialmente. 2.2.6.6 Interruptores. Un interruptor eléctrico es un dispositivo utilizado para desviar o interrumpir el curso de una corriente eléctrica. En el mundo moderno las aplicaciones son innumerables, van desde un simple interruptor que apaga o enciende un bombillo, hasta un complicado selector de transferencia automático de múltiples capas controlado por computadora. Su expresión más sencilla consiste en dos contactos de metal inoxidable y el actuante. Los contactos, normalmente separados, se unen para permitir que la corriente circule. El actuante es la parte móvil que en una de sus posiciones hace presión sobre los contactos para mantenerlos unidos. 2.2.6.7 Generador de señales. Un generador de funciones es un instrumento versátil que genera diferentes formas de onda cuyas frecuencias son ajustables en un amplio rango. Las salidas más frecuentes son ondas senoidales, triangulares, cuadradas y diente de sierra. Las frecuencias de estas ondas pueden ser ajustadas desde una fracción de hertz hasta varios cientos de kilo hertz. Un generador de funciones puede fijar la fase de un generador de funciones con una armónica de una onda senoidal del otro generador, mediante el ajuste de fase y amplitud de las armónicas permite general casi cualquier onda obteniendo la suma de la frecuencia fundamental generada por un generador de funciones de los instrumentos y la armónica generada por el otro. El generador de funciones también se puede fijar en fase a una frecuencia estándar, con lo que todas las ondas de salida generadas tendrán la exactitud y estabilidad en frecuencia de la fuente estándar. El generador de funciones también puede proporcionar ondas a muy bajas frecuencias. Ya que la frecuencia baja de un oscilador RC es limitada, la figura ilustrada otra técnica. Este generador entrega ondas senoidales triangulares y cuadradas con un rango de frecuencias de 0.01 Hz hasta 100 kHz. La red de control de frecuencia está dirigida por el selector fino de frecuencia en el panel frontal del instrumento o por un voltaje de control aplicado externamente. El voltaje de control de frecuencia regula dos fuentes de corriente.