DISEÑO DE PROCESADORES DEDICADOS Práctica 3 CIDETEC

Anuncio

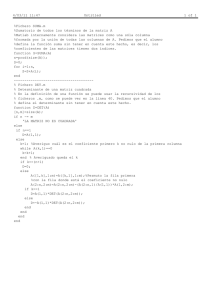

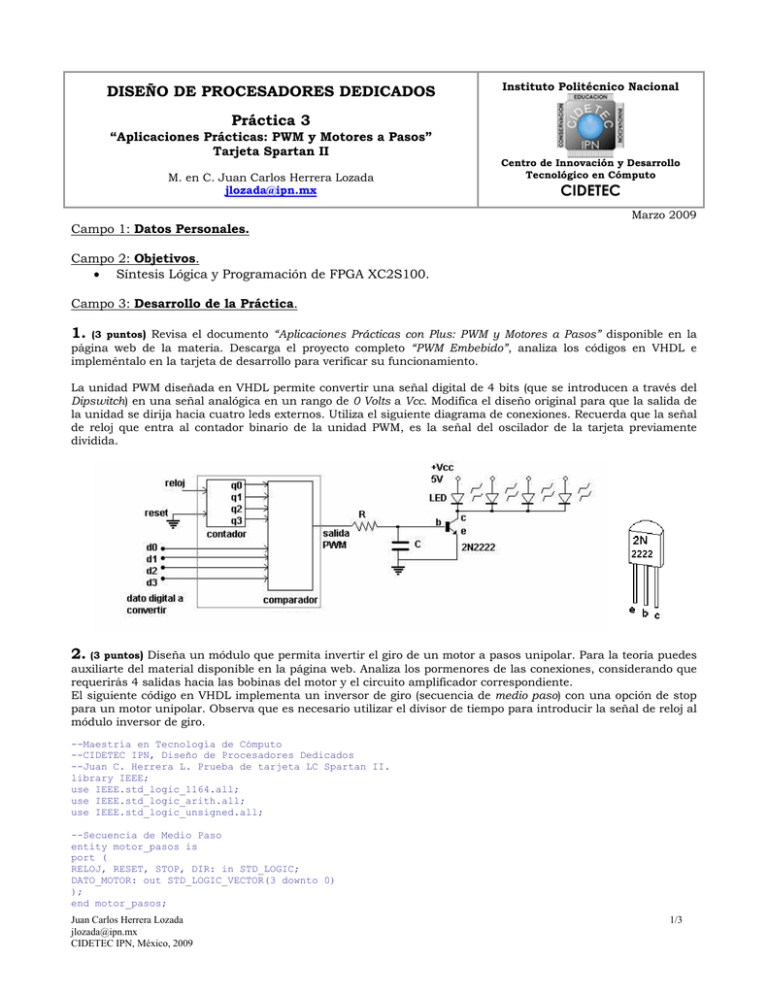

DISEÑO DE PROCESADORES DEDICADOS Instituto Politécnico Nacional Práctica 3 “Aplicaciones Prácticas: PWM y Motores a Pasos” Tarjeta Spartan II M. en C. Juan Carlos Herrera Lozada [email protected] Campo 1: Datos Personales. Centro de Innovación y Desarrollo Tecnológico en Cómputo CIDETEC Marzo 2009 Campo 2: Objetivos. • Síntesis Lógica y Programación de FPGA XC2S100. Campo 3: Desarrollo de la Práctica. 1. (3 puntos) Revisa el documento “Aplicaciones Prácticas con Plus: PWM y Motores a Pasos” disponible en la página web de la materia. Descarga el proyecto completo “PWM Embebido”, analiza los códigos en VHDL e impleméntalo en la tarjeta de desarrollo para verificar su funcionamiento. La unidad PWM diseñada en VHDL permite convertir una señal digital de 4 bits (que se introducen a través del Dipswitch) en una señal analógica en un rango de 0 Volts a Vcc. Modifica el diseño original para que la salida de la unidad se dirija hacia cuatro leds externos. Utiliza el siguiente diagrama de conexiones. Recuerda que la señal de reloj que entra al contador binario de la unidad PWM, es la señal del oscilador de la tarjeta previamente dividida. 2. (3 puntos) Diseña un módulo que permita invertir el giro de un motor a pasos unipolar. Para la teoría puedes auxiliarte del material disponible en la página web. Analiza los pormenores de las conexiones, considerando que requerirás 4 salidas hacia las bobinas del motor y el circuito amplificador correspondiente. El siguiente código en VHDL implementa un inversor de giro (secuencia de medio paso) con una opción de stop para un motor unipolar. Observa que es necesario utilizar el divisor de tiempo para introducir la señal de reloj al módulo inversor de giro. --Maestría en Tecnología de Cómputo --CIDETEC IPN, Diseño de Procesadores Dedicados --Juan C. Herrera L. Prueba de tarjeta LC Spartan II. library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_arith.all; use IEEE.std_logic_unsigned.all; --Secuencia de Medio Paso entity motor_pasos is port ( RELOJ, RESET, STOP, DIR: in STD_LOGIC; DATO_MOTOR: out STD_LOGIC_VECTOR(3 downto 0) ); end motor_pasos; Juan Carlos Herrera Lozada [email protected] CIDETEC IPN, México, 2009 1/3 architecture motor_arch of motor_pasos is type state_type is (INICIA, CERO, UNO, DOS, TRES, CUATRO, CINCO, SEIS, SIETE); signal estado, estado_siguiente: state_type; begin arranque_motor:process (RELOJ, RESET) begin if RESET='0' then estado <= INICIA; elsif RELOJ='1' and RELOJ'event then estado <= estado_siguiente; end if; end process arranque_motor; estados_motor:process (estado, DIR, STOP) begin case estado IS when INICIA => if STOP='0' then estado_siguiente <= INICIA; elsif DIR='1' then estado_siguiente <= CERO; else estado_siguiente <= SIETE; end if; when CERO => if STOP='0' then estado_siguiente <= CERO; elsif DIR='1' then estado_siguiente <= UNO; else estado_siguiente <= SIETE; end if; when UNO => if STOP='0' then estado_siguiente <= UNO; elsif DIR='1' then estado_siguiente <= DOS; else estado_siguiente <= CERO; end if; when DOS => if STOP='0' then estado_siguiente <= DOS; elsif DIR='1' then estado_siguiente <= TRES; else estado_siguiente <= UNO; end if; when TRES => if STOP='0' then estado_siguiente <= TRES; elsif DIR='1' then estado_siguiente <= CUATRO; else estado_siguiente <= DOS; end if; when CUATRO => if STOP='0' then estado_siguiente <= CUATRO; elsif DIR='1' then estado_siguiente <= CINCO; else estado_siguiente <= TRES; end if; when CINCO => if STOP='0' then estado_siguiente <= CINCO; elsif DIR='1' then estado_siguiente <= SEIS; else estado_siguiente <= CUATRO; end if; when SEIS => if STOP='0' then estado_siguiente <= SEIS; elsif DIR='1' then estado_siguiente <= SIETE; else estado_siguiente <= CINCO; end if; when SIETE => if STOP='0' then Juan Carlos Herrera Lozada [email protected] CIDETEC IPN, México, 2009 2/3 estado_siguiente <= SIETE; elsif DIR='1' then estado_siguiente <= CERO; else estado_siguiente <= SEIS; end if; END CASE; end process estados_motor; salida:process(estado) begin case estado IS when INICIA => DATO_MOTOR when CERO => DATO_MOTOR when UNO => DATO_MOTOR when DOS => DATO_MOTOR when TRES => DATO_MOTOR when CUATRO => DATO_MOTOR when CINCO => DATO_MOTOR when SEIS => DATO_MOTOR when SIETE => DATO_MOTOR when others => NULL; END CASE; end process salida; <= <= <= <= <= <= <= <= <= "0000"; "1000"; "1100"; "0100"; "0110"; "0010"; "0011"; "0001"; "1001"; end motor_arch; 3. (4 puntos) Modifica el diseño para que tu motor pueda dar un paso por cada pulso de reloj introducido a través de un push button. Investiga qué es un circuito anti-rebotes y cómo lo puedes implementar en VHDL. El recorrido debe poder realizarse en ambos sentidos, por lo que en tu diseño debes conservar la variable DIR (dirección de giro). Campo 4: Conclusiones individuales. Juan Carlos Herrera Lozada [email protected] CIDETEC IPN, México, 2009 3/3