Ejercicio 1. Sistemas Digitales II. NOMBRE: 1) (1 pto) Determine el

Anuncio

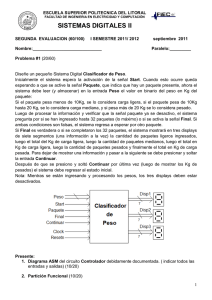

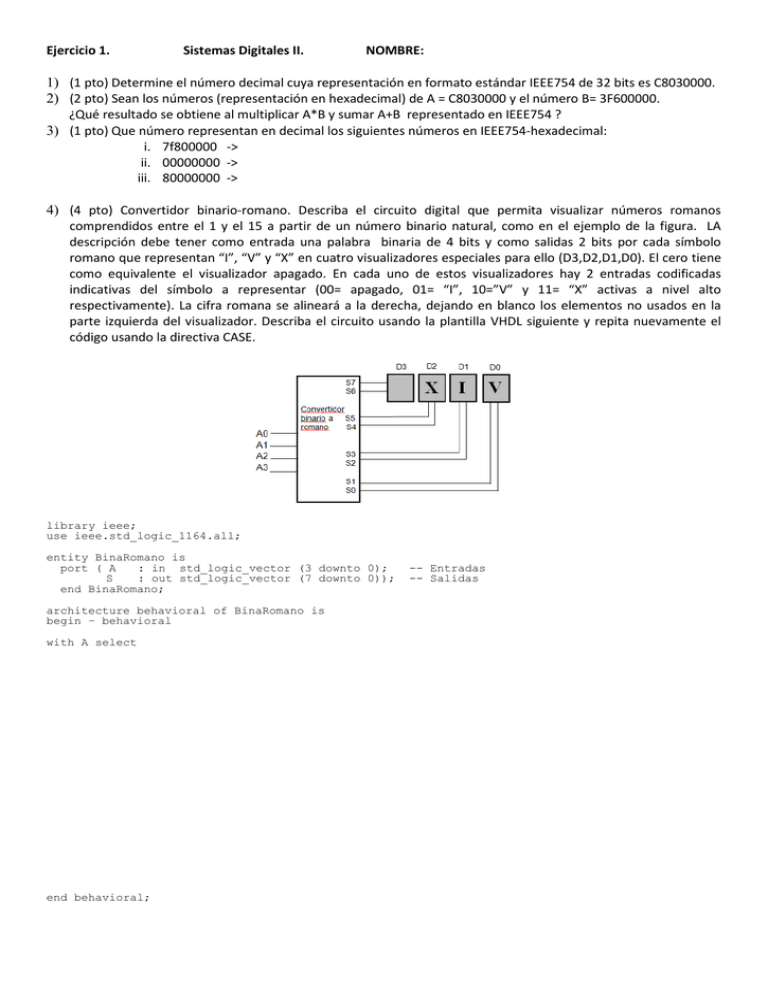

Ejercicio 1. Sistemas Digitales II. NOMBRE: 1) (1 pto) Determine el número decimal cuya representación en formato estándar IEEE754 de 32 bits es C8030000. 2) (2 pto) Sean los números (representación en hexadecimal) de A = C8030000 y el número B= 3F600000. ¿Qué resultado se obtiene al multiplicar A*B y sumar A+B representado en IEEE754 ? 3) (1 pto) Que número representan en decimal los siguientes números en IEEE754-hexadecimal: i. 7f800000 -> ii. 00000000 -> iii. 80000000 -> 4) (4 pto) Convertidor binario-romano. Describa el circuito digital que permita visualizar números romanos comprendidos entre el 1 y el 15 a partir de un número binario natural, como en el ejemplo de la figura. LA descripción debe tener como entrada una palabra binaria de 4 bits y como salidas 2 bits por cada símbolo romano que representan “I”, “V” y “X” en cuatro visualizadores especiales para ello (D3,D2,D1,D0). El cero tiene como equivalente el visualizador apagado. En cada uno de estos visualizadores hay 2 entradas codificadas indicativas del símbolo a representar (00= apagado, 01= “I”, 10=”V” y 11= “X” activas a nivel alto respectivamente). La cifra romana se alineará a la derecha, dejando en blanco los elementos no usados en la parte izquierda del visualizador. Describa el circuito usando la plantilla VHDL siguiente y repita nuevamente el código usando la directiva CASE. library ieee; use ieee.std_logic_1164.all; entity BinaRomano is port ( A : in std_logic_vector (3 downto 0); S : out std_logic_vector (7 downto 0)); end BinaRomano; architecture behavioral of BinaRomano is begin – behavioral with A select end behavioral; -- Entradas -- Salidas 5) (2p) Dado el VHDL a continuación, obtener el diagrama de estados library ieee; use ieee.std_logic_1164.all; entity maquina is port( clk : in input : in reset : in enable : in output : out end entity; std_logic; std_logic; std_logic; std_logic; std_logic_vector (1 downto 0)); architecture rtl of maquina is type tipo_estado is (s0, s1, s2, s3); signal estado : tipo_estado; begin process (clk, reset) begin if reset = '0' then estado <= s0; elsif (clk’event='1' and clk'1') then if enable='1' then case estado is when s0=> if input = '1' then estado <= s1; else estado <= s0; end if; when s1=> if input = '1' then estado <= s2; else estado <= s1; end if; when s2=> if input = '1' then estado <= s3; else estado <= s2; end if; when s3 => if input = '1' then estado <= s0; else estado <= s3; end if; end case; end if; end if; end process; process (estado) begin case estado when when when when end case; end process; is s0 s1 s2 s3 => => => => output output output output <= <= <= <= "01"; "00"; "00"; "10"; end rtl; OPCIONAL: Haga un proyecto en Quartus con la máquina de estados anterior. Genere el banco de pruebas correspondiente. Inserte los estímulos para el caso favorable y un caso no favorable. Ponga en el ejercicio el código VHDL y la pantalla con el resultado de la simulación.