11. Capítulo 6_Diseño y simulación del dispositivo de medida

Anuncio

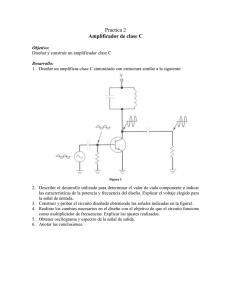

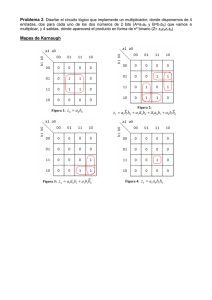

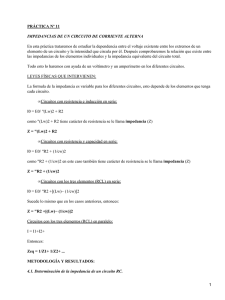

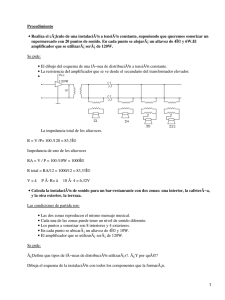

Capítulo 6: Diseño y simulación del dispositivo de medida. Este capítulo se centra en el diseño y simulación de los distintos módulos que conforman el dispositivo de bioimpedancia. Como se ha comentado en el apartado anterior, el dispositivo dispone de tres grandes módulos, los cuales se pueden subdividir en otros módulos de funcionalidad más básica. A continuación se muestra un esquema donde se descomponen estos módulos principales en módulos más simples. Figura 27: Diagrama de bloques del sistema de bioimpedancia. Las distintas etapas o subetapas que componen el sistema de medida de bioimpedancia se describen detalladamente a lo largo de este capítulo. Se nombran a continuación las distintas etapas que componen el sistema, divididas de acuerdo a la función a desempeñar. El diseño del dispositivo completo se podría dividir en 3 etapas principales. • ETAPA 1: GENERACION DE SEÑAL • ETAPA 2: FUENTE DE CORRIENTE • ETAPA 3: SISTEMA DE DETECCION La etapa 3 se puede dividir a su vez en distintos bloques según la función que desempeña cada uno: 1) ETAPA 3.1: ETAPA DE AMPLIFICACION 2) ETAPA 3.2: GENERACION DE SEÑAL EN FASE Y EN CUADRATURA 3) ETAPA 3.3: ETAPA MULTIPLICACION DE SEÑALES 4) ETAPA 3.4: ETAPA DE FILTRADO 5) ETAPA 3.5: ETAPA DE CONVERSION (A/D) 6.1.-ETAPA 1: GENERACION DE SEÑAL En esta primera etapa se generará una señal de referencia senoidal muy precisa de forma digital. Para desempeñar esta función la etapa se compone básicamente de dos elementos. Uno de ellos es un dispositivo DDS, el otro es una fuente de alimentación. El DDS (de sus siglas en inglés Direct Digital Synthesis) será alimentado por la fuente de alimentación externa. Esta fuente estará aislada para de esta forma proteger de sobretensiones y sobreintensidades al paciente al cual posteriormente se le inyectará corriente. Para alimentar al sistema se debe tener en cuenta la energía que necesita el DDS para funcionar. Esta primera etapa juega un papel primordial en el sistema de bioimpedancia completo, ya que de la calidad de generación de la señal dependerá directamente la corriente que será aplicada al tejido. Existen múltiples métodos que pueden ser aplicables para la obtención de la señal, ya sea para obtener una señal sinusoidal o una señal pulsátil. Para esta aplicación concreta se ha decidido usar la Síntesis Digital Directa (DDS) por ser la técnica más novedosa, completa y la que mejor calidad de señal genera. Se han descartado técnicas de mayor coste como por ejemplo el uso de DSP (Digital Signal Processor) o el uso de FPGAs para la generación de señal. A continuación se describirá detalladamente en que se basa la técnica de Síntesis Digital Directa de señal. 6.1.1. Síntesis digital directa Es la técnica de síntesis de frecuencia desarrollada más recientemente y está caracterizada por su velocidad. Todas las otras técnicas de generación de señal se basan en alguna clase de oscilador cuya salida es controlada por el sintetizador. El DDS es único porque es digitalmente determinístico, las mismas entradas siempre producirán invariablemente las mismas salidas. La señal que este genera, se sintetiza desde una definición digital del resultado deseado. Un DDS utiliza lógica y memoria para construir digitalmente la señal de salida deseada, también dispone de un dispositivo de conversión de datos para traducir los datos del dominio digital al analógico. De esta manera, el método DDS de reconstrucción de señal, es casi enteramente digital pudiéndose conocer y controlar en cualquier momento parámetros como amplitud, frecuencia y fase de la señal generada. La resolución que proporciona el DDS está determinada por la frecuencia de reloj dividida sobre 2 N (número de bits en la palabra de control), entonces la frecuencia de salida es determinada mediante la siguiente fórmula: f out = Δ fase∗CLKIN 232 Donde: Δfase = valor de los 32 bits de la palabra de control. CLKIN = frecuencia de reloj de referencia en MHz. fOUT = frecuencia de la señal de salida en MHz. Las ventajas del DDS incluyen una conmutación muy rápida, típicamente menor a los microsegundos, escalones muy finos, cambios de fase continuos, gran flexibilidad como demodulador y su tamaño es francamente pequeño. Pero este dispositivo también posee desventajas, entre las cuales la más importante es acerca de su rango de operación, ya que está restringido por el teorema de Nyquist, limitando la salida aproximadamente al 45% de la frecuencia de reloj a la cual la lógica puede operar. La segunda limitación es la pureza espectral, la cual se ve afectada a medida que el ancho de banda de operación aumenta. La arquitectura del DDS se muestra en la figura 28. Figura 28: Diagrama de bloque básico de un DDS. (Adaptación del datasheet del componente) En concreto el DDS que se usará en el sistema de bioimpedancia es el AD9850, se ha elegido este componente porque permite una precisión muy alta en la frecuencia de salida, con una resolución de 0.0291Hz y con un reloj de referencia de 125MHz. El AD9850 proporciona una señal de amplitud 0.3 V y un nivel de continua de 0.35 V. Por sus ventajas en desempeño, tamaño y rapidez este dispositivo es usado para suministrar la forma de onda requerida por la fuente de corriente con una gran precisión. Su configuración se muestra en la figura 29. Figura 29: Configuración y conexión del DDS AD9850 (Adaptación del datasheet del componente). La programación de la frecuencia de salida es realizada mediante la carga en serie de los 40 bits de datos requeridos, 32 para el valor de la frecuencia, 4 de control y 4 para el valor de la fase. Después de que los 40 bits de datos han sido enviados al DDS, un pulso FQ_UD se encarga de actualizar la frecuencia y la fase de salida. El dispositivo también cuenta con 5 bits para la modulación de fase controlada digitalmente, permite el desplazamiento de fase en incrementos de 180º, 90º, 45º, 22.5º y 11.25º y una combinación de las mismas. 6.2. ETAPA 2: FUENTE DE CORRIENTE En esta etapa el dispositivo emplea la señal senoidal antes generada por el DDS. Esta señal se hace circular por una fuente que genera una corriente senoidal de la misma frecuencia que la generada por el DDS y una amplitud constante prefijada. La corriente que genere esta fuente debe estar bien controlada y definida ya que de ésta dependerá la corriente que se inyecta al paciente. También debe tener una amplitud fija con la variación de la frecuencia para que el valor de corriente inyectada sea conocido en todo el dominio de la frecuencia. Una fuente de corriente puede modelarse idealmente como una fuente de corriente en paralelo con la impedancia de la fuente Zs, como se muestra en la figura 30. Los cambios en la corriente que circulará por la impedancia de carga serán más pequeños en tanto que la impedancia de la fuente Zs sea más alta, por tanto nos interesa tener una fuente de corriente con una impedancia relativamente alta para que cuando se modifique la impedancia de carga la corriente que se inyecta sea prácticamente la misma. Esta circunstancia puede observarse de forma clara en la siguiente ecuación. I L =I s ( Zs ) Z s+Z L Figura 30: Modelado de una fuente de corriente. Como ya se ha comentado la solución ideal para la fuente de corriente, es adoptar un diseño tal que la impedancia Zs sea tan alta que al variar la impedancia de carga en el rango esperado la corriente de salida no cambie significativamente. El nivel máximo de corriente que se inyectará al paciente está especificado en normas internacionales (IEC 601.1). Por otro lado, se debe tener en cuenta que la relación señal-ruido que se obtiene en las medidas será tanto mayor cuanto mayor sea el nivel de la señal inyectada, por lo que en un principio parece interesante trabajar con los niveles de señal más grandes posibles. Un factor que puede limitar el nivel de señal es la posibilidad de saturación de los circuitos de detección de tensión. Se debe tener especial cuidado a la hora de diseñar el sistema de inyección para que en ningún caso inyecte corriente continua al paciente. La inyección de corriente continua, aunque sea de bajo nivel, durante periodos de tiempo largos puede causar quemaduras en la piel debido a procesos de electrólisis en la interfaz electrodo-piel. Debemos tener presente que incluso la corriente de polarización de los amplificadores operacionales que eventualmente pudieran utilizarse para la detección de la tensión sobre el cuerpo puede producir este efecto en la piel del paciente por lo cual es necesario desacoplar en continua mediante condensadores. Distintos autores han estudiado e implementado varios diseños y enfoques de distintas fuentes de corriente para el uso en sistemas de bioimpedancia, se han estudiado por ejemplo transportadores de corriente, topología Howland, etc. Se puede concluir que la mayoría de las implementaciones operan muy bien en frecuencias del orden de los kHz, pero la impedancia de salida decrece cercana a 1 Mhz. 6.2.1. Diseño del circuito Las fuentes de corriente controladas por tensión (VCCS) con realimentación positiva son ampliamente utilizadas en bioimpedancia, un ejemplo de éstas es la fuente de corriente tipo Howland, en la cual se centra el desarrollo de hardware de la fuente de corriente del presente proyecto. El circuito Howland es una implementación de un único amplificador operacional, de ganancia unitaria, como se observa en la figura 31. Los valores de las resistencias deben ser ajustados cuidadosamente para obtener la mayor precisión posible. El problema para este tipo de fuentes, recae en mayor proporción en frecuencias por encima de los valores DC, donde los efectos reactivos empiezan a ser importantes debido, por ejemplo, a las capacidades parásitas de las resistencias. Como consecuencia a esta reacción la impedancia de salida del circuito decrece con el aumento de la frecuencia de operación. Además de esto, si la ganancia excede la unidad, la ganancia de salida de la fuente podría llegar a ser negativa si existe una impedancia de carga muy grande y de esta forma el circuito llegaría a oscilar. Dicha situación puede ocurrir en el caso de que un electrodo se encuentre desconectado. El uso de resistencias de precisión se hace indispensable. Figura 31: Fuente de corriente Howland. Figura 32: Fuente Howland sin impedancia de carga ni resistencia de entrada. Figura 33: Circuito equivalente de la fuente de corriente Howland Son de vital importancia las siguientes ecuaciones para comprender el funcionamiento de la fuente de corriente. Para hallar la corriente que será suministrada a la carga se plantean las ecuaciones mostradas a continuación, teniendo en cuenta la figura 32. V +. =V −. =V i V i= Ii= R2 V R 2+R4 O V i−V o −R4 = V R3 R3 R2 i Zi= V i −R2 R3 = Ii R4 Teniendo en cuenta las anteriores ecuaciones y las figuras 31 y 33, tenemos que: Ii= Vi R2 R3−R 4 R L = V Z i RL R1 R2 R3−R1 R4 R L− R2 R 3 R L i R1+ Z i+R L IL= I L= Zi I Z i+ RL i R 2 R3 V R1 R 2 R 3−R1 R 4 R L −R 2 R3 R L i Si RL <<R1,R2,R3,R4 la ultima ecuación se simplifica, obteniendo: I L= Vi R1 El esquema completo utilizado para la generación de corriente constante, se muestra en la figura 34, el cual se basa en el amplificador operacional OPA354 y en la utilización de resistencias de precisión. Este cumple el análisis matemático realizado anteriormente, pero al implementar dos etapas de fuente de corriente idénticas proporciona el doble de corriente, lo cual se describe como: 2V I L= i R1 Figura 34: Fuente de corriente. Este tipo de fuente de corriente basada en la topología Howland, presenta las características suficientes para su adopción como fuente de corriente en aplicaciones de bioimpedancia ya que proporciona una impedancia de salida mínima de 540K a 1 Khz. En la simulación se ha usado una fuente senoidal ideal, este elemento realizará la función que desempeñaría el DDS, la señal que genera la fuente senoidal (DDS) se inyecta en la etapa de la fuente de corriente para conseguir una corriente prácticamente constante en la salida. Para ver las prestaciones de la fuente en corriente se realizó un barrido en frecuencia con el objeto de comprobar la dispersión que tiene este parámetro en función de la frecuencia. El AD9850 proporciona una señal de amplitud 0.3 V y un nivel de continua de 0.35 V. Con esta tensión de entrada y el planteamiento matemático antes realizado se estima una corriente de carga de: 1.3V I L≈ ≈143μ A 9,09 k Para comprobar esto en todas las frecuencias se ha realizado un barrido en frecuencia desde los 5khz hasta 5Mhz, mostrado en la figura 35, y hasta 1 Mhz en la figura 36. Usando la fuente VAC de las librerías del programa simulación se puede simular la función del DDS, configurada esta fuente con los parámetros que entregaría el DDS (AD9850). Figura 35: Intensidad de salida, barrido hasta 5Mhz. En esta primera gráfica se observa la estabilidad de la fuente de corriente frente a la frecuencia. Hasta la frecuencia de 1Mhz, frecuencia máxima a la que va a trabajar el dispositivo, el valor de la fuente de corriente varía muy poco. Para verlo más claramente se mostrará otra simulación pero esta vez hasta la frecuencia de 1Mhz para tener más resolución de la medida. Figura 36: Intensidad de salida, barrido hasta 1Mhz. En esta segunda simulación de la fuente vemos como efectivamente la diferencia entre el valor mínimo de corriente que se inyecta en las frecuencias más bajas en comparación con los valores de la frecuencia más alta está en torno a 0,6uA, la cual se corresponde un error máximo admisible inferior al 0,5%. La intensidad que inyectaría la fuente sería de unos 164,5uA. Como se puede ver en la figura 36, este valor podría ser un valor demasiado pequeño para obtener medidas de calidad debido a la pequeña amplitud de la corriente. Si se inyecta una señal mayor, evidentemente, se tendrían en los extremos del instrumento de detección de señal una amplitud mayor, siendo así más fácil de tratar en su posterior procesamiento. Otra ventaja es que al ser una señal mayor que la inicial (164,5uA) esta última será más robusta ante los ruidos que se pudieran introducir. Por este motivo se ha decidido añadir una nueva etapa amplificadora. Al circuito anterior se ha añadido otro amplificador operacional pero esta vez en una configuración de amplificador inversor, de esta forma se tendría control sobre la amplitud de la fuente de inyección con tan solo una resistencia. Esto puede ser de gran valor para adaptar la fuente a diferentes pacientes u otras aplicaciones de bioimpedancia. Por lo tanto la relación simplificada de la intensidad de salida sería: I L ≈Vi / R24 La tensión de entrada en la etapa amplificadora es 1,65V como se puede ver en la siguiente simulación (figura 37). Figura 37: Barrido (AC) en frecuencia de la tensión de salida. Por lo tanto, como se ha comentado, modificando solo R24 tendremos el control sobre la intensidad de carga. En la figura 38 se muestra el circuito con la nueva etapa. La siguiente tabla establece los distintos valores de resistencia y la intensidad teórica que se debería obtener. Para cada resistencia de la tabla se han simulado tres modelos de bioimpedancia similares a valores reales, con el objeto de analizar la sensibilidad del diseño al valor de la impedancia medida. Se han establecido las siguientes bioimpedancias para dicho análisis: Z a : Ra=671.3 ohm ; Rb =2227.3 ohm ; C=69 nF Z b : Ra =500 ohm ; Rb=3000 ohm ; C=80 nF Z c : Ra =750 ohm ; Rb=1800 ohm; C =50 nF Figura 38: Fuente de corriente con la etapa de amplificación añadida. I L ≈1,65 /R24 R24(Ohm) 1000 1500 2000 3000 3300 5000 IL. TEORICA(mA) 1,65 1,10 0,83 0,55 0,50 0,33 A continuación se mostraran las simulaciones con los distintos valores de R24 y las distintas impedancias (Za,Zb y Zc). R24=1,5k Figura 39: Intensidad de salida usando tres impedancias distintas (Za, Zb, Zc) con R24=1,5k R24=2k Figura 40: Intensidad de salida usando tres impedancias distintas (Z a, Zb, Zc) con R24=2k R24=3k Figura 41: Intensidad de salida usando tres impedancias distintas (Z a, Zb, Zc) con R24=3k R24=3.3k Figura 42: Intensidad de salida usando tres impedancias distintas (Za, Zb, Zc) con R24=3,3k R24=5k Figura 43: Intensidad de salida usando tres impedancias distintas (Z a, Zb, Zc) con R24=5k Con estas simulaciones queda demostrado que con la nueva etapa y modificando única y exclusivamente la resistencia R24 podemos tener control sobre la intensidad que se inyecta al paciente. En las tres bioimpedancias de prueba, la corriente que inyecta es prácticamente la misma, con un error alrededor del 0.5%. Los valores obtenidos en las simulaciones están dentro de los márgenes establecidos en las especificaciones. 6.3. ETAPA 3: SISTEMA DE DETECCION En esta etapa se detectará la señal de tensión una vez la corriente ha recorrido el segmento biológico. Esta etapa engloba otras etapas de niveles más básicos. La función de la misma en su conjunto es detectar la señal, generar señales coherentes en fase y cuadratura para, a través de un multiplicador analógico, demodular estas señales y separar las dos componentes de la medida. Al multiplicar dos señales de la misma frecuencia aparece una señal de continua y una señal del doble de la frecuencia de las señales originales. La señal de continua contiene información de la fase y de la amplitud de las señales de partida, y su procesado permite extraer el módulo y la fase de la impedancia, como veremos más adelante. Para realizar su procesado, las señales son convertidas a un entorno digital mediante un ADC. A continuación se describirá de forma general el sistema completo incluyendo todas las subetapas que lo componen para luego hacer hincapié en cada una de estas etapas por separado y así poder comprender mejor el funcionamiento completo del sistema. La figura 44 muestra un diagrama del funcionamiento del método de detección completo. Figura 44: Diagrama de bloques del sistema de detección. El principio básico de este enfoque está basado en dos demodulaciones coherentes de la señal de entrada. La tensión entre los electrodos de tensión en función del tiempo puede ser representada como VIN(t)= Z*I*sin(ω0t+θ), donde I es la amplitud de la fuente de corriente, la cual es conocida, Z es el módulo y θ es la fase de la biompedancia. A la salida del amplificador de instrumentación la tensión puede ser representada como v(t)=V*sin(ω0t+θ), y de acuerdo con las relaciones trigonométricas, también como V(t)=V*cos(θ)*sin(ω0t) + V*sin(θ)*cos(ω0t). La señal V(t) es posteriormente dividida en dos líneas, y multiplicada en una de las líneas con una señal en fase con la señal de referencia original, representada como U*sin(ω 0t), y una señal en cuadratura con la señal de referencia original, que se representa como U*cos(ω0t). Las señales de cada una de las líneas es demodulada a través de un filtro paso de baja, de modo que las señales de continua obtenidas a la salida de los demoduladores son proporcionales a las funciones cos(θ) y sin(θ) respectivamente. De esta forma, las señales demoduladas en fase y en cuadratura son proporcionales a las componentes resistiva y reactiva de la impedancia, respectivamente, ya que la parte real de la impedancia es proporcional a Vcos(θ)/I y la parte imaginaria de la impedancia es proporcional a Vsin(θ)/I. Es necesario utilizar un filtrado paso de baja para obtener las señales de continua, las cuales son luego muestreadas por conversores analógicos/digitales para su posterior procesamiento. La impedancia medida se corresponde así con la impedancia del tejido o la sección del cuerpo en cuestión. Además, debido a que los electrodos de tensión están separados de los electrodos de corriente, la densidad de corriente en los puntos donde se mide la tensión es más uniforme que en la zona de inyección de corriente, de modo que las medidas son mucho más precisas. 6.3.1. ETAPA 3.1: ETAPA DE AMPLIFICACION La señal de tensión detectada en el tejido puede ser de amplitud muy baja (dependiendo de la impedancia medida), por lo que puede ser necesaria su amplificación. De este modo el ruido en los circuitos no afectará tanto a la medida y el procesado de la medida será de mayor calidad. Por otro lado, en una configuración de cuatro electrodos, la impedancia de entrada del preamplificador que mide la diferencia de tensión entre los electrodos es normalmente mucho mayor que la impedancia de los electrodos. De esta forma, la impedancia de los electrodos puede ser despreciada en el análisis de bioimpedancia, ya que la caída de tensión en los electrodos es mucho menor que la observada a la entrada del amplificador. Esto lo conseguiremos con el amplificador de instrumentación INA332. El amplificador utilizado para este sistema de detección es el INA332 del fabricante Burr-Brown Corporation de Texas Instruments, este amplificador tiene una alta impedancia de entrada (como 10 13//3pF en el INA332). Como la impedancia de entrada es muy alta, en los electrodos de tensión no pasa prácticamente corriente, así la medida de la impedancia del tejido es descontaminada por la impedancia de contacto. La gran ventaja de este dispositivo es que dispone de una ganancia adaptable desde el exterior. Esta ganancia se puede programar con dos resistencias, una conectada del pin RG al pin Out, y la otra de RG a REF. Figura 45: Esquema del INA332 (Imagen del datasheet del fabricante) La ganancia del componente es programable con ayuda de las resistencias R2 y R1 del esquema anterior. La relación que tiene la ganancia con las resistencias es la siguiente: G=5+5( R 2 / R1) Para no saturar los componentes, se ha considerado una amplificación de 10 para el amplificador de instrumentación. En este caso, se han establecido los valores recomendados por el fabricante R1=R2=100 kΩ. Se realizaron además una serie de simulaciones para comprobar su operación en las frecuencias más altas y más bajas a las cuales el dispositivo va a trabajar. Se ha establecido un valor de tensión de referencia en la impedancia de 50mV. Este valor se ha considerado adecuado ya que es lo suficientemente elevado como para generar señales medibles y está dentro de los márgenes de seguridad para los dispositivos de bioimpedancia. El esquema simulado es el que se muestra a continuación. Figura 46: Esquema de simulación del amplificador de instrumentación (INA332) A continuación se muestran las simulaciones de las distintas impedancias (Z a,Zb,Zc) a distintas frecuencias (5 kHz, 100 kHz, 500 kHz y 1 MHz.) 5khz Figura 47: Señal de salida (linea roja) y señal de entrada diferencial (linea azul) de las distintas impedancias (Z a,Zb,Zc) a 5kHz 10Khz Figura 48: Señal de salida (linea roja) y señal de entrada diferencial (linea azul) de las distintas impedancias (Z a,Zb,Zc) a 10kHz 100khz Figura 49: Señal de salida (linea roja) y señal de entrada diferencial (linea azul) de las distintas impedancias (Z a,Zb,Zc) a 100kHz 1Mhz Figura 50: Señal de salida (linea roja) y señal de entrada diferencial (linea azul) de las distintas impedancias (Z a,Zb,Zc) a 1MHz. La tensión de salida a 1Mhz debería tomar un valor 500mV, sin embargo toma un valor máximo de 461,827mV, este valor tiene un error del 7,63%, un error demasiado grande según las especificaciones de diseño. En la hoja de característica del componente, el fabricante muestra una gráfica que explica el comportamiento de la ganancia del dispositivo en función de la frecuencia. Esto proporciona una idea de cómo la ganancia va disminuyendo a medida que aumenta la frecuencia (Figura 51). Figura 51: Representa la ganancia frente a la frecuencia (Imagen de datasheet del fabricante) Como se puede apreciar en dicha gráfica (figura 51), cuanto más pequeña es la ganancia, ésta mantendrá su valor más cercano al ideal a frecuencias más altas. Por este motivo se ha decidido simular el dispositivo con una ganancia de cinco, la ganancia mínima a la que puede funcionar el dispositivo. 6.3.1.1. Amplificador de instrumentación con ganancia cinco. Como se ha comentado en el apartado anterior, con frecuencias cercanas al Mhz la ganancia disminuye (figura 51), la frecuencia a la que la ganancia comienza a disminuir es mayor cuanto menor sea la ganancia configurada en el componente. El componente con G=10 no da un valor preciso a frecuencias cercanas al Mhz. Por ello se ha simulado el componente con la mínima ganancia permitida en su función de trasferencia (G=5). A continuación se muestran las gráficas de las simulaciones de las distintas impedancias (Za,Zb,Zc) en distintas frecuencias (5khz,10khz, 100khz, 1Mhz). 5khz Figura 52: Señal de salida (linea azul) y señal de entrada diferencial (linea roja) de las distintas impedancias (Z a,Zb,Zc) a 5kHz. 10khz Figura 53: Señal de salida (linea azul) y señal de entrada diferencial (linea roja) de las distintas impedancias (Z a,Zb,Zc) a 10kHz. 100khz Figura 54: Señal de salida (linea azul) y señal de entrada diferencial (linea roja) de las distintas impedancias (Z a,Zb,Zc) a 100kHz. 1Mhz Figura 55: Señal de salida (linea azul) y señal de entrada diferencial (linea roja) de las distintas impedancias (Z a,Zb,Zc) a 1MHz. Se ha representado las tres impedancias en una gráfica, mostrando un barrido AC en frecuencia de la entrada y la salida del instrumento amplificador (figura 56), de esta forma se podrá comprobar cómo el dispositivo se aleja de su comportamiento ideal a medida que aumenta la frecuencia. Figura 56: Barrido en frecuencia de la señal de salida (linea azul) y señal de entrada diferencial (linea roja) de las distintas impedancias (Za,Zb,Zc), G=5. El comportamiento a la salida no se ve con suficiente resolución en la figura 55, por ello se ha simulado las tres impedancias pero representado únicamente la tensión a la salida del instrumento. Figura 57: Barrido en frecuencia de la señal de salida (linea roja) de las distintas impedancias (Z a,Zb,Zc). El componente reduce su ganancia a medida que aumenta la frecuencia, es necesario encontrar entonces la frecuencia máxima a la cual el componente puede trabajar con una ganancia que introduzca un error máximo del 1%. Debido a este problema se realiza la simulación en varias frecuencias y se concluye que la frecuencia máxima a la que dispositivo puede operar adecuadamente es 450khz. A esta frecuencia el dispositivo permite una ganancia de cinco con un error del 0,98%. A frecuencias superiores de 450khz el comportamiento del dispositivo se deteriora reduciendo su ganancia e imposibilitando así la toma de medidas con suficiente precisión. A 1Mhz el valor máximo que ofrece el dispositivo es 239mV, cuando debería acercarse lo máximo a 250mV ya que alimentamos el componente con 50mV. Con estas medidas el error es del 4.4% aproximadamente, un error demasiado alto que distorsionaría la medida impidiendo que éstas sean de calidad, aunque este error es menor que el que se produce a la misma frecuencia con una ganancia de diez. A una frecuencia de excitación de 800khz, el valor que ofrece el dispositivo en su salida es de 243,09 mV teniendo la medida un error próximo al 2.5 %. El objetivo es que el error en la ganancia sea inferior al 1%. Por tanto el valor máximo ofrecido por el componente debe de ser superior a 247,5mV. Con la simulación a 500khz el valor máximo que ofrece la señal de salida es 247, 047mV. Aún se debería reducir más la frecuencia para tener medidas precisas (con un error inferior al 1%). Con una frecuencia un poco inferior, 450 khz, el valor máximo de salida es 247,550mV, este error es de 0,98% que está dentro de los límites requeridos por la aplicación. Por lo que este componente no se considera óptimo para realizar medidas de bioimpedancia a frecuencias de trabajo superiores a 450khz. 6.3.2. ETAPA 3.2: GENERACION DE SEÑAL EN FASE Y EN CUADRATURA Para poder medir el módulo y la fase de la bioimpedancia es necesario separar la señal medida en dos componentes, una componente para la señal en fase y otra para la señal en cuadratura. Esto se realiza multiplicando por un lado la señal detectada y amplificada en la etapa anterior por una señal en fase con la señal de referencia de la fuente de corriente. Por el otro lado, la señal detectada y amplificada es multiplicada por una señal en cuadratura con la señal de salida de la fuente de corriente. Se plantea entonces el problema de obtener señales tanto en fase como en cuadratura para la realización de la demodulación coherente planteada en el diseño. Con circuitos RC-CR se pueden obtener estas señales como demostraremos a lo largo de este punto. Considerando un primer circuito R1-C1 y un segundo circuito C2-R2. Con este esquema, se consigue un desfase de 90º en la tensión observada en la resistencia R2 y la capacidad C1. Si modificamos la frecuencia de excitación de la fuente, las señales de tensión en R2 y C1 seguirán teniendo un desfase de 90º pero a medida que va cambiando la frecuencia la amplitud de la señal difiere una con respecto a la otra. Figura 58: Esquema del circuito RC-CR. Usando una excitación de 5khz, obtenemos las siguientes señales en las salidas Figura 59: Salida del circuito RC-CR a 5khz, tensión de salida en C1(linea roja) y tensión de salida en R2 (linea verde) Si nos fijamos en las dos señales efectivamente están desfasadas 90º (¼ de periodo) pero no tienen la misma amplitud, a continuación se muestran dos simulaciones adicionales, una primera a 8khz (figura 60) y otra a 15khz (figura 61). 8khz Figura 60: Salida del circuito RC-CR a 8khz, tensión de salida en C1(linea roja) y tensión de salida en R2 (linea verde) En la simulación vemos como ya las amplitudes son más parecidas pero no tienen el mismo módulo. 15khz Figura 61: Salida del circuito RC-CR a 15khz, tensión de salida en C1(linea roja) y tensión de salida en R2 (linea verde) El desfase es de 90 grados para todas las frecuencias. Sin embargo, el valor de la amplitud no es el mismo en todas las frecuencias. A pesar de ello, existe una frecuencia para la cual, en función del valor de los componentes, las señales de tensión en R2 y C1 sí toman el mismo valor. Esta sería la frecuencia deseada de operación, la cual se corresponde con la frecuencia para la cual la resistencia y la capacidad tienen la misma impedancia en módulo. Dicha frecuencia puede ser deducida a partir de la siguiente expresión: R= 1 1 1 = = jwC wC 2 π f C Despejando la frecuencia de la ecuación de anterior se obtiene el siguiente valor: f interes= 1 2 πRC Por lo que si introducimos en la ecuación los valores de R=12k y de C=1,27n que son los valores con los que se ha simulado el circuito anterior (figura 58) la frecuencia de interés será: f interes=10 443 Hz≈10kHz La frecuencia a la que coincide en módulo la impedancia de la resistencia y del condensador puede observarse gráficamente en la figura 62. Figura 62: Módulo de las salidas en los componentes C1 y R2. Se puede apreciar como efectivamente ambas señales se cortan en un punto próximo a los 10khz, lo cual significa que en esa frecuencia las dos señales tendrían la misma amplitud. En la siguiente simulación se muestra la evolución temporal del circuito con una frecuencia de 10khz. Figura 63: Salida del circuito RC-CR a 10khz, tensión de salida en C1(linea roja) y tensión de salida en R2 (linea verde) A esta frecuencia las dos ondas tienen la misma amplitud, entonces surge un problema de la necesidad del uso de múltiples frecuencias si se quiere obtener una medida precisa y de calidad. La solución a este problema viene dada por el uso de un potenciómetro digital como es el caso del ADN2850 de Analog Devices. Con este dispositivo modificaremos el valor de la resistencia para recorrer todas las frecuencias. A continuación se muestran las claves para realizar la programación del potenciómetro y así configurar el generador de señales en fase y cuadratura para su empleo en cada una de las frecuencias de interés. 6.3.2.1. Esquema de Programación del Potenciómetro Digital ADN2850. La resistencia nominal entre el terminal W y el terminal B del potenciómetro, RWB, tiene un valor de 25kΩ, aunque también es posible el valor de 250kΩ. A partir de este valor nominal, el potenciómetro digital es capaz de moverse por 1024 posiciones (resolución de 10bits). Los dígitos finales en la nomenclatura del componente determinan el valor nominal, pero en la aplicación actual utilizaremos el valor de 25 kΩ. Para el cálculo de la resistencia RWB hay que tener en cuenta que el valor más pequeño posible se corresponde con el dato 0x000, RWB(0), y éste tiene un valor de 30Ω causado por la resistencia de la escobilla, el cual es independiente a la resistencia nominal. El segundo valor más pequeño, RWB(1) es 24.4Ω+30Ω=54.4Ω para el dato 0x001. El tercer valor de la resistencia es 24.4*2Ω+30Ω=78.8Ω, el cuarto, 24.4*3Ω+30Ω=103.2Ω y así sucesivamente. En la posición 0 donde el valor de la resistencia es 30Ω el límite de corriente entre los terminales W y B no debe de ser más de 20mA. La siguiente ecuación determina por lo tanto el valor de la resistencia: RWB ( D)= D ∗RWB..NOM +RW 1024 Donde: D es el equivalente decimal del dato contenido en el registro interno del potenciómetro: RDAC. RWB..NOM es el valor de la resistencia nominal (25kΩ). RW es la resistencia de la escobilla (30Ω). Por ejemplo, usando el valor D=3 obtendríamos una resistencia de 100 Ohm. RWB (3)= 3 ∗25k Ω+30 Ω=103 Ω≈100 Ω 1024 Dicho valor se corresponde con la siguiente frecuencia de operación para el dispositivo. f interes= 1 =1,2 Mhz 2 π∗100 Ω∗1,27 nF Por lo tanto usando D=3 en una frecuencia próxima al Mhz las señales tendrán la misma amplitud y el desfase deseado de 90º. 6.3.2.2. Circuito RC para generar señal en fase y cuadratura. A continuación se mostrarán los resultados obtenidos mediante simulación del esquema planteado para la generación de señales en fase y cuadratura. Figura 64: Esquema del circuito generador de las señales en fase y cuadratura. En el estudio por simulación se han considerado las siguientes frecuencias: 5 kHz, 10 kHz, 100 kHz y 1 MHz. Como vimos en el apartado anterior, cada una de estas frecuencias está asociada con un valor del potenciómetro para obtener dos señales desfasadas 90º con la misma amplitud. La siguiente tabla resume estos valores: FRECUENCIA(Hz) D 5078,64 1010 10105,02 507 102245,40 49 1214449,44 3 RESISTENCIA Ω 24688,20 12407,93 1226,29 103,24 A continuación se presentan los resultados obtenidos mediante simulación para cada una de las frecuencias de interés. También se ha representado la fase de cada una de ellas. D=1010 f=5k Figura 65: a) Tensión de salida en R1(linea verde)(R1C1) y R2(linea roja)(R2C2), b) margen de fase de las salidas, (D=1010, fc=5khz) Como se mencionó anteriormente, la frecuencia de interés es aquella en la que la señal en fase y la señal en cuadratura tienen el mismo módulo. Observando la figura 65, esta frecuencia se corresponde con el punto de corte de los módulos de las tensiones. Este punto coincide como ya se ha comentado con la frecuencia en la que la resistencia y la capacidad tienen la misma impedancia en módulo. Para todas las frecuencias, el desfase entre ambas señales es de 90º, incluida la frecuencia de interés. D=507 f=10k Figura 66: a) Tensión de salida en R1(linea verde)(R1C1) y R2(linea roja)(R2C2), b) margen de fase de las salidas, (D=507, fc=10khz) D=49 f=100k Figura 67: a) Tensión de salida en R1(linea verde)(R1C1) y R2(linea roja)(R2C2), b) margen de fase de las salidas, (D=49, fc=100khz) D=3 f=1Mh Figura 68: a) Tensión de salida en R1(linea verde)(R1C1) y R2(linea roja)(R2C2), b) margen de fase de las salidas, (D=3, fc=1Mhz) A medida que se aumenta el valor del parámetro D la frecuencia de interés va decreciendo. En la frecuencia de interés las señales tienen un valor equivalente a la mitad de la señal original la fase se mantiene en todas las frecuencias con una diferencia de 90º, incluida la frecuencia de interés. 6.3.3. ETAPA 3.3: ETAPA MULTIPLICACION DE SEÑALES Como ya hemos comentado en otras partes de la memoria, para poder obtener el módulo y la fase de la impedancia es necesario multiplicar la señal detectada a la salida de la etapa de amplificación por una señal en fase y una señal en cuadratura. Este proceso se llevará a cabo a través de dos multiplicadores analógicos de señales. Para el diseño de esta etapa se ha probado distintos diseños encontrados en la literatura, los cuales se describen más detalladamente a continuación. 6.3.3.1. Multiplicador analógico – Diseño A Partiendo de una señal A y una señal B, el objeto del multiplicador será la multiplicación de ambas señales. En electrónica, dicho proceso no resulta inmediato. En este primer diseño nos basaremos en una de las propiedades de los logaritmos: el logaritmo de un producto es la suma de los logaritmos de los factores: lnA+lnB=ln ( A∗B) Entonces si al resultado anterior le aplicamos la inversa del logaritmo, obtendremos el producto A por B. antilog (ln( A∗B))= A∗B Necesitamos entonces componer un circuito que sea capaz de realizar el logaritmo de la señal, después debe sumar dos señales y por ultimo un circuito que realice función antilogarítmica. De este modo tendremos las dos señales A y B multiplicadas. En un primer lugar se muestra un circuito que realiza el logaritmo de la señal de entrada de modo que si llamamos A a la entrada, la salida será ln(A). Este circuito tiene una salida no lineal y es proporcional al logaritmo neperiano de la señal de entrada. Se basa en la relación exponencial que existe entre la corriente y la tensión en una unión PN. Figura 69: Circuito logarítmico [43] El esquema anterior permite obtener el logaritmo de la señal. Para realizar la suma de los logaritmos (lnA+lnB) se utiliza el esquema mostrado en la figura 70, correspondiente a un sumador inversor de dos canales. Figura 70: Circuito sumador inversor [43] Si intercambiamos en el primer circuito el diodo por la resistencia y viceversa, el circuito finalmente realizará la función antilogaritmática. Figura 71: Circuito antilogarítmico [43] La unión de los tres circuitos anteriores conforma el diseño del multiplicador. La figura 72 muestra este esquema y las partes que lo componen. Figura 72: Circuito multiplicador analógico de señales A continuación se muestra el esquema del circuito completo y posteriormente una simulación de éste. Figura 73: Esquema de simulación del multiplicador analógico (Diseño A). Para comprobar si el circuito realizaba la función para la cual fue diseñado, se simuló su respuesta ante dos señales de la misma frecuencia, comparando la señal resultante con la obtenida con un multiplicador ideal que ofrece la librería del programa de simulación. Figura 74: Multiplicación ideal (linea verde) y salida del multiplicador analógico (Diseño A) (linea azul). Tras diversas simulaciones probando diversos parámetros y componentes, no fue posible obtener una señal correspondiente a la multiplicación de las señales. Se decidió descartar el diseño y probar otra alternativa. 6.3.3.2. Multiplicador analógico – Diseño B El siguiente esquema está basado en el diseño propuesto en [44] y [45]. En [44] se describe un circuito de control de potencia para el sistema de gestión de la energía de la batería utilizando operacionales. El esquema propuesto consiste en un circuito de detección de corriente con salida de tensión y un multiplicador analógico. Esta última parte de su diseño es el esquema que queremos analizar. Los autores consiguen buenos resultados con la multiplicación analógica, por este motivo se decide probar esta solución. El esquema propuesto es el que se muestra a continuación: Figura 75: Esquema de simulación del multiplicador analógico (Diseño B). En este circuito las señales de entrada A y B se trasfieren al multiplicador analógico. Los operacionales U1 y U3, en concreto los usados en la simulación son AD648A, están bien emparejados entre sí, al igual que IB1=IB3=IB y Is1=Is3=Is. Donde IB denota la corriente en reposo. De los análisis demostrados en [45], la tensión de salida de este circuito viene dada por: V o= −R f Ra 2 c 2R R q I S ∗v a v b+2 ( Ra R f − )v 2R c R p b En la ecuación anterior si elegimos valores adecuados para las resistencias de modo que Rf/Rp=Ra/ (2Rc), entonces la tensión de salida puede reescribirse como: V o= −R f Ra 2 2R c R q I S v a v b=−k v a v b Donde k es la ganancia de la multiplicación. Las resistencias son asignadas para cumplir la igualdad Rf/Rp=Ra/(2Rc), y posteriormente para cumplir que la ganancia sea igual a 1, esto se consigue únicamente con la modificación de Rq: Rc=R11=R15=5k Ra=R7=R12=50k Rp=R14=R8=500k Rm=R1=R2=R6=100k R3=Rm/2 Rq=R13=R9=100k Rf=R16=R10=100k La figura 76 muestras los resultados de simulación obtenidos con los valores de resistencias impuestos. Figura 76: Multiplicación ideal (señal azul) y salida del multiplicador analógico (Diseño B)(señal roja). Los resultados obtenidos no cumplieron con las expectativas iniciales por lo que se decidió buscar otra alternativa. 6.3.3.3.- Multiplicador analógico – Diseño C El circuito que se muestra a continuación realiza la multiplicación de señales usando amplificadores operacionales. Está formado por tres operacionales de uso común A1, A2 y A3 y una serie de resistencias. Figura 77: Esquema de simulación del multiplicador analógico (Diseño C). Los operacionales utilizados en este diseño son HA-5154. Los operacionales A1 y A2 y las resistencias R31=R32=R3 están conectadas como un convertidor tensión a corriente. Las resistencias R11, R21, R12 y R22 se usan para detectar la corriente de la fuente y sus valores cumplen con las siguientes restricciones: R11=R12=R1, R21=R22=R2, R1=R2. La tensión de salida V01 y V02 son las tensiones de salida en los operacionales A1 y A3, y A2 y A3, respectivamente. Estas tensiones pueden ser expresadas del siguiente modo: 2RR f RR f v x +v y 2 2 V 01= (i 31) = ( ) =K 1 ( v x +v y ) 2 8R S I S 4R S I S R X 2RR f RR f v x −v y 2 2 V 02= ( i 32) = ( ) =K 1( v x −v y )2 8R S I S 4R S I S R X Donde Vx y Vy son las tensiones de las señales de entrada (señales a multiplicar). Las tensiones V 01 y V02 son trasferidas al amplificador diferencial formado por el operacional A3 y las resistencias Rs11=Rs21=Rs22=Rs y Rf1=Rf2=Rf. Como resultado de esto la tensión de salida se corresponde al siguiente valor: V o =V 01−V 02 Y sustituyendo en las dos ecuaciones anteriores resultaría la siguiente expresión: V 0 =K 2 v x v y K 2= RR f 2 I S RS R X Por lo tanto V0 es la multiplicación de las señales analógicas multiplicadas por un factor de ganancia K2. La relación de resistencia se ha elegido teniendo en cuenta que la ganancia K 2 debe ser lo más cercana posible a 1. Se realizaron diversas simulaciones del circuito a diversas frecuencias. La figura 78 muestra un ejemplo de los resultados obtenidos. Figura 78: Multiplicación ideal (señal marrón) y salida del multiplicador analógico(Diseño C)(linea azul). Como se puede observar en la gráfica obtenida por el programa de simulación, la señal de salida no es capaz de alcanzar a la señal ideal, no realizando correctamente la multiplicación deseada. Se descarta también este circuito por no alcanzar los objetivos previstos. 6.3.3.4. Multiplicador analógico – Diseño D Teniendo en cuenta que los circuitos simulados basados en amplificadores operacionales no mostraron los resultados esperados, se decidió analizar el comportamiento de circuitos basados en amplificadores de transconductancia. Los amplificadores de transconductancia difieren principalmente de los operacionales en el tipo de salida que presentan: en vez de corresponderse con una fuente tensión de baja impedancia, se corresponde con una fuente de corriente de alta impedancia controlada por la tensión diferencial entre sus terminales de entrada. Un amplificador de transconductancia se representa normalmente por el siguiente símbolo: Figura 79: Símbolo del amplificador operacional de transconductancia. La ganancia de estos amplificadores puede programarse con la corriente de entrada en el terminal correspondiente (IABC). Teniendo en cuenta esta característica, se va a realizar un análisis de las posibilidades de este dispositivo como elemento para la realización de una multiplicación analógica. A continuación se describirá el comportamiento del dispositivo LM13700, un amplificador de transconductancia de uso común y altas prestaciones que será empleado en el análisis de la etapa de multiplicación realizada en este apartado. 6.3.3.4.1. Teoría de funcionamiento del dispositivo LM13700. La figura 80 muestra el esquema interno del amplificador de transconductancia LM13700. En la etapa de entrada se encuentran los transistores T1 y T2. Al aplicar una tensión diferencial vd, se produce una diferencia en las corrientes de colector de los transistores que es proporcional aproximadamente a: I c2− I c1= g m v d Figura 80: Circuito interno del amplificador de transconductancia LM13700 Los transistores T9, T10, y T11 forman un espejo de corriente, que reproducen en el colector de T11 la corriente Ic1. Esta corriente a su vez vuelve a ser pasada por otro espejo de corriente formado por T15, T16 y T17, sobre el colector de T16. Por otra parte, la corriente I c2 es reproducida sobre el colector de T14 por un tercer espejo con los transistores T12, T13 y T14. Por tanto la corriente de salida se puede expresar como: I o=I c14− I c16 I o=I c2− I c1= g m v d Además de lo comentado anteriormente el dispositivo contiene dos transistores más (T 18 y T19) que forman un seguidor Darlington necesario en las aplicaciones en las cuales se requiere seguir la tensión a la salida sin cargar a ésta. La polarización del circuito se realiza con otro espejo de corriente (T5, T6 y T7). Este espejo usa la corriente IABC y la copia en los emisores de T1 y T2, repartiendo la corriente de inyección en partes iguales entre los dos emisores. La corriente de reposo de T9 a T17 es la mitad de I ABC por lo que los transistores tienen puntos de trabajo idénticos. El parámetro más fundamental que se controla con IABC es la transconductancia g m= I ABC 2VT gm sólo depende de la corriente de control y de la temperatura. La ganancia de tensión del amplificador queda determinada por la resistencia de carga y puede reducirse hasta el valor que se requiera. Estas dos características permiten el uso del dispositivo en lazo abierto. La corriente de polarización IB también depende directamente de IABC. La ecuación que los relaciona se muestra a continuación, a través de la ganancia de los transistores de entrada: I B= I ABC 2β También la corriente de offset varía directamente con IABC, ya que es aproximadamente proporcional a la corriente de polarización y al desapareamiento entre las β de los transistores de entrada. Las resistencias de entrada y salida resultan proporcionales a β e inversamente proporcionales a IABC. La máxima corriente de salida es aproximadamente IABC, ya que ésta se tiene cuando uno de los transistores de entrada se corta. Entonces el otro conduce toda la corriente IABC, que se traslada a la salida. El ruido equivalente del amplificador también depende de IABC, ya que los mecanismos básicos de producción de ruido en los semiconductores son dependientes de las corrientes de polarización de las uniones. 6.3.3.4.2. Análisis del funcionamiento del amplificador El amplificador de transconductancia se descompone así en una etapa formada por dos fuentes de Wilson (espejos de corriente de precisión) y una etapa diferencial. En el modelo que se muestra a continuación (ver figura 81 se han considerado las resistencias de entrada y salida de las fuentes de Wilson (espejos de corriente de precisión), pero con ganancia ideal. En la rama de I3 despreciaremos la influencia de 2*rπ'/β' por ser varios órdenes de magnitud inferior a roβ. 2 V cc I 3= +I 1 r oβ Asimismo, para V0 = 0. I 4= 2 V cc + I2 r oβ I 5= 2V cc +I 3 ro ' β Figura 81. Modelo del amplificador completo en el que se han sustituido las fuentes de Wilson por fuentes de corriente ideales en paralelo con sendas resistencias. La corriente de salida es: 1 1 1 1 + )=I 2−I 1−V cc ( + )=. r o β ro ' β ' r o β ro ' β ' I Δ Is 1 1 .= ABC (v d +V T −V cc V T ( + )) 2VT Is β V A β' V A ' I o=I 2−I 3+V cc ( Donde aparece un término constante de tensión de offset: V os.i =V cc V T ( 1 1 + ) β V A β' V A ' La transconductancia es la misma que para el diferencial, debido a que la ganancia de las fuentes de Wilson es casi igual a 1. La resistencia de entrada es la resistencia de entrada del diferencial. Ri=2 r π La resistencia de salida es el paralelo de las resistencias de salida de las dos últimas fuentes de Wilson (una NPN y la otra PNP). 6.3.3.4.3. Modelo en frecuencia del amplificador de transconductancia El modelo surge del análisis en frecuencia de las distintas etapas que componen el amplificador: las fuentes de Wilson y la etapa diferencial. La etapa diferencial de entrada no influye en lo relativo a la transadmitancia global gm , ya que es prácticamente constante en un rango de frecuencias muy amplio. Sí influye en su impedancia de entrada, que afecta cuando se emplean generadores de señal no ideales. Las corrientes de colector del diferencial son tomadas por fuentes de corriente de Wilson, que por ser PNP tienen una respuesta en frecuencia pobre. La corriente del sector inversor atraviesa otra de las fuentes Wilson, pero esta vez es NPN, y por lo tanto no influye dado que la respuesta en frecuencia de los transistores NPN integrados es dos órdenes de magnitud superior a la de los PNP. El modelo en frecuencia se muestra en la figura 82. Figura 82: Esquema del modelo en frecuencia del amplificador de transconductancia Los parámetros del amplificador se muestran a continuación: Ri≃2 r π≃ C i≃ G m= 4β NPN V T I ABC C π NPN +C μ NPN 2 I ABC 2 τ T s+1 2 2 2 V t 2 τ T s +2 τ T s+1 RO ≃r oPNP β PNP = 2β PNP V A.PNP I ABC C o≃2(C μ PNP +C μ NPN )+C cs Ro es el paralelo de las resistencias de salida de las dos fuentes Wilson, pero la fuente NPN tiene una resistencia mucho mayor que la PNP. No sucede lo mismo con Co, donde aparecen las dos capacidades de salida. También aparece la capacidad colector-sustrato del transistor NPN, que puede ser de hasta 3 pF. 6.3.3.4.4. Adaptador de impedancia (buffer) En la mayoría de las aplicaciones del amplificador de transconductancia es necesario aplicar una carga importante a la tensión en la salida, pero sin alterar la salida. En el LM13700 se han incorporado dos transistores en conexión Darlington, T18 y T19, para cumplir esta función. El transistor T8 es una extensión de la fuente de Wilson que polariza a T1 y T2, la función de este transistor es polarizar al primer transistor del Darlington con una corriente proporcional a IABC. Esto permite reducir la corriente con la que la base de T18 carga la salida del amplificador para una IABC baja y, para mantener una polarización convenientemente elevada cuando IABC es alta. Un inconveniente de este tipo de adaptación de impedancia reside en la caída de tensión de más de 1V respecto a la tensión de salida de la etapa de transconductancia, aunque por tratarse de una caída aproximadamente constante no tiene efectos importantes en señales de corriente alterna. 6.3.3.4.5. Multiplicador analógico de cuatro cuadrantes. Para el desarrollo del amplificador analógico de cuatro cuadrantes se usa el amplificador operacional de transconductancia dual con diodos alineados y buffer resultante del modelo LM13700 proporcionado por Texas instruments. A continuación se muestra un esquema del componente. Figura 83: Esquema del dispositivo LM13700 (dual). (Imagen datasheet del componente) En nuestro caso sólo es necesario usar uno de los dos amplificadores operacionales de transconductancia de los que dispone el dispositivo. En el mismo datasheet del componente se muestra el esquema de un multiplicador analógico de cuatro cuadrantes. Figura 84: Multiplicador analógico de señal de cuatro cuadrantes (Diseño D)(Imagen datasheet del componente). Dicho esquema fue empleado en las múltiples simulaciones que se realizaron para analizar el funcionamiento del componente. Figura 85: Esquema de simulación del multiplicador de señal de cuatro cuadrantes (Diseño D). La gráfica mostrada en la figura 86 muestra un ejemplo de los resultados obtenidos con el esquema propuesto a la frecuencia de 5kHz, así como la tensión esperada resultante de una multiplicación ideal. La figura 87 muestra esta vez los resultados a una frecuencia de 500khz. Figura 86: Multiplicación ideal(linea azul) y salida del multiplicador analógico de cuatro cuadrantes(Diseño D)(linea roja), 5khz. Figura 87: Multiplicación ideal(linea azul) y salida del multiplicador analógico de cuatro cuadrantes(Diseño D)(linea roja), 500kHz. Los resultados obtenidos no cumplieron con las expectativas iniciales. Como se puede observar en la gráfica, la señal de salida no se corresponde con la magnitud deseada y además existe un desfase entre la onda de referencia y la onda de salida. 6.3.3.5. Multiplicador analógico – Diseño E: Integrado MPY634. A la vista de los resultados obtenidos, se procedió posteriormente a analizar la viabilidad de un multiplicador analógico comercial. El dispositivo MPY634 es un multiplicador analógico integrado de cuatro cuadrantes. Las entradas diferenciales (X, Y y Z) permiten la configuración como multiplicador y como divisor, pero además permiten el cálculo del cuadrado de la señal y su raíz cuadrada manteniendo una gran exactitud. Al tener un gran ancho de banda permite el procesamiento de señales RF, IF. La salida interna del amplificador del MPY634 reduce la complejidad del diseño comparado con otros multiplicadores de altas frecuencias. La exactitud de la tensión interna de referencia proporciona un preciso ajuste del factor de escala. La entrada diferencial Z permite seleccionar un factor de escala desde 0.1 a 10 usando un lazo externo de resistencias. A continuación se muestra un esquema del dispositivo. Figura 88: Esquema del dispositivo MPY634 (Imagen de datasheet del fabricante). La relación que adquiere la tensión de salida del componente es la siguiente: V out =A[ ( X 1− X 2 )(Y 1 −Y 2 ) −( Z 1−Z 2 )] SF Donde A es la ganancia de salida del amplificador (típicamente 85dB en DC), SF es el factor de escala. El valor de SF viene preajustado de fábrica a 10V pero es ajustable en un rango de 3V a 10V usando una configuración de resistencias externas. X,Y,Z son las tensiones de entrada. La tensión de entrada a escala completa es igual a la seleccionada en el SF. La máxima tensión de entrada es ±1.25 SF. Una comprensión intuitiva de la función de transferencia se puede obtener por analogía a la del amplificador operacional. Al asumir que la ganancia en bucle abierto, A, de la salida del amplificador operacional es infinita, la revisión de la función de transferencia revela que cualquier Vout se puede crear con una cantidad infinitesimal dentro del miembro entre corchetes. El circuito puede ser analizado asignando tensiones para todas las entradas X, Y, Z. Por ejemplo si se hace la entrada Z1=Vout y Z2=0. La expresión entre corchetes se reduce a: ( X 1− X 2 )(Y 1 −Y 2 ) −(V out −0)=0 SF Esta aproximación conduce a una simple relación que puede ser resuelta para Vout. El factor de escala se ajusta a 10V desde fábrica con una precisión de 0,1% o inferior. Aunque también puede ser ajustado conectando resistencias o potenciómetros entre el pin SF y el -Vs de la fuente de alimentación. El valor de la resistencia externa de ajuste puede ser aproximado por la siguiente expresión: RSF =5,4 k Ω[ SF ] 10−SF Muchas aplicaciones pueden beneficiarse de la posibilidad de la reducción del factor de escala. El MPY634 está plenamente caracterizado a VS = ± 15V pero puede operar hasta con ±8V con una consiguiente reducción de la capacidad de entrada y rango de salida. Al igual que con cualquier circuito de gran ancho de banda, las fuentes de alimentación deben ser reforzadas con condensadores cerámicos de alta frecuencia. Estos condensadores deben estar ubicados lo más cerca posible a las conexiones de alimentación de la MPY634. 6.3.3.5.1. Configuración básica del multiplicador integrado. La siguiente figura muestra la conexión básica como multiplicador. La precisión está completamente definida sin la necesidad de ninguna circuitería adicional. Algunas aplicaciones pueden beneficiarse del ajuste de una o más entradas. Las entradas completamente diferenciales facilitan las entradas de referencia. Figura 89: Esquema de conexionado como multiplicador del MPY634 (Imagen de datasheet) Se puede compensar la tensión de offset con una relación de resistencias como la que se muestra en la figura 89. Además, se utiliza la simplificación anteriormente comentada en la que se une el pin de salida Vout a Z1 y el Z2=0, obteniéndose una tensión de salida equivalente a: ( X 1 −X 2 )(Y 1−Y 2 ) +Z 2 10V Si hacemos Z2=X2=Y2=0, la tensión de salida que se obtiene es: V out = V out = X 1∗Y 1 10V 6.3.4. ETAPA 3.4: ETAPA DE FILTRADO. La etapa de filtrado, como ya se ha comentado, es necesaria para obtener el nivel de continua de las señales resultantes de las multiplicaciones. Ambos niveles de continua contienen información suficiente para el cálculo del módulo y la fase de la impedancia. Para realizar esta operación se utilizará un filtro pasa-baja que permita aislar las señales de continua, las cuales son posteriormente muestreadas por conversores analógicos/digitales para su posterior procesamiento. Las señales de cada una de las líneas es demodulada a través de un filtro pasa-baja, de modo que las señales de continua obtenidas a la salida de los demoduladores son proporcionales a las funciones cos(θ) y sin(θ) respectivamente. También son proporcionales al módulo de la impedancia, de modo que un sencillo procesado permitiría resolver tanto el módulo como la fase de la impedancia, teniendo en cuenta que el resto de factores que intervienen son conocidos. El filtro pasa-baja ideal es un circuito formado por una resistencia y un condensador, que permite el paso de las frecuencias por debajo de la frecuencia de corte (Fc) y elimina las que sean superiores a ésta. Figura 90: Filtro pasa baja y su respuesta en frecuencia. La reactancia capacitiva cambia con la frecuencia. Para altas frecuencias X C es baja logrando con esto que las señales de estas frecuencias sean atenuadas. En cambio a bajas frecuencias (por debajo de la frecuencia de corte) la reactancia capacitiva es grande, lo que causa que en estas frecuencias los parámetros no se vean afectados o son afectados muy poco por el filtro. Con la ley de Ohm: V i =I∗Z= I∗√( R +X C ) 2 2 V o =I ∗X C V o= Vi √1+(2 π R C )2 Donde Z es la impedancia. La frecuencia de corte es aquella donde la amplitud de la señal entrante cae hasta un 70.7 % de su valor máximo. Y esto ocurre cuando X C = R (reactancia capacitiva = resistencia). Si XC = R, la frecuencia de corte será: Fc= 1 2 π RC La banda de frecuencias por debajo de la frecuencia de corte se llama Banda de Paso, y la banda de frecuencias por encima de Fc se llama Banda de Atenuación. En nuestro diseño, se ha ajustado la frecuencia de corte a 1 kHz, ya que la frecuencia de corte más baja a la que va a trabajar el dispositivo son 5 kHz. A continuación se muestra un esquema con el diseño del filtro y los valores adecuados de resistencia y condensador. Esta frecuencia de corte es suficientemente baja para atenuar en las frecuencias en las que trabaja el dispositivo. Figura 91: Esquema para la simulación del filtro A continuación se muestra el Diagrama de Bode. El margen de ganancia del filtro muestra una frecuencia de corte de 1kHz, atenuando más de 14dB cualquier señal por encima de 5 kHz. Figura 92: Respuesta del filtro con una frecuencia de corte impuesta de 1khz. 6.3.5. ETAPA 3.5: ETAPA DE CONVERSION (A/D) Esta etapa es fundamental para que los datos analógicos obtenidos puedan ser interpretados y procesados por un software con el objeto de obtener el módulo y la fase de la impedancia. Se hace necesaria así una transformación de las señales analógicas en datos digitales. Con tal objetivo, se emplearán un convertidor A/D integrado, el ADS7230 de Texas Instruments. El ADS7230 es un dispositivo electrónico capaz de convertir una entrada analógica de tensión en un valor binario equivalente al valor que toma la señal analógica. La señal analógica, que varía de forma continua en el tiempo, se conecta a la entrada del conversor A/D y se somete a un muestreo con una frecuencia fija. A la salida se obtiene el equivalente digital de la señal. Este conversor posee dos señales de entrada llamadas Vref+ y Vref- que determinan el rango en el cual se convertirá la señal de entrada. El dispositivo establece una relación entre su entrada (señal analógica) y su salida (digital) dependiendo de su resolución. Esta resolución se puede establecer a partir del valor máximo de la tensión de entrada y la cantidad máxima de dígitos binarios en la señal de salida. El componente elegido tiene una resolución de 12 bits y su resolución responde a la siguiente expresión: Resolución= valor analogico maximo 12 2 Este conversor permite la conversión de dos señales a la vez, conectadas a los pines +IN1 y +IN0. Dichas señales se establecen respecto de una referencia de tensión, conectada al pin COM. A continuación se muestran la vista superior y los pines del componente (ver Figura 93) al igual que su conexionado básico para que el dispositivo opere correctamente (ver Figura 94) según las recomendaciones del fabricante del dispositivo (la imagen se corresponde con el ADS7279, pero sería equivalente en el ADS7230, teniendo en cuenta los pines +IN1, +IN0 y COM). Figura 93: Vista superior del componente ADS7230 (Imagen del datasheet del fabricante) Figura 94: Conexionado del componente DAS7229 (Imagen datasheet del fabricante). 6.4. Simulación del Modelo de Cole-Cole modificado. Gráficas y código Matlab. Finalmente, con el objeto de comprender mejor el comportamiento en frecuencia de la impedancia de un medio biológico, se ha realizado una simulación del modelo de Cole. El modelo utilizado es una ampliación que incluye en la expresión un retardo de tiempo invariante (Td). Este retardo es causado por la velocidad a la que se transfiere la corriente eléctrica a través de un conductor (hay que tener en cuenta que el dispositivo de bioimpedancia utiliza normalmente cables para llegar hasta el segmento corporal a medir). El error introducido por este Td fijo fue modelado como un error en θ que aumenta linealmente con la frecuencia [46], este error fue matemáticamente modelado multiplicando la expresión por un factor (e− jwT ) . Por lo tanto la ecuación general del modelo es: d Z obs =( RE RE − jwT )[ R I + ) α ]( e RE +R I 1+( jwC m (R E +R I )) d Donde Zobs es el complejo observado de Z; RE, RI y Cm son los componentes de los valores de este circuito; ω es la frecuencia f en radianes (=2π·f); y j es √ −1 . Se ha realizado una simulación Matlab del modelo para dos casos reales de pacientes en hemodiálisis (ver ANEXO). Los valores de los parámetros (R E, RI, CM, Td y α) fueron proporcionados por un dispositivo comercial de bioimpedancia (Body Composition Monitor de Fresenius). Con esta simulación se ha pretendido ilustrar el comportamiento en frecuencia de los valores de impedancia en dos casos reales. En la figura 95 se muestran los valores de impedancia obtenidos para el caso de un paciente con los siguientes parámetros RE=671,3Ω; RI =2227,3Ω; Cm=0,69nF; Td=-3,06ns; α=0,39 Figura 95: Diagrama de Cole modificado para los valores RE=671,3Ω; RI =2227,3Ω; Cm=0,69nF; Td=-3,06ns; α=0,39 En la figura 96 se muestran los valores de impedancia obtenidos para el caso de un paciente con los estos parámetros RE=715,5Ω; RI =1455Ω; Cm=2,01nF; Td=-4,24ns; α=0,38 Figura 96: Diagrama de Cole modificado para los valores RE=715,5Ω; RI =1455Ω; Cm=2,01nF; Td=-4,24ns; α=0,38