Práctica 2: PLL

Anuncio

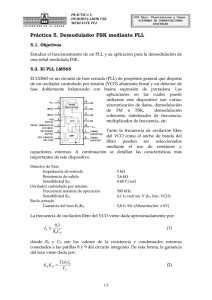

Práctica 2: PLL 2.1 Introducción En esta práctica se utilizará el circuito NE565. Es un bucle de enganche en fase monolítico con márgenes de funcionamiento que llegan hasta los 500 Khz. para el NE565. El PLL responde a un diagrama de bloques simplificado como el de la Figura 1. 2.2 Circuito NE 565 El circuito NE565 un PLL de propósito general. Su diagrama de bloques y patillado se muestra en la siguiente figura. Figura 2. Diagrama de bloques del PLL NE565 - Entrada El circuito de entrada tiene un limitador conectado al pin 6. - VCO. 0.3 , donde R0 es una resistencia R0C0 externa entre los terminales 8 y +Vcc (pin 10) y C0 es un condensador externo situado entre la patilla 9 y tierra. La frecuencia libre del VCO es f 0 ! − Comparador de fase El parámetro que caracteriza el comportamiento del detector de fase es su sensibilidad KD (V/rad). Es un parámetro interno, por lo que no se puede modificar. En las hojas de características del NE565 aparece como valor típico KD = 0.68 (V/rad). 1 - Filtro del lazo La ganancia en lazo cerrado viene determinada por la expresión K0 × KD (s-1), donde K0 ((rad/s)/V) es la sensibilidad del VCO. Para el circuito NE565 se puede hacer la aproximación: K 0 K D ! 33.6 f 0 -1 (s ) , siendo VC la tensión de alimentación VC total que se suministra al circuito. La salida del detector de fase se obtiene en la patilla 7. Entre la patilla 7 y la 10, el NE565 tiene una resistencia interna R1 = 3.6 kΩ que puede utilizarse para construir el filtro del lazo. En la mayoría de las aplicaciones basta con aplicar un único condensador a la patilla 7; de esta forma, el paralelo con la resistencia R1 produce un filtro de orden 1, tal y como se muestra en la Figura 3. Figura 3. Filtro del lazo En este caso, la función de transferencia del filtro de lazo es L( s ) = 1 1 = 1 + sR1C1 1 + s!1 La función de transferencia del lazo, en el caso de tener un comportamiento ideal en el detector de fase, vendría especificada por la expresión "( s) L( s ) = !( s ) L( s ) + s Obsérvese que cuando L(s) es una función de primer orden, la respuesta global del lazo es de segundo orden: $( s) K = 2 #( s ) s + 2"!n s + !2n donde ζ es el factor de amortiguamiento y ωn es la frecuencia natural del sistema. Por ello, la función de trasferencia del filtro cerrado es "2n K 0 K D / !1 %( s) , = 2 = 2 2 $( s ) s + 2#"n s + "n s + s / !1 + K 0 K D / !1 2 siendo su respuesta en frecuencia la mostrada en la Figura 4. Figura 4. Función de transferencia en lazo cerrado - Margen de enganche. El margen de enganche es el margen de frecuencias de entrada fi a las que el PLL puede engancharse. Este límite, suponiendo que el VCO no se satura, está determinado por la característica del detector de fase. Supongamos que la diferencia entre la frecuencia de salida del VCO fo y la de entrada fi es Δf. Para que el PLL se enganche a la frecuencia de entrada, hay que modificar el voltaje de control del VCO en V0 = !f voltios. Si el amplificador del lazo no tiene ganancia, el voltaje de K0 control del VCO es directamente el voltaje de salida del detector de fase (V0=VD). Como el detector de fase entrega un voltaje VD = K D ! e , y como la desviación máxima de fase que puede seguir el PLL es #e " ! / 2 , resulta que el margen de enganche es #f H = "K 0 K D ! 16 f 0 . VC 2.3 Desarrollo de la práctica • Los PLL se pueden utilizar para realizar demodulación coherente de señales moduladas en amplitud. El esquema de demodulación coherente se muestra en la Figura 5. LM565 Limitador Detector de fase A V fRF fFI VCO LM1496 Figura 5. Demodulador coherente 3 Como se observa, se puede utilizar el demodulador balanceado MC1496 junto con el integrado NE565 para llevar a cabo dicha operación. • Module una portadora de 10 Khz. con un tono de 1 Khz. Diseñe y analice el demodulador coherente de AM, siguiendo el esquema mostrado en la Figura 6. Elija adecuadamente los componentes R0 y C0 para que la frecuencia de oscilación libre sea 10kHz con la fuente de alimentación de 15V. Puede sustituir el transistor 2N3565 por el 2N2222. Los valores de los condensadores aparecen en µF. Correspondencia entre el patillaje del integrado LM1596 y el del LM1496 LM1596 1 2 3 4 5 6 7 8 9 10 LM1496 1 2 3 4 5 6 8 10 12 14 4 R 0 C0 Figura 6. Demodulador coherente 2.3.1 Caracterización del PLL Nota: Para evitar la carga del mezclador con el PLL desconecte el Condensador de 0.1uF que une el emisor del transistor Q1 con el pin 7 del mezclador LM1496/LM1596. 2.3.1.1 Medición de la frecuencia de oscilación libre del PLL. Con la entrada conectada a tierra mida la frecuencia de oscilación libre del PLL en el emisor del transistor Q1. 2.3.1.2 Medición del margen de enganche y seguimiento a con distintos voltajes de fuente. Mida los márgenes de enganche y seguimiento del PLL introduciendo una señal sinusoidal en la entrada del circuito y observando la salida en el emisor del transistor Q1 variando la fuente de alimentación entre 10 voltios y 24 voltios de 2 en 2 voltios. Realice una gráfica en el informe con esta tabla de valores. 5 2.3.2 Caracterización del Mezclador 2.3.2.1 Rechazo de OL en FI. Con la entrada general del circuito conectada a 0 voltios, introduzca una señal de 1 Vrms y 10 Khz. al mezclador a través del condensador de 0.1µF desconectado en la etapa anterior. Observe la salida para verificar el nivel de potencia de la señal a 10 Khz. en el pin 12 del LM1496. Calcule el nivel de rechazo en FI del OL. 2.3.2.2 Rechazo de OL en RF Utilizando el mismo montaje del apartado anterior, mida el nivel de señal de 10Khz. en el pin 4 del LM1496. Calcule el nivel de rechazo en RF de OL. 2.3.2.3 Rechazo de RF en FI Conectando el condensador de 0.1µF de nuevo a tierra, introduzca una señal de 10 Khz. por la entrada general del circuito y verifique el nivel de señal de 10 Khz. existente en el pin 12 del LM1496. Calcule el nivel de rechazo de RF en FI. ¿Cómo se podrían mejorar los niveles de rechazo de las distintas señales a la salida? Verifique la topología del montaje y los posibles puntos por los cuales se intercomunican las entradas entre si y la salida. Sugiera posibles soluciones de montaje y/o calidad de componentes. 2.3.3 Medidas a Realizar con el Demodulador Nota: Conecte el condensador entre el emisor del transistor Q1 y el pin 7 del mezclador LM1496. El valor de la fuente de alimentación será de 15V. 2.3.3.1 Verificación de la demodulación y distorsión de la señal obtenida. Una vez conectado completamente el circuito genere una señal modulada en AM con frecuencia portadora 10Khz. y moduladora de 1.3 Khz. Verifique que a la salida del PLL hay una señal triangular de 10Khz., y a la salida del circuito total se obtiene la señal demodulada. Tome como señal de referencia la moduladora de 1 Khz. para todas las siguientes medidas. (Mida con el osciloscopio la FFT de esta señal antes de introducirla al segundo generador para realizar la modulación, y anote su valor en dB) Sobre la señal demodulada: − Mida su nivel de potencia en comparación a la señal de referencia. − Mida el nivel de potencia de los armónicos 2 y 3 de la señal demodulada (2 y 3 Khz.) y los armónicos de la señal a 20 y 30 Khz. − ¿Es posible mejorar la señal final reduciendo la distorsión de estos armónicos? Analice la señal con la que se está realizando la demodulación coherente. ¿Cómo la podría mejorar? 6