Final de Febrero 06

Anuncio

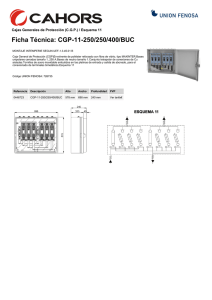

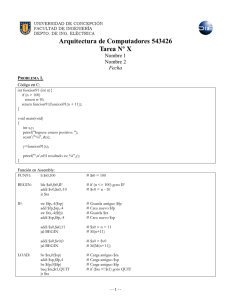

ESTRUCTURA Y TECNOLOGÍA DE COMPUTADORES EXAMEN DE TEORÍA (Problemas) (2-Febrero-2006) Apellidos: Grupo: Sistemas I Sistemas II Nombre: Gestión I Gestión II 2. (3 puntos) Dada la subrutina MIPS siguiente: subrutina: DNI: Superior I Superior II buc: 1. (2 puntos) Dado el siguiente circuito: Reloj A sig: T Q Q’ S1 D Q C Q’ S2 fin: move move li andi bne addi srl addi beq j jr $v0,$0 $s0,$a0 $t0,32 $t1,$s0,1 $t1,$0,sig $v0,$v0,1 $s0,$s0,1 $t0,$t0,-1 $t0,$0,fin buc $ra S4 B a) J Q K Q’ a) (0.5 puntos) Describir en castellano, de forma muy breve y concisa (una sola frase bastaría) qué utilidad tiene esta rutina (es decir, qué valor devuelve en función del parámetro $a0). b) Suponer que se llama a la rutina con $a0=0xfffedb77: i. (1.0 puntos) Sabiendo que la rutina tarda 4 µs en ejecutarse en un procesador monociclo, calcular la frecuencia del mismo. ii. (1.0 puntos) Si suponemos que los retardos de la memoria y la ALU son el doble que el retardo del banco de registros, utilizando el resultado anterior calcular el tiempo de ejecución de la misma rutina en una versión multiciclo del procesador. c) (0.5 puntos) La rutina NO respeta el convenio de salvado de registros en la pila. Especificar las instrucciones que habría que añadir y el lugar en el que habrían de colocarse para respetar escrupulosamente dicho convenio. S3 (1.0 puntos) Completar el cronograma adjunto, suponiendo retardos despreciables en todos los elementos del diagrama: R e lo j A B S1 Notas: S2 • S3 • S4 b) (1.0 puntos) Suponiendo un retardo de 10 ns para los flip-flops de tipo T y JK, de 7 ns para el cerrojo de tipo D, de 4 ns para las puertas lógicas AND y OR, y de 2 ns para el inversor NOT, calcular el retardo total del circuito para obtener la señal de salida S4, justificando el cálculo realizado. Para el apartado b), tener en cuenta las traducciones a instrucciones reales de las posibles pseudoinstrucciones. Suponer que todas las instrucciones aritmético-lógicas inmediatas y de desplazamiento tardan 4 ciclos, y que el jr tarda 3. Para el resto de instrucciones considerar la duración en ciclos vista en clase en la implementación multiciclo. 3. (2 puntos) Supóngase un procesador con un CPI ideal igual a 4 ciclos y una frecuencia de reloj de 2 GHz. El sistema dispone de una memoria caché, así como de una memoria principal con un tiempo de acceso de 100 ns. Si la tasa de fallos de la caché es del 15%: a) (0.5 puntos) ¿Cuál sería el CPIreal de esta máquina? b) (0.75 puntos) ¿Cuánto más rápida será la máquina al añadir una segunda cache que tiene un tiempo de acceso de 10 ns y una tasa de fallos del 30%?. Se supone que una petición a memoria principal se realiza solamente cuando se detecta un fallo en la caché de segundo nivel. c) (0.75 puntos) ¿Cuánto más rápida será la máquina si, en lugar de añadir una segunda caché, duplicamos la frecuencia de reloj del procesador manteniendo el tiempo de acceso a memoria principal en 100 ns? SOLUCIÓN: 1. a) Cronograma: R e lo j A B S1 S2 S3 S4 b) El retardo más largo desde las entradas A y B hasta la salida S4 lo introduce el camino que pasa por el flip-flop tipo T (10 ns), el negador pegado a la puerta AND (2 ns), la puerta AND (4ns) y la puerta OR (4 ns), para sumar un total de 20 ns. Se puede comprobar que no existe otro camino con mayor retardo. 2. a) Se trata de una rutina que cuenta el número de bits que hay a cero en la constante de 32 bits que se le pasa como parámetro en $a0, y devuelve el valor de dicho conteo en $v0. b) Análisis del tiempo de ejecución (observar que las tres pseudoinstrucciones que aparecen, dos move y un li, se traducen por sendas add y addi, respectivamente): Instrucción MIPS move $v0,$0 move $s0,$a0 li $t0,32 buc: andi $t1,$s0,1 bne $t1,$0,sig addi $v0,$v0,1 sig: srl $s0,$s0,1 addi $t0,$t0,-1 beq $t0,$0,fin j buc fin: jr $ra # Ejecuciones 1 1 1 32 32 5 32 32 32 31 1 Total: 200 instrs. # Ciclos/Inst. 4 (add) 4 (add) 4 (addi) 4 3 4 4 4 3 3 3 Subtotal 4 4 4 128 96 20 128 128 96 93 3 Total: 704 ciclos Monociclo: El programa ejecuta exactamente 200 instrucciones, es decir, 200 ciclos en un procesador monociclo. Si tarda en ejecutarse 4 microsegundos, es decir, 4000 nanosegundos, el tiempo de ciclo será de 4000/200 = 20 ns. La frecuencia, por tanto, será de 1/(20·10-9) = 50.000.000 Hz = 50 MHz. Multiciclo: El tiempo de ciclo en la implementación monociclo debe ser el de la instrucción más larga, esto es, un lw. Dicho tiempo es TMEM + TBR + TALU + TMEM + TBR = 2TBR + TBR + 2TBR + 2TBR + TBR = 8TBR. De lo que se deduce que 8TBR = 20 ns, esto es, TBR = 2.5 ns. El tiempo de ciclo en multiciclo, sin embargo, es el del paso más largo, en nuestro caso el introducido por la ALU o la memoria, es decir, 2TBR = 5 ns. Puesto que el programa ejecuta 704 ciclos en su versión multiciclo, tardará 704·5 = 3520 ns = 3’52 µs. c) La rutina machaca uno de los registros seguros, $s0. Por tanto, deberá guardarlo previamente en la pila, para recuperarlo justo antes de volver. Es decir, habrá que añadir las instrucciones: subrutina: addi sw move move li buc: andi bne addi sig: srl addi beq j fin: lw addi jr $sp,$sp,-4 $s0,0($sp) $v0,$0 $s0,$a0 $t0,32 $t1,$s0,1 $t1,$0,sig $v0,$v0,1 $s0,$s0,1 $t0,$t0,-1 $t0,$0,fin buc $s0,0($sp) $sp,$sp,4 $ra 3. Si la frecuencia de reloj es de 2 Ghz, entonces un ciclo dura 1/2·109 = 0.5·10-9 segundos = 0.5 ns a) El tiempo de acceso a la memoria principal son 100 ns, que equivalen a 200 ciclos. El CPI real es: CPIreal = CPIideal + TF*PF ya que las referencias a datos no producen fallos. Luego tenemos que: CPIreal = 4 + 0,15*200 = 34 ciclos b) La segunda cache tiene un tiempo de acceso de 10 ns = 20 ciclos. Al añadir esta segunda cache, tenemos CPIreal = 4 + 0,15*(0,7*20 + 0,3*(200 + 20)) = 16 ciclos ya que el 15% de las veces tenemos un fallo en la cache de primer nivel y, dentro de ese 15%, el 70% de las veces tenemos un acierto en la cache de segundo nivel (lo que supone un tiempo de acceso de 20 ciclos) y el 30% restante un fallo (lo que supone un tiempo de acceso de 220 ciclos por el tratamiento del fallo en la cache de segundo nivel y el acceso a la memoria principal). Por tanto, la nueva máquina es 34/16 = 2.13 veces más rápida. c) En este caso, un ciclo dura 1/4000·106 = 0.25·10-9 segundos, es decir, 0.25 nanosegundos. El tiempo de acceso a memoria principal equivale a 100ns = 400 ciclos. El CPI real de la nueva máquina es: CPIreal=CPIideal + TF*PF = 4 + 0,15*400 = 64 ciclos. Sin embargo, puesto que hemos doblado la frecuencia del reloj, hemos divido por 2 la duración del ciclo, lo que afectará al tiempo de ejecución de los programas. Sabiendo que el tiempo real que, en promedio, se tarda en ejecutar una instrucción es: TCPU de 1 instrucción = CPIreal * Tiempo de Ciclo tenemos que la nueva máquina será: TCPU-A/TCPU-C = (34 * 0.5) / (64 * 0.25) = 17 ns / 16 ns = 1.06 veces más rápida.