CODISEÑO HW/SW

Anuncio

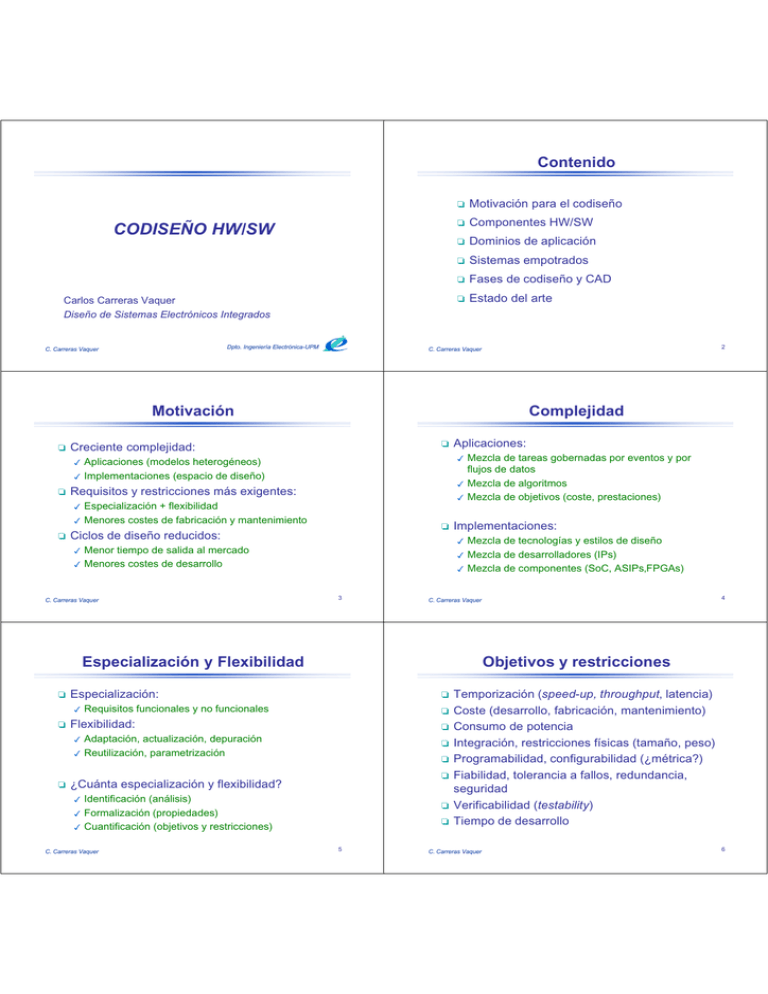

Contenido CODISEÑO HW/SW Carlos Carreras Vaquer Diseño de Sistemas Electrónicos Integrados Dpto. Ingeniería Electrónica-UPM C. Carreras Vaquer R Motivación para el codiseño R Componentes HW/SW R Dominios de aplicación R Sistemas empotrados R Fases de codiseño y CAD R Estado del arte 2 C. Carreras Vaquer Motivación R Complejidad R Creciente complejidad: Mezcla de tareas gobernadas por eventos y por flujos de datos Mezcla de algoritmos Mezcla de objetivos (coste, prestaciones) Aplicaciones (modelos heterogéneos) Implementaciones (espacio de diseño) R Requisitos y restricciones más exigentes: Especialización Menores R + flexibilidad costes de fabricación y mantenimiento R Ciclos de diseño reducidos: Implementaciones: Mezcla de tecnologías y estilos de diseño de desarrolladores (IPs) Mezcla de componentes (SoC, ASIPs,FPGAs) Menor tiempo de salida al mercado Menores costes de desarrollo Mezcla 3 C. Carreras Vaquer Aplicaciones: Especialización y Flexibilidad R R Objetivos y restricciones Especialización: Requisitos R funcionales y no funcionales R Flexibilidad: R Adaptación, actualización, depuración Reutilización, parametrización R R R R ¿Cuánta especialización y flexibilidad? Identificación (análisis) (propiedades) Cuantificación (objetivos y restricciones) R Formalización C. Carreras Vaquer 4 C. Carreras Vaquer R 5 Temporización (speed-up, throughput, latencia) Coste (desarrollo, fabricación, mantenimiento) Consumo de potencia Integración, restricciones físicas (tamaño, peso) Programabilidad, configurabilidad (¿métrica?) Fiabilidad, tolerancia a fallos, redundancia, seguridad Verificabilidad (testability) Tiempo de desarrollo C. Carreras Vaquer 6 Ciclos de diseño reducidos R R R R R What is a System Anyway? Nuevas metodologías y herramientas que soporten la complejidad (CAD) Mecanismos de especificación (funcionalidad y restricciones) Exploración del espacio de diseño (algoritmos y estimadores) Verificación (accesibilidad, heterogeneidad) Reutilización de los diseños (IPs) como clave para mayor productividad EE249 5 7 C. Carreras Vaquer Sistemas Heterogéneos System (for us) R Sistemas heterogéneos: especificación n n y restricciones (aplicación) y arquitecturas (implementación) metodologías de diseño niveles de programabilidad niveles integración componentes Environment to environment Sensors + Information Processing + Actuators u Computer is a system u Micro-processor is not R Sistemas HW/SW: HW: SW: EE249 velocidad y alto coste flexibilidad y bajo coste 6 8 C. Carreras Vaquer Programabilidad e integración R Componentes HW y SW R Niveles de programabilidad: ASIC: Aplicación: funcionalidad seleccionable Instrucción: instrucciones en memoria Microinstrucción: microprograma en memoria Hardware: interconexionado configurable R Sistemas C. Carreras Vaquer No configurable Configurable FPGA: R Arquitecturas de componentes SW (programables): Monoprocesadores: secuenciales (cores) – ASIP: Arquitectura e instrucciones específicas – DSP: Arquitectura específica, instrucciones generales – ISP: Arquitectura e instrucciones generales (RISC, CISC) Niveles de integración: Sistemas Arquitecturas de componentes HW: en una placa en un chip Multiprocesadores: paralelos – SIMD: Instrucción única y datos múltiples (en array) – MIMD: Instrucciones y datos múltiples (concentrados, distribuídos) 9 C. Carreras Vaquer 10 ASIPs R R R R R R Comparación de componentes ASIP: Application Specific Instruction Processor Adapta a la aplicación el set de instrucciones y los recursos (registros, buses, conexiones) Mejores prestaciones que ISP en aplicaciones concretas Facilita comunicaciones HW/SW al usarse como core Requiere un compilador específico Disponibles como megacells (reuso) ISP Prestaciones Potencia Reutilización Diseño HW Diseño SW Processor cores in embedded systems + ASIC +++ + +++ (Fuente: Zebo Peng) 11 C. Carreras Vaquer + +++ +++ ASIP ++ ++ ++ ++ ++ 12 C. Carreras Vaquer Terminology 3 4 DSP Gen. purp. Fixed Parameterisable Applicationspecific Have CISC, RISC or VLIW features. Adapted for signal processing : ASIP Parallel MAC 1 maccycle Ecient memory & register structure Ecient data addressing modes : FIR. . . Traditional vendors : - TI : TMS320C5x - Moto : M56xxx Fabless vendors : Semiconductor dpts : - DSP Group : Pine, Oak - TCSI : Lode - ARM - Philips : Epics - SGS-Th : ST18950 ASIP System dpts : Adapted for specic application : - Philips - Alcatel-Bell - Ericsson - TI - ... GSM, DECT, MPEG, automotive control. . . Mostly xed-point. Instruction set : ,! Retargetable compilation tools ! c 1996 Gert Goossens Selection of standard instructions Specialised instructions : Viterbi stage, WDF adaptor, FFT buttery. . . Telecom & multimedia : low power ! DAC Tutorial June 7, 1996 c 1996 Gert Goossens Codiseño Heterogéneo (HW/SW) R R Problemas de codiseño “Diseño concurrente por parte del mismo equipo de diseñadores de los componentes HW y SW de un sistema digital usando metodologías y herramientas que consideren la interacción HW/SW” R Tipos de problemas de codiseño Sistemas empotrados (parte de un sistema mayor) en un chip (bloques) Síntesis de ASIPs y procesadores Máquinas aceleradoras (basadas en FPGAs) Sistemas Elementos de codiseño: Especificación = comportamiento + restricciones = especificación + arquitectura Síntesis = partición + comunicaciones Validación = síntesis + especificación Partición C. Carreras Vaquer DAC Tutorial June 7, 1996 R Cada problema pone el énfasis en ciertas tareas de diseño R Impacto crítico: Características Tiempo 13 C. Carreras Vaquer coste-prestaciones de salida al mercado 14 Sistemas empotrados (embedded) R R Embedded Systems Gobernados por datos (DSP), por control (reactivos, tiempo real) y mixtos Dominios de aplicación: Automoción, electrónica de consumo, comunicaciones, aviación, domótica, robótica, defensa, industria, ... R R Programabilidad a nivel de instrucción y microinstrucción Énfasis en: Cumplimiento Tiempo de restricciones (coste-prestaciones) de desarrollo (iteraciones del ciclo de diseño) Embedded systems = systems reading, processing and controlling physical quantities 15 C. Carreras Vaquer Modern Vehicles, an Electronic System Importance of Embedded Software and Embedded Processors “... the New York Times has estimated that the average American comes into contact with about 60 microprocessors every day....” [R. Camposano, Design Automation of Embedded Systems] Most of the functionality of embedded systems will be implemented in software! Latest top-level BMWs contain over 100 microprocessors [Personal communication] Smart Dust Components Home Networking: Application (Subnet) Clusters Voice Phone Video Phone Still Camera PDA Telecom Based Internet Access Printer Laptop Intercom PC-2 PC/Data Based DVD Player Video Game Entertainment Based PC-1 Security Based Audio Alarms Door Sensors Window Sensors Motion Detectors Passive CCR comm. MEMS/polysilicon Active beam steering laser comm. MEMS/optical quality polysilicon Web-TV STB VCR TV Stereo Analog I/O, DSP, Control COTS CMOS Power capacitor Multi-layer ceramic Sensor MEMS/bulk, surface, ... Light Control Smoke Detectors Video surveillance Cam Corder Laser diode III-V process Clocks Climate Control Solar cell CMOS or III-V Appliance Based Ovens Thick film battery Sol/gel V2O5 Utility Customization Toasters Sprinklers 1-2 mm Micromechanical Flying Insects Communication versus Computation • Computation cost (2004): 60 pJ/ operation (assuming continued scaling) • Communication cost (minimum): – 100 m distance: 20 nJ/ bit @ 1.5 GHz – 10 m distance: 2 pJ/ bit @ 1.5 GHz • Computation versus Communications – 100 m distance: 300 operations == 1bit – 10 m distance: 0.03 operation == 1bit blowfly Calliphora Computation/ Communication requirements vary with distance, data type, and environment http://robotics.eecs.berkeley.edu/~ronf/mfi.bfml Vision Sistemas basados en componentes Contact Joe Network, any ucers -to-any trannscl R Handy 21 Joe`s Office urgent R Alternativa de implementación para sistemas empotrados (SoC) Énfasis en: Especificación (comportamiento, temporización, comunicaciones) Selección arquitectural (determina prestaciones) Reutilización (tiempos de desarrollo) forward Get John Mike Maria John R Joe in Boston Mike Maria Problemática: Selección de componentes (exploración) y verificación Síntesis de interfases Validación Oxygen, LCS, MIT, http://www.lcs.mit.edu 16 C. Carreras Vaquer Productivity 2000+ Challenge Deep Submicron Paradigm Shift Logic Trans./Chip 15M 100M 15x - Productivity GAP 10M System Architecture • Hardware • Software 1.0M Logic Design Verification Physical Design Silicon Processing Trans./ Staff- Month (Average of Top 10% of Codes) 2M Transistors 100 MHz Wire RC 1 ns/ cm 40M Transistors 600 MHz Wire RC 6 ns/ cm Virtual Component Based Design - Minimize Design Time - Maximize IP Reuse - Optimize System Level 90% New Design Cell Based Design - Minimize Area - Maximize Performance - Optimize Gate Level Will the design team deliver on time and within budget? 1991 1996 2001 90% Reused Design Deep Sub- Micron: Impact on Semicon Industry “Virtual” “Real” Component Virtual Components and System Design “Real” “Virtual” Component Component Component Deep Sub- Micron Component based design System on Board System on Board System on Silicon • Today, several IC companies have a chance of selling their devices on a board. • With the possibility of integrating an entire system on a single chip, there will be room only for one manufacturer!!! • However, nobody can possibly know all these areas in depth. System on Silicon • Select the best components from several different internal and external vendors • Integrate the system using standard interfaces • Validate the design functionality, performance and reliability. Sistemas de procesamiento Test Challenge: System-On-Chip R • SoC manufactured and tested in single stage • Core I/Os often more than Chip I/Os • Test generation difficult due to limited core design knowledge • Direct access to core ports unavailable • Core & UDL test part of System-On-Chip test R Soporte arquitectural para sistemas operativos del set de instrucciones y la arquitectura Diseño software en multiprocesadores System-on-Board (SOB) System-on-Chip (SOC) Process Process Selección IC Design ASIC Design Core Design UDL Design IC Manuf. ASIC Manuf. IC Test ASIC Test R SOC Integration SOB Test Énfasis en: Prestaciones SOB Design SOB Manuf. Soporte de programabilidad a nivel de aplicación Diseño de ISPs y ASIPs: SOC Manuf. (exploración del espacio de diseño) correcta (verificación por simulación) Funcionalidad SOC Test R Problemática: Compiladores Arquitecturas optimizados para cada set específicas: pipeline, caches, ... 17 C. Carreras Vaquer Sistemas de emulación y prototipado R R R R CAD en codiseño Acelerar la simulación de un HDL Programabilidad a nivel de instrucción y a nivel hardware (configurables) Arquitectura destino: ISP (SW) y FPGAs (HW) Énfasis en: R R R Análisis: dependencias, sincronismo, paralelismo Caracterización de tiempos HW y SW R Problemática: R Compiladores optimizados con coordinación HW-SW Limitaciones de las FPGAs (nº de puertas, pinout) C. Carreras Vaquer 18 Necesidad: complejidad, restricciones, tiempo de desarrollo Tareas: modelado, exploración, particionado, síntesis, validación Ámbito actual: bajo nivel de abstracción (niveles físico, RTL, ensamblador) con tendencia al alto nivel (más fiable en SW) Ámbito futuro: alto nivel de abstracción (nivel algorítmico), diseño de arquitecturas, verificación C. Carreras Vaquer 19 CAD Methodology Traditional System Level Design Flow • • • • • • • • • Capture – Simulate (60’s – 80’s) • Describe – Synthesize (80’s – 00’s) • Specify-Explore-Refine (00’s – 20’s) Interface Definition ( Bus Standards ) Component Selection SW and ASIC development Selection of “Glue Logic” PCB Layout SW integration Debug Prototypes Manufacturing and Test of Board Copyright 1999 Daniel D. Gajski Behavioral Synthesis Traditional ASIC Design Flow • • • • • • Design entry at RTL Synthesis Netlist Simulation with respect to behavioral Model Place and route Simulation with timing Definition: Behavioral synthesis (high-level, algorithm and architectural synthesis) means going from an algorithm specification to a RT level which implements that behavior. Implications: • More reliable analysis of design decisions • Will compete with machine code in future. • Manufacturing & test of chip Fases de codiseño HW/SW (1) R Fases de codiseño HW/SW (2) Especificación: R Modelado, lenguaje, formato intermedio, transformaciones Modelos (simulables): aspectos funcionales, de temporización y de comunicaciones R Síntesis HW, generación de código SW, interfases de comunicaciones Importancia de la planificación: – Interacción HW-SW – Serialización de procesos SW Particionado: R Diseño arquitectural, selección de componentes, estimación SW: reducción de coste, interacción intensa con el sistema operativo HW: partes cuya temporización sea crítica, interacción intensa con el entorno C. Carreras Vaquer Síntesis: Integración: Validación por simulación, emulación, prototipado Verificación, validación y estimación aparecen en todas las fases en mayor o menor medida 20 C. Carreras Vaquer 21 Pasos en cada fase Flujo de codiseño Especificació ón de nivel superior Transformaciones Formato Intermedio Nueva especificación NO de nivel inferior Partició ón HW-SW Evaluación restricciones Sííntesis Hardware Generació ón de có ódigo Integració ón a nivel inferior SI Comprobación equivalencia NO a nivel superior C. Carreras Vaquer Verificació ón Cosimulació ón 22 Prototipado C. Carreras Vaquer Control vs Flujo de datos R Entornos de codiseño Control: R Foco: controladores reactivos Modelo: basado en control (p.e. FSM) Optimización: control Entornos: POLIS (‘94), CHINOOK (‘95) R R R R R Flujo de datos: R Foco: procesamiento de datos Modelo: basado en datos (p.e. DFG) Optimización: flujo de datos Entornos: VULCAN (‘95), COSYMA (‘93) C. Carreras Vaquer 23 R R 24 CADLAB: http://www.ida.liu.se/~cadlab/codesign.html CHINOOK: http://www.cs.washington.edu/research/project/lis/chinook/ COMET: http://www.ececs.uc.edu/~ddel/projects/comet/comet.html COOL: http://ls12-www.informatik.uni-dormunt.de/~niemann/ COSYMA: http://www.ida.ing.tu-bs.de/projects/cosyma/home.e.html POLIS: http://www-cad.eecs.berkeley.edu/Respep/Research/hsc/abstract.html PROCOS : http://archive.comlab.ox.ac.uk/procos/codesign.html SIR /CASTLE: http://borneo.gmd.de/EDS/SYDIS/castle/index.html C. Carreras Vaquer 25