Ejercicios Resueltos y Propuestos: ADC,DAC, DDR y SNR.

Anuncio

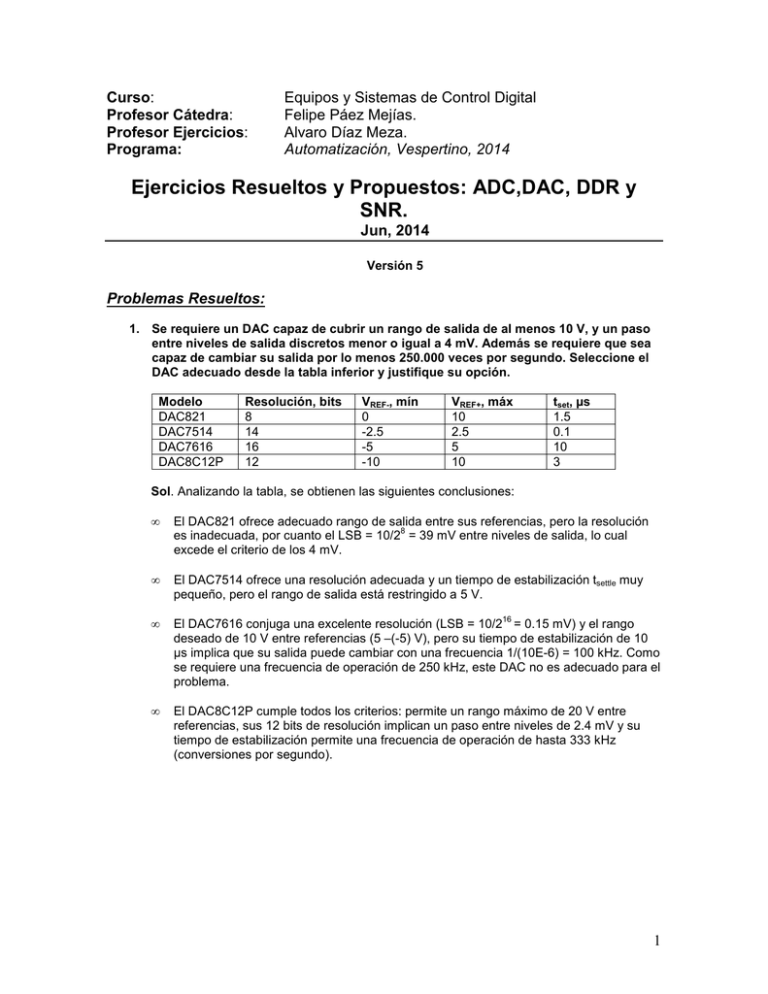

Curso: Profesor Cátedra: Profesor Ejercicios: Programa: Equipos y Sistemas de Control Digital Felipe Páez Mejías. Alvaro Díaz Meza. Automatización, Vespertino, 2014 Ejercicios Resueltos y Propuestos: ADC,DAC, DDR y SNR. Jun, 2014 Versión 5 Problemas Resueltos: 1. Se requiere un DAC capaz de cubrir un rango de salida de al menos 10 V, y un paso entre niveles de salida discretos menor o igual a 4 mV. Además se requiere que sea capaz de cambiar su salida por lo menos 250.000 veces por segundo. Seleccione el DAC adecuado desde la tabla inferior y justifique su opción. Modelo DAC821 DAC7514 DAC7616 DAC8C12P Resolución, bits 8 14 16 12 VREF-, mín 0 -2.5 -5 -10 VREF+, máx 10 2.5 5 10 tset, µs 1.5 0.1 10 3 Sol. Analizando la tabla, se obtienen las siguientes conclusiones: • El DAC821 ofrece adecuado rango de salida entre sus referencias, pero la resolución 8 es inadecuada, por cuanto el LSB = 10/2 = 39 mV entre niveles de salida, lo cual excede el criterio de los 4 mV. • El DAC7514 ofrece una resolución adecuada y un tiempo de estabilización tsettle muy pequeño, pero el rango de salida está restringido a 5 V. • El DAC7616 conjuga una excelente resolución (LSB = 10/2 = 0.15 mV) y el rango deseado de 10 V entre referencias (5 –(-5) V), pero su tiempo de estabilización de 10 µs implica que su salida puede cambiar con una frecuencia 1/(10E-6) = 100 kHz. Como se requiere una frecuencia de operación de 250 kHz, este DAC no es adecuado para el problema. • El DAC8C12P cumple todos los criterios: permite un rango máximo de 20 V entre referencias, sus 12 bits de resolución implican un paso entre niveles de 2.4 mV y su tiempo de estabilización permite una frecuencia de operación de hasta 333 kHz (conversiones por segundo). 16 1 2. Se desea muestrear, mediante un ADC, una señal cualquiera de la que se conocen los siguientes datos: i. La potencia máxima de la señal alcanza los 800 mW ii. La potencia mínima es de 0,1 mW iii. Su frecuencia máxima alcanza los 10 kHz. Determine: a) El rango dinámico (DR) de la señal Solución. El DR puede calcularse como: DR = 10 log Pmax 800 = 10 log = 10 log 8000 = 39,03dB Pmin 0 .1 b) La mínima cantidad de bits de resolución (del ADC) requerida para evitar distorsión y que cumpla con el SNR. Solución: Para determinar la cantidad ‘n’ de bits de resolución se asume que DDR (rango dinámico digital) es igual al rango dinámico (DR) de la señal. Es decir, DDR=39.03 dB. Además se sabe que DDR = 6,02 ⋅ n , con lo que n= DDR 39,03 = = 6,48 ≈ 7 bits 6,02 6,02 El resultado de ‘n’ debe aproximarse al entero siguiente si no es exacto. Con 7 bits de resolución, el ADC puede muestrear señales con un DR de hasta 6,02*7 = 42,14 dB. De esto se desprende que el DDR real del ADC (42,14 dB) es mayor que el DDR supuesto para el cálculo (39,03 dB), pero ello es correcto por cuanto DDR debe ser igual o mayor que DR. c) El tiempo de conversión requerido para satisfacer la frecuencia máxima de la señal. Solución. Este ítem se relaciona con Nyquist. Si la frecuencia máxima medida de la señal alcanza 10 kHz, entonces se requiere una frecuencia mínima de muestreo del doble, es decir, 20 kHz. Para tener esta frecuencia de muestreo, el tiempo de conversión debe ser de 1 / 20kHz = 50 uS. 2 Problemas Propuestos: 1. Se requiere un conversor DAC capaz de ofrecer por lo menos 200 niveles de salida para un rango de salida entre -5 y +5 V, a un mínimo de 20000 conversiones por segundo. Determine: i. Resolución en bits mínima que cumpla con el problema (Sugerencia: utilice log2 de la cantidad de niveles). ii. Tiempo de estabilización requerido para la frecuencia especificada. iii. Máxima frecuencia en la salida análoga que el DAC puede representar, según Nyquist. 2. Se desea utilizar un DAC para generar una onda senoidal bipolar de 1 kHz de frecuencia, con 200 muestras por ciclo y una amplitud peak-to-peak de 20 V, sin componente continua. Al respecto: i. Especifique la cantidad de bits de resolución, tales que el paso entre niveles de salida sea menor o igual a 0.5 mV ii. Calcule el máximo tiempo de conversión aceptable para lograr la frecuencia requerida de la onda pseudo-senoidal en la salida. iii. Especifique los voltajes de referencia requeridos 3. Se tiene un DAC conectado con voltajes de referencia Vref+=8V, Vref-=0 V. Si el LSB es 62,5 mV determine: a. Resolución en bits del DAC b. Rango dinámico análogo máximo representable en su salida c. Máxima frecuencia que puede representar en su salida si su tiempo de estabilización es de 250 us. 4. Un canal de comunicación posee un SNR de 75 dB, y su nivel de ruido base es de 0.5mW. Determine entonces la potencia máxima de señal que entrega este canal. 3 5. Se tiene un ADC de 10 bits de resolución, con referencias simétricas, VREF-= -8V. Su tiempo de conversión es de 100us. a. Dibuje el ADC considerando todos sus terminales conectados a los voltajes correspondientes, tanto analógicos como digitales. b. Resultado digital si se aplica VIN = 9 V c. Resultado digital para VIN = 0 V. d. A qué voltaje en la entrada corresponde una salida digital N=1110110101 binario. e. Determine la máxima cantidad de muestras por segundo que el ADC puede tomar. f. Determine si el ADC puede convertir una señal cuya amplitud fluctúa entre 0,1 mV y 5V, en términos de rango dinámico, sin producir distorsión en amplitud g. Suponga que se desea que el ADC adquiera datos durante 6 meses sin parar, a razón de 15 conv/s. Si se usan 2 bytes por cada conversión de 10 bits, determine la cantidad de memoria necesaria, en Mbytes, para cumplir con el requerimiento. Considere meses de 30 días, 1Mbyte=1048576 bytes. 6. Se dispone de un ADC ideal de 8 bits de resolución, con voltajes de referencia simétricos, Vref+ = +8V. Además, su tiempo de conversión es de 10 uS. Al respecto: a. Determine el rango dinámico digital del conversor (DDR). b. Determine si el DDR del mismo es adecuado para una señal análoga en la entrada cuya amplitud mínima es 0,3 mV y la máxima es 3V. 7. Se dispone de un DAC ideal de 11 bits de resolución, con voltajes de referencia Vref+ = 8V y Vref- =0V. Dibuje el DAC con sus conexiones y determine: a. b. c. d. e. Valor del LSB Resultado análogo (VOUT) si se aplica entrada N=128. Diferencia en % entre la salida análoga máxima del DAC y voltaje Vref+ A qué entrada digital corresponde una salida de 2.5V Si tset=2.5uS, calcule cuantas veces por segundo puede actualizar su salida análoga. 4