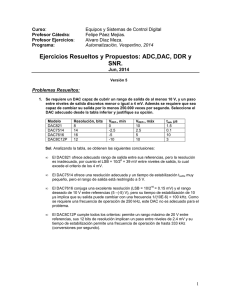

Ejercicios Resueltos ADC / DAC

Anuncio

Curso: Profesor: Programa: Equipos y Sistemas de Control Digital Felipe Páez M. Automatización, Vespertino, 2010 Ejercicios Resueltos ADC / DAC Versión 1.1 Problemas Resueltos: 1. Se tiene un DAC ideal de 10 bits, con tiempo de estabilización total tset de 12 µs. Está conectado en una configuración con VREF- a tierra y VREF+=12 V. Al respecto: a. Calcule el valor del LSB. Sol. El paso entre valores de voltaje discretos, también conocido como LSB, corresponde a: V −V LSB = REF + n REF − donde n=10 bits. 2 Por tanto el LSB= 12/210 = 0.01171875 volts b. Calcule la máxima salida análoga y el error de escala completa expresado como porcentaje de la misma. Sol. La máxima salida análoga se produce para una entrada digital N=1111111111 binario, o (210) – 1=1023 decimal. Por tanto, la salida análoga sería 1023*LSB = 11.9883 V. El error de escala completa corresponde a la salida máxima ideal menos la real, es decir, 12 V – 11.9883 V = 0.0117 V. Para expresarlo como porcentaje, se recurre a la proporción: 100% 12V = x% 0.0117V de donde x=(0.0117 * 100)/12 = 0.098 % c. Calcule la salida para el valor 1001100011 binario. Sol. La entrada N=1001100011 b = 29 + 26 + 25 + 21 + 20 = 611 dec., por tanto la salida será 611·LSB = 7.16 V. d. Determine si una frecuencia de trabajo del DAC de 150 kHz respeta sus condiciones de operación. Justifique. 1 Sol. La frecuencia de entrada o trabajo del DAC determina la cantidad de veces por segundo que el DAC debe convertir la entrada digital en salida análoga. Es evidente que, para una operación fiable, no puede exigírsele al DAC que realice la conversión en un tiempo menor al de estabilización. Por tanto, para una frecuencia de trabajo de 150 kHz, se tendría que el tiempo entre conversiones debe ser de 1/150000 = 6.67 µs, pero el mismo DAC requiere de por lo menos 12 µs para estabilizar la salida, por lo que esta frecuencia de trabajo en la entrada es inadecuada para el conversor. 2. Se dispone de un ADC ideal de 8 bits de resolución, con voltajes de referencia Vref+ = +10V y Vref- a tierra. Además, su tiempo de conversión es de 20 uS. Determine: a. Valor del LSB Sol. LSB = V REF + − V REF − donde n=8 bits y Vref- = 0. 2n Por tanto el LSB= 10/28 = 0,0390625 volts b. Resultado digital si se aplica VIN = 4.68 V V − V REF − , donde la Sol. Para el ADC ideal, la salida digital N = 2 n IN V REF + − V REF − parte fraccionaria de N se elimina si existe. En este caso, para n=8 bits, 4.68 − 0 N = 28 = 119.808 , que debe aproximarse a N=119. 10 − 0 c. Resultado digital para VIN = 10 V. Sol. Para VIN ≥ VREF+ , asumiendo que este voltaje de entrada no quema al conversor, se produce un fenómeno de saturación, donde N es el máximo posible para la cantidad de bits dada, es decir, N=2n – 1. En este caso, N=28 – 1 = 255. d. A qué voltaje en la entrada corresponde una salida digital N=11010101 binario. Sol. En primer lugar es necesario traducir a decimal la salida N dada, en este caso, N = 128+64+16+4+1 = 213. Luego se despeja el término VIN en la V − V REF − , reemplazando todos los demás valores ecuación N = 2 n IN V REF + − V REF − 2 v −0 conocidos. En este caso, 213 = 2 8 IN , de donde se despeja que VIN = 10 − 0 8.3203 V. e. Si ahora se mantiene VREF+ en 10 V pero se usa una configuración simétrica, determine la salida N para VIN = -2 V. Sol. El cambio a la configuración simétrica implica que VREF- = -VREF+ , por tanto ahora VREF- = -10V. Aplicando entonces la fórmula anterior V − V REF − , se tiene que N=102.4 que se “recorta” a N=102. N = 2 n IN V REF + − V REF − f. Determine la máxima cantidad de muestras por segundo que el ADC puede tomar. Sol. Si el tiempo de conversión es tconv = 20 µs , entonces su frecuencia de 1 1 1 muestreo es de f s = = = = 50 Khz . Entonces, el ADC tconv 20 µs 20 ⋅ 10 −6 s toma 50000 muestras por segundo, que también se expresa como 50 kS/s (kiloSamples / segundo). 3. Un ADC con tecnología de aproximaciones sucesivas posee 12 bits de resolución y requiere 1 pulso de reloj por cada bit de salida. El tiempo de conversión total se cuenta desde el primer hasta el último pulso. Según el fabricante, la frecuencia máxima de muestreo es de 80 KHz, pero la entrada de reloj admite pulsos de hasta 1.2 MHz. Al respecto: a. Calcule qué frecuencia de reloj se requiere para hacer trabajar al ADC a su máxima frecuencia de muestreo. Sol. Puesto que el ADC es de 12 bits y requiere un pulso por bit, se establece la relación entre la frecuencia de reloj fCLK (del tren de pulsos) y la frecuencia de conversión fCONV (cantidad de muestras por segundo, tambien llamada frec. de muestreo): f CLK 12 Por tanto, para lograr que el ADC trabaje con una frecuencia de muestreo fCONV = 80 kHz, f CLK = 12 ⋅ 80kHz = 960kHz f CONV = b. Calcule la frecuencia de muestreo que se obtendría al aplicar la máxima frecuencia de reloj. ¿Es aceptable para la especificación del ADC ? 3 Sol. La máxima frecuencia de reloj es fCLK=1.2 Mhz = 1200 kHz. Según la ecuación anterior, a esta frecuencia el ADC debiera convertir a una fCONV de 1200/12 = 100 kHz, lo que excede el máximo para fCONV, que es de 80 kHz; por tanto fCLK=1.2 Mhz no es aceptable para este ADC. c. Si este ADC ampliara su resolución a 24 bits, manteniendo sus demás especificaciones, calcule el tiempo de conversión que se obtendría con una frecuencia de reloj de 480 kHz Sol. Si ahora n=24 bits, la fórmula anterior queda: f f CONV = CLK , donde fCLK = 480 kHz. 24 Evaluando, fCONV=20 kHz < 80 kHz (máximo fCONV), lo que implica que no hay problema para muestrear a esta frecuencia. 4. Se dispone de un DAC ideal con 12 bits de resolución, Está conectado en una configuración con VREF- = -6 V y VREF+=10 V. Al respecto: a. Determine la salida anàloga para entrada N=2541 dec. V REF + − V REF − donde 2n n=12 bits. Por tanto el LSB= 16/212 = 0.00390625 V. Luego, la salida VOUT se calcula como VOUT = N ⋅ LSB + V REF − , donde reemplazando los valores del problema se obtiene que VOUT = 3.926 V. Sol. En primer lugar se determina el LSB, usando LSB = b. Determine qué entrada N debe aplicarse al DAC para obtener VOUT = 8 V. Sol. La entrada N a calcular se obtiene reemplazando el voltaje de salida deseado, junto con el LSB y el voltaje VREF- en la fórmula VOUT = N ⋅ LSB + V REF − , y se procede a despejar N. En este caso, V − V REF − N = OUT =3584 dec. LSB c. El DAC puede entregar hasta 10 mA en su salida antes de que su voltaje caiga producto de la carga aplicada. Determine, para la máxima salida análoga de voltaje posible, la mínima impedancia resistiva requerida para que respete esta limitación. Sol. En términos de circuito, el problema plantea lo siguiente: 4 i out + RL vout DAC - Debe respetarse que iout no supere los 10 mA, ya que de otro modo el voltaje de salida del DAC caería respecto al esperado de acuerdo a su entrada digital N. En este caso, si Vout se ha fijado en 10 V, la resistencia de carga se calcula V 10V simplemente como RL = out = = 1Kohm . Cualquier valor inferior iout 0,01A para esta resistencia provocaría que la corriente de salida fuera mayor y por tanto, dado que el DAC no puede proporcionarla, el efecto sería que el voltaje de salida caería en su valor, además de sobrecargar el circuito. d. Conecte un amplificador operacional a la salida del DAC para solucionar este problema. Sol. El problema de la poca capacidad de carga del DAC se puede solucionar con un amplificador operacional conectado en ganancia unitaria: iout + DAC vout + - iamp + RL vout - El operacional proporciona una corriente iamp mucho mayor que iout, al tiempo que su entrada (+) consume unos pocos microamperes, en la mayoría de los casos. Por tanto, su voltaje de salida es el mismo que el del DAC, pero con una capacidad de carga mucho mayor. Otro beneficio de esta configuración es que la carga no queda conectada directamente al conversor y por tanto su operación es más segura. 5