Universidad de Puerto Rico Recinto Universitario de Mayagüez

Anuncio

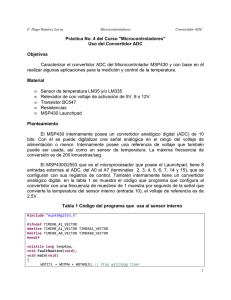

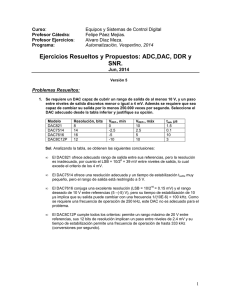

Universidad de Puerto Rico Recinto Universitario de Mayagüez Departamento de Ingeniería Eléctrica y Computadoras Experimento #9: Convertidores de Analógico a Digital Giselle M. Bonilla Ortiz 802-00-0809 Carlos M. Rubert 802-01INEL 4225 Sección 14A Instructor: María Fernanda Naranjo I. Objetivos: 1- Estudiar varias técnicas para conversión de analógico a digital. 2- Diseñar y construir un convertidor de analógico a digital (ADC) de aproximaciones sucesivas. 3- Entender como funciona un convertidor DAC de aproximaciones sucesivas. 4- Conocer las limitaciones y desventajas de este tipo de ADC. II. Marco Teórico: Un convertidor análogo a digital es un circuito que tiene una línea de entrada análoga y n líneas de salida digitales. Genera el código binario que es proporcional a la entrada de voltaje análoga. Todos los ADC requieren al menos un comparador análogo, un elemento que acepte dos entradas análogas de voltaje y produzca una salida digital. Diferentes tipos de convertidores análogo a digital han sido desarrollados a través del tiempo. Los más populares son el de rampa o escalera y el de aproximaciones sucesivas. El ADC contador de rampa es el más lento y simple de los ADC secuenciales. El registro de resultados es un contador de n bits que se pone en cero al comenzar la conversión. Mientras la salida del convertidor DAC sea menor que la entrada analógica, al contador se le permite seguir contando. Cuando la salida del DAC sea mayor que la entrada analógica el contador se detiene, su valor almacenado es el resultado, Esta técnica requiere un máximo de 2n pasos para realizar la conversión de n bits. En esta y todas la técnicas secuenciales el tiempo que toma cada paso debe ser mayor que el tiempo de estabilización del control digital, del DAC y del comparador. En este experimento vamos a estudiar sólo el de aproximaciones sucesivas. Esta técnica requiere sólo n ciclos de reloj para lograr una aproximación de n-bits. Este circuito opera de la siguiente manera. En el primer pulso de reloj el SAR es puesto en 1. Si la salida del comparador se mantiene alta este bit es mantenido en 1; si el comparador tiene una salida baja, el MSB es puesto en 0 por el SAR. En el próximo pulso de reloj el bit número 6 es puesto en 1, y como antes, si la salida del comparador es alta, este bit es mantenido en lógica 1. Este procedimiento es repetido seis veces más, y después de un total de de 8 ciclos, la conversión esta completa. Si la señal de entrada analógica al ADC puede cambiar significativamente durante la conversión, un circuito llamado "sample & hold" debe ser utilizado. El circuito "sample & hold" muestrea el voltaje de entrada por un período corto de tiempo precediendo la conversión y retiene un voltaje constante de salida por la duración de la conversión. El "sample & hold" puede ser utilizado si las variaciones del voltaje de entrada durante el tiempo de conversión excede la resolución del ADC. La Figura que se muestra a continuación muestra un convertidor AD combinacional, la cual es la manera mas rápida de realizar la conversión. Cada comparador tiene un voltaje de referencia Vmax*i/2n para la entrada V- y el voltaje de entrada analógico a ser convertido en la entrada V+. Todos los comparadores cuyas referencias sean menores que la entrada analógica tienen una salida de 1, y los demás tienen una salida de 0. Las salidas del comparador están conectadas a un codificador digital de prioridad, que es un circuito combinacional de 2n entradas que produce la codificación de n bits de la posición de la entrada más alta. Otra configuración del ADC se conoce como el “Flash ADC”. Es la mas fácil de implementar y una de las mas rápidas. Pero también es una de las mas grandes en términos de piezas de interconexión, ya que requiere 2N comparadores para hacer una conversión de N bits De igual manera que ocurría con un DAC, las salidas de un ADC muestran un margen de error al compararlas con la salida del modelo ideal: Al igual forma que como se puede hacer con un DAC, este error de offset se puede corregir con una señal de offset en la entrada. Las causas para este error son iguales que las causas de offset para un DAC: errores de cuantización, ruido en el sistema, alguna nolinealidad o un error de “offset”. Preguntas: Vin 0.0 0.1 0.3 0.7 1.0 2.0 2.5 3.5 5.0 7.0 9.0 9.4 9.7 10.0 Palabra Calculada 000 000 000 000 001 001 010 010 100 101 111 111 111 111 Palabra Obtenida 000 000 000 000 000 001 010 010 100 101 111 111 111 111 III. Conclusión: