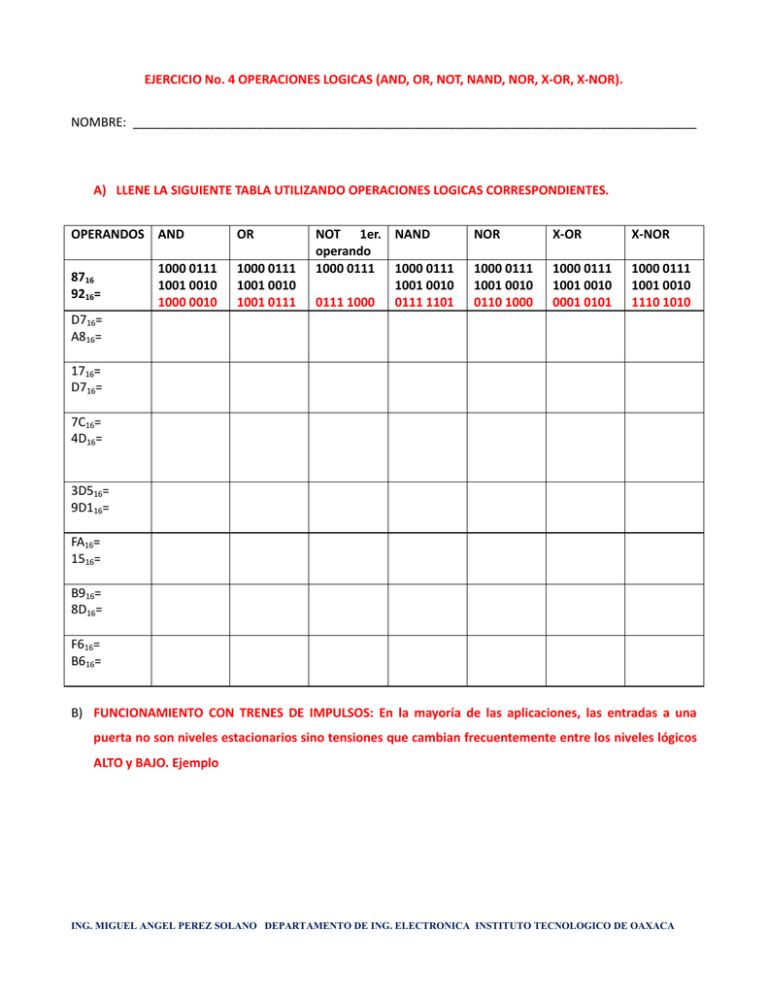

EJERCICIO No. 4 OPERACIONES LOGICAS (AND, OR, NOT

Anuncio

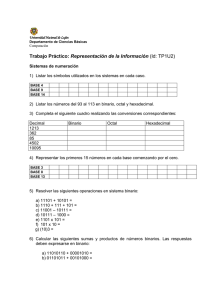

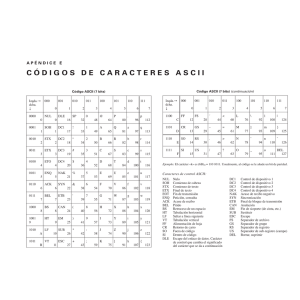

EJERCICIO No. 4 OPERACIONES LOGICAS (AND, OR, NOT, NAND, NOR, X-OR, X-NOR). NOMBRE: __________________________________________________________________________________ A) LLENE LA SIGUIENTE TABLA UTILIZANDO OPERACIONES LOGICAS CORRESPONDIENTES. OPERANDOS AND 8716 9216= D716= A816= 1000 0111 1001 0010 1000 0010 OR 1000 0111 1001 0010 1001 0111 NOT 1er. NAND operando 1000 0111 1000 0111 1001 0010 0111 1000 0111 1101 NOR X-OR X-NOR 1000 0111 1001 0010 0110 1000 1000 0111 1001 0010 0001 0101 1000 0111 1001 0010 1110 1010 1716= D716= 7C16= 4D16= 3D516= 9D116= FA16= 1516= B916= 8D16= F616= B616= B) FUNCIONAMIENTO CON TRENES DE IMPULSOS: En la mayoría de las aplicaciones, las entradas a una puerta no son niveles estacionarios sino tensiones que cambian frecuentemente entre los niveles lógicos ALTO y BAJO. Ejemplo ING. MIGUEL ANGEL PEREZ SOLANO DEPARTAMENTO DE ING. ELECTRONICA INSTITUTO TECNOLOGICO DE OAXACA Si se aplican las formas de onda A y B a las entradas de una puerta, ¿cuál es la forma de onda resultante de salida? ING. MIGUEL ANGEL PEREZ SOLANO DEPARTAMENTO DE ING. ELECTRONICA INSTITUTO TECNOLOGICO DE OAXACA ING. MIGUEL ANGEL PEREZ SOLANO DEPARTAMENTO DE ING. ELECTRONICA INSTITUTO TECNOLOGICO DE OAXACA • A continuación se muestra una red de inversores en cascada. Si s aplica un nivel ALTO en el punto A, determinar los niveles lógicos de los puntos B hasta F. • Las señales de entrada que se aplican a una puerta AND de tres entradas que se muestra. Determinar la señal de salida para las entradas dadas en función del tiempo, utilizando un diagrama de tiemp ING. MIGUEL ANGEL PEREZ SOLANO DEPARTAMENTO DE ING. ELECTRONICA INSTITUTO TECNOLOGICO DE OAXACA • Para el conjunto de señales de entrada de la siguiente figura, determinar la salida de la puerta mostrada y dibujar el diagrama de tiempos • Determinar la señal de la salida correspondiente a la Figura. ING. MIGUEL ANGEL PEREZ SOLANO DEPARTAMENTO DE ING. ELECTRONICA INSTITUTO TECNOLOGICO DE OAXACA