Clase lab 1

Anuncio

LAB 1

Introducción a Verilog

Laboratorio de Sistemas Digitales

ELO212

Primer Semestre de 2012

Objetivos Generales

Conocer

aspectos básicos de Verilog.

Diseñar circuitos con Verilog.

Hacer pruebas funcionales y

temporales de diseños.

Trabajar bajo un ambiente ISE

(Integrated Software Environment).

Recursos

Lenguajes para descripción de Hardware

◦ Esquemáticos y diagramas en bloques.

◦ Lenguajes de programación:Verilog,VHDL.

Software para Diseño

◦

◦

◦

◦

ISE Design Suite de Xilinx

Digilent Adept Suite

VeriWellgtkwave

Cygwin

Simuladores

◦ Isim

◦ VeriWell & gtkwave

Hola Mundo en Verilog

module hello_world ;

initial begin

$display (“Hola Mundo!");

#10 $finish;

end

endmodule

Mi Primer Programa en Verilog

Descripción de Circuitos:

◦ Estructural.

◦ De comportamiento.

Descripción Estructural

module sAnd(a, b, c, f);

input a, b, c;

output f;

and (f, a, b, c);

endmodule

Descripción Basada en el

Comportamiento de la Red

module sAnd(a, b, c, f);

input a, b, c;

output f;

assign f = a & b & c;

endmodule

Bloque always

module sCAnd(a, b, c, en, f);

input a, b, c, en;

output reg f;

always@(*) begin

if (en) f = a & b & c;

else f = f;

end

endmodule

Uso de Buses

module mux21(ctl, e, s);

input [0:1] e;

input ctl;

output reg s;

always@(*)

if (ctl == 0) s = e[1]; else s = e[0];

endmodule

Definición de Constantes

Sin especificación de largo

◦ Octal: 'o372

◦ Hexadecimal: 'hFe31

◦ Decimal: 321

Con especificación de tamaño

◦ Binario: 5'b01101

◦ Hexadecimal: 12'h72

◦ Decimal: 11'd3029

Diseño Jerárquico

module mux41(ctl, e, s);

input [0:1] ctl;

input [0:3] e;

output s;

wire s1, s2;

mux21 m1(ctl[1], e[2:3], s1);

mux21 m2(ctl[1], e[0:1], s2);

mux21 m3(ctl[0], {s2,s1}, s);

endmodule;

Decodificador BCD – Decimal (1)

//

//

//

//

//

//

//

//

//

//

1-of-10 inverting decoder/demultiplexer.

+----------+

+-------------------------------+

/Y0 |1 +--+ 16| VCC

| S3| S2| S1| S0|/Y0|/Y1|...|/Y9|

/Y1 |2

15| S0

|---+---+---+---+---+---+---+---|

/Y2 |3

14| S1

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

/Y3 |4

13| S2

| 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 |

/Y4 |5 7442 12| S3

| . | . | . | . | 1 | 1 | . | 1 |

/Y5 |6

11| /Y9

| 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 |

/Y6 |7

10| /Y8

| 1 | 0 | 1 | X | 1 | 1 | 1 | 1 |

GND |8

9| /Y7

| 1 | 1 | X | X | 1 | 1 | 1 | 1 |

+----------+

+-------------------------------+

Decodificador BCD – Decimal (2)

module v7442(A, Y);

input [3:0] A;

output [9:0] Y;

assign

assign

assign

assign

assign

assign

assign

assign

assign

assign

endmodule

Y[0]

Y[1]

Y[2]

Y[3]

Y[4]

Y[5]

Y[6]

Y[7]

Y[8]

Y[9]

=

=

=

=

=

=

=

=

=

=

~(A

~(A

~(A

~(A

~(A

~(A

~(A

~(A

~(A

~(A

==

==

==

==

==

==

==

==

==

==

4'b0000);

4'b0001);

4'b0010);

4'b0011);

4'b0100);

4'b0101);

4'b0110);

4'b0111);

4'b1000);

4'b1001);

Circuito Verificador

module test_v7442;

reg [3:0] A;

// Inputs

wire [9:0] Y; // Outputs

v7442 uut (

// Instantiate the Unit Under Test (UUT)

.A(A), .Y(Y)

);

initial begin

A = 0;

#(100)

finish

// Initialize Inputs

// Wait 100 time unit for global reset to

// Add stimulus here

repeat (16) begin

#(10) A = A + 1;

$display ("t=%t \t\t\t A=%d \t\t\t Y=%b", $realtime, A, Y);

end

end

endmodule

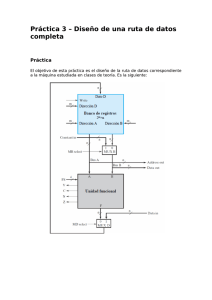

Trabajo Previo (1)

Estudio de Verilog

(s P1.2) Diseño de un programa en Verilog

◦ f(a,b,c,d) = abc + ab’d’ + a’c’d

◦ Descripción estructural

◦ Descripción de comportamiento

(s P1.3) Diseño usando bloque always

◦ Si ctl es 1, f = abc + ab’d’ + a’c’d

◦ Si ctl es 0, f = ab’c’d

Trabajo Previo (2)

(s P1.4) Modificar módulo mux21

◦ Diseñar de un módulo mux41 (multiplexor 4 a 1)

(s P1.5) Usando diseño jerárquico

◦ Diseñar un multiplexor 16 a 1 en base al módulo mux41

Diseño de módulos de prueba

◦ Circuito del punto P1.3 (bloque always)

◦ Circuito del punto P1.5 (mux. 16 a 1)

◦ AYUDA: incluya un estamento – initial – para inicializar

variables de salida.

Ejemplo mux21: initial s = 0;

En el Laboratorio (1)

Revisión actividades previas.

Simulación temporal y funcional.

◦ Circuito punto 2.3 (bloque always y ctl)

◦ Circuito contador de secuencias

Uso de monitor().

Uso de $display y $strobe.

En el Laboratorio (2)

Diseño de un circuito:

◦ Si entrada tiene número par de unos:

e = 011010010011000, s = 1111110000000000

◦ Si entrada tiene número impar de unos:

e = 011010010011001, s = 0000000001111111