SUMA/RESTA ACUMULADA

Anuncio

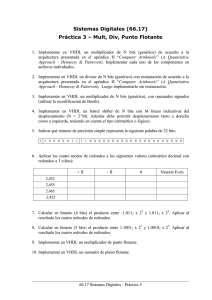

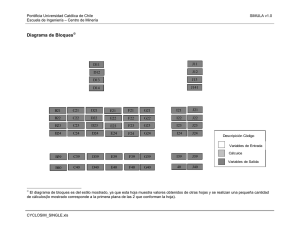

Introducción a la simulación de sistemas digitales 04-05 UPV LDD Ejemplo: SUMA/RESTA ACUMULADA ATC OBJETIVO: En estas sesiones de laboratorio vamos a estudiar una de las herramientas software habituales que se utilizan para el diseño de sistemas digitales. Existen varias alternativas en el mercado; en este curso vas a utilizar un paquete comercial muy común, MAX+plus II de la casa ALTERA, para implementar diseños en dispositivos de lógica programable. Para estudiar este conjunto de aplicaciones vamos a diseñar un pequeño sistema digital, siguiendo todos los pasos habituales: definición del sistema lógico, dibujándolo o mediante lenguajes tipo VHDL, compilación, simulación, e implementación en un dispositivo concreto utilizando la placa UP1. EJEMPLO: Se ha diseñado un sistema que suma o resta números naturales de dos bits y muestra el resultado acumulado en un registro. Los datos se introducen mediante dos interruptores. El sistema se controla mediante tres pulsadores: LD, S y R. Como ejemplo, sólo se considera la suma hasta 4 bits y no se consideran resultados negativos. Por ello, al superar el valor 15 (overflow), o si el resultado es <0 (underflow) no se pueden realizar más operaciones hasta pulsar LD. LD: carga en el registro de un dato de 4 bits. No existe señal de inicialización a cero; para introducir un 0 hay que ejecutar LD 0. Al cargar un dato los dos indicadores del sistema (overflow y underflow) se ponen a 0. S: suma de un número de dos bits al valor del registro, tal como se ha hecho en el ejemplo anterior (SUM). Al detectar overflow (>15), se activa el indicador OVF; a continuación sólo se admite una operación LD. R: resta de un número de dos bits al valor del registro. Al detectar underflow (<0), se activa el indicador UNF; a continuación sólo se admite una operación LD. El algoritmo de control y un esquema de la unidad de proceso aparecen en la figura e la pagina siguiente. Unidad de proceso: 0,0,N1,N0 4 Biest JK JOVF 4 4 J K KOVF Cout clk RESETL N3-0 4 4 OVF CL Rest Sumador Q Biest JK 0 Dat_0 1 Mux JUNF J K KUNF 4 clk Ld_R clk RESETL Registro 4 Unidad de control: RESET* E0 0 1 E1 LD 0 E2 KOVF KUNF DAT_0 LD_R 0 S 1 1 0 1 Cout (>15) JOVF 1 JUNF E5 1 LD Cout (< 0) 0 1 LD+S+R E3 LD_R REST LD_R E4 0 R 0 Q CL UNF TRABAJO A REALIZAR 1. DESCRIPCIÓN DEL DISEÑO En primer lugar se va a describir el diseño propuesto utilizando tanto el editor gráfico como el de texto. a) Editor gráfico (Unidad de proceso): Un diseño puede describirse gráficamente utilizando los símbolos de los módulos incluidos en alguna de la tres bibliotecas de la herramienta Altera, o bien, los de los diseños previos realizados por un usuario. En este caso, se va a describir la Unidad del proceso del ejemplo utilizando elementos de las citadas bibliotecas. Para ello consultar el resumen de la guía del usuario de la herramienta y seguir las siguientes pautas: • Usar la biblioteca de primitivas para puertas lógicas y biestables. • Usar la bibliotecas de CI estándar TTL de la serie 74 para el Sumador • Usar la biblioteca de módulos parametrizables para el registro de almacenamiento. y el multiplexor. b) Editor de texto para VHDL (Unidad de control): La Unidad de control se va a describir utilizando el lenguaje VHDL. Para ello seguir los pasos ya vistos en las clases teóricas y consultar la guía Altera para editar dicho fichero. c) Usar de nuevo el editor gráfico para generar la descripción del sistema completo: Unidad de control + Unidad de proceso. 2. SIMULACIÓN LÓGICA Se van a simular desde un punto de vista lógico las unidades previamente diseñadas. Para ello y tal como se describe en la guía de usuario Altera, los pasos a seguir son: a) Compilar el diseño: En primer lugar se realizará una compilación funcional simple. b) Editar las formas de onda de las señales de entrada del sistema a simular utilizando para ello el Editor de Formas de onda: Waveform Editor. c) Simular el diseño descrito en el orden siguiente: 1. Unidad de control: las posibles transiciones de estados (al menos los casos más críticos), las señales de salida a activar. 2. Unidad de proceso: las respuestas de los diferentes módulos incluidos 3. El sistema completo: realizar un estudio lo suficientemente representativo del funcionamiento del sistema sin alargarlo en exceso con casos redundantes. 3. COMPILACIÓN Y PROGRAMACIÓN EN UNA CPLD. Se va a implementar el diseño en una de los dispositivos disponibles en la placa UP1, en concreto el de la familia FLEX10K20, utilizando para ello el “ByteBlaster” que permite su programación directa desde el PC. Para poder visualizar de manera adecuada las salidas y aplicar las entradas se actuará de la siguiente manera: • Para el dato de entrada se utilizarán los microinterruptores • Asignaremos el pulsador PB1 a La señal S, y el pulsador PB2 a R. • Asignaremos microinterruptores a Reset, y a la señal LD. • Visualizaremos el estado del sistema en uno de los dígitos y el resultado en el otro NOTA: Para ello será necesario incluir en el diseño dos decodificadores Hex-7seg. . a) Tareas previas. Seleccionar el dispositivo concreto en el que se va a implementar el diseño, volver a compilarlo (esta vez con el dispositivo seleccionado). Añadir al diseño los módulos necesarios de acuerdo con las pautas del párrafo anterior, y realizar la asignación de pines de entrada/salida. Para ello consultar la guía del usuario y la información resumida de la placa UP1. b) Programar la CPLD Seleccionar en el menú “Programer”, verificar las conexiones de la placa UP1 al PC yl programarlo. c) Comprobar el funcionamiento del sistema real.