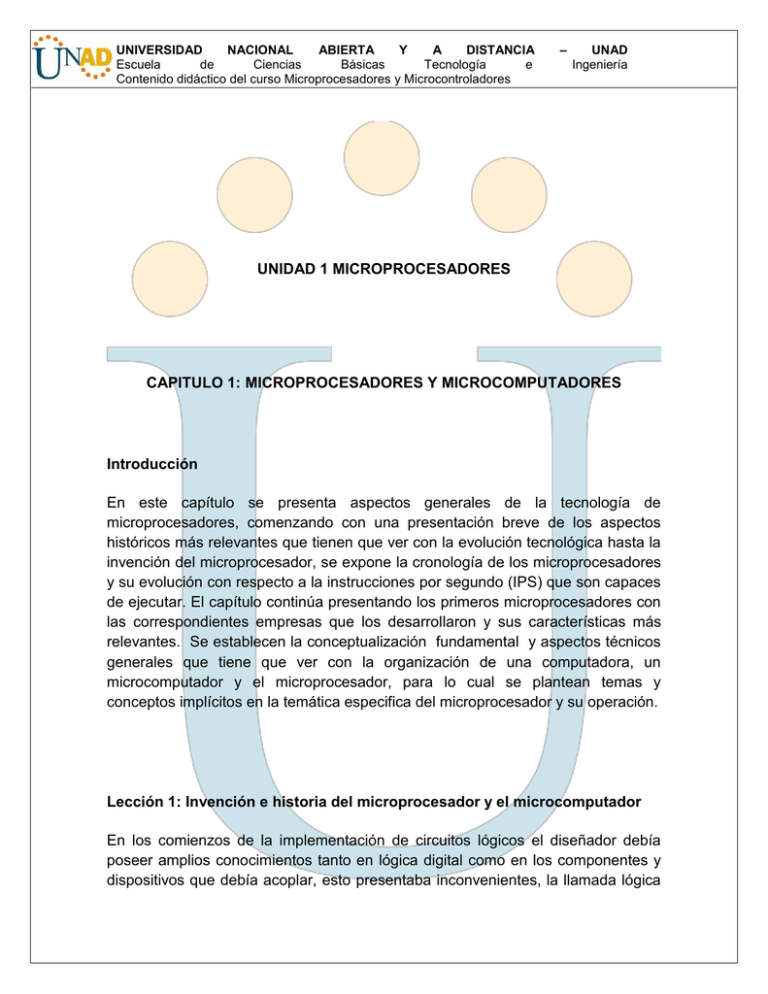

UNIDAD 1 MICROPROCESADORES CAPITULO 1

Anuncio