T4.1. S. Memoria

Anuncio

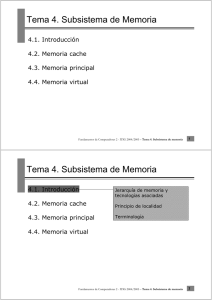

Tema 4. Subsistema de Memoria 4.1. Introducción 4.2. Memoria cache 4.3. Memoria principal 4.4. Memoria virtual Fundamentos de Computadores 2 - ITIG 2004/2005 – Tema 4. Subsistema de memoria 1 Tema 4. Subsistema de Memoria 4.1. Introducción Jerarquía de memoria y tecnologías asociadas 4.2. Memoria cache Principio de localidad 4.3. Memoria principal Terminología 4.4. Memoria virtual Fundamentos de Computadores 2 - ITIG 2004/2005 – Tema 4. Subsistema de memoria 2 1 4.1 I N T R O Introducción • Memoria Ideal Æ Rápida, grande y barata. – ¿Qué significa que sea “rápida”? • Monociclo Æ Poca latencia de operación (tciclo pequeño) • Multiciclo Æ Que no determine el tiempo de ciclo. – ¿Qué significa que sea “grande”? • Que el tamaño de la memoria no limite los programas que puedo ejecutar. – ¿Qué significa que sea “barata? • Abordable económicamente. • Sin embargo, la realidad es otra: – Las memorias grandes son lentas – Las memorias rápidas son pequeñas (y caras) Fundamentos de Computadores 2 - ITIG 2004/2005 – Tema 4. Subsistema de memoria 3 4.1 Diferencia de rendimientos entre memoria y procesador Gap Procesador- Memoria DRAM (latencia) 1000 CPU µProc 60%/año (2X/1.5años) “Ley de Moore” 100 Gap: crece 50%/año 10 DRAM DRAM 9%/año (2X/10 años) 1982 1983 1984 1985 1986 1987 1988 1989 1990 1991 1992 1993 1994 1995 1996 1997 1998 1999 2000 1 1980 1981 Rendimiento I N T R O Año Fundamentos de Computadores 2 - ITIG 2004/2005 – Tema 4. Subsistema de memoria 4 2 4.1 I N T R O Tecnologías de memoria (1) • Las tecnologías principales de memoria son • SRAM: Static Random Access Memory • Baja densidad, alto consumo potencia, cara, rápida • Estática Æ no necesita ser “refrescada” • DRAM: Dynamic Random Access Memory • Alta densidad, baja potencia, barato, lento • Dinámica Æ necesita ser “refrescada” regularmente • Disco Magnético • Cada tipo de memoria tiene sus características (1997): Tecnología de memoria Tiempo de acceso Coste por Mbyte SRAM 5-25 ns 100-250 $ DRAM 60-120 ns 5-100 $ 10-20 millones ns 0,10-0,20 $ Disco Magnético Fundamentos de Computadores 2 - ITIG 2004/2005 – Tema 4. Subsistema de memoria 5 4.1 I N T R O Tecnologías de memoria (2) • Tendencias tecnológicas: Capacidad 2x en 3 años 2x en 3 años DRAM: 4x en 3 años 2x en 10 años Disco: 4x en 3 años 2x en 10 años Año 1980 1983 1986 1989 1992 1995 • Velocidad (latencia) SRAM: Evolución de la memoria DRAM Tamaño Tiempo ciclo 64 Kb 250 ns 256 Kb 220 ns 1 Mb 190 ns 4 Mb 165 ns 16 Mb 145 ns 64 Mb 120 ns 1000:1! 2:1! ¿Podríamos hacer una memoria ideal con tecnología SRAM? Compromisos: • Capacidad-Velocidad Æ Alta capacidad y alta velocidad • Coste-Velocidad Æ Alta velocidad y bajo coste Fundamentos de Computadores 2 - ITIG 2004/2005 – Tema 4. Subsistema de memoria 6 3 4.1 I N T R O Tecnologías de memoria y tipos de acceso • El acceso puede ser aleatorio, pseudo-aleatorio y secuencial. – Acceso Aleatorio: • El tiempo de acceso es el mismo para todas las posiciones de memoria – Ejemplo: DRAM, SRAM – Acceso Pseudo-aleatorio: • El tiempo de acceso varía de una posición a otra y depende del momento en que se realice. – Ejemplo: Disco magnético, CDROM – Acceso Secuencial: • El tiempo de acceso depende de la localización del dato en el medio. – Ejemplo: Cinta magnética Fundamentos de Computadores 2 - ITIG 2004/2005 – Tema 4. Subsistema de memoria 7 4.1 I N T R O Impacto de la velocidad de la memoria en el rendimiento • Supongamos un procesador a 200 MHz (tciclo=5 ns), con un CPI medio de 1.1 ciclos con un sistema de memoria ideal para un programa determinado que tiene 50% de instrucciones aritmético-lógicas, 30% de instrucciones de cargaalmacenamiento (memoria) y 20% de instrucciones de control. • Si ahora ponemos un sistema de memoria real que provoca que el 10% de las instrucciones de memoria tengan una penalización de 50 ciclos, ¿cómo varía el CPI? CPI = CPImem_ideal + ciclos de bloqueo promedio por instrucción = = 1.1 + 0,30 * 0,10 * 50 = 1.1 + 1.5 = 2,6 ciclos por instrucción Rendimiento = Tcpu_mem_ideal / Tcpu_mem_real = N * 1.1 * 5 / N * 2.6 * 5 = 0.42 Æ Hemos perdido el 58% de rendimiento Æ El procesador pasa ahora el 58% del tiempo bloqueado esperando que lleguen los datos de memoria Fundamentos de Computadores 2 - ITIG 2004/2005 – Tema 4. Subsistema de memoria 8 4 4.1 I N T R O Organización jerárquica de la memoria • Objetivo: Dar la impresión al usuario de que tiene una memoria grande, rápida y barata. • ¿Cómo? – Organizando la memoria de forma jerárquica, compromiso entre Tecnología, Coste y Velocidad. • llegando así a un ¿En qué consiste? – En utilizar distintos niveles de memorias de forma que los niveles más cercanos al procesador utilizan tecnología más rápida (aunque son de menor tamaño y más caras) y los niveles más lejanos al procesador utilizan tecnología más lenta (y son de mayor tamaño y más baratas). Fundamentos de Computadores 2 - ITIG 2004/2005 – Tema 4. Subsistema de memoria 9 4.1 I N T R O Visión general del sistema de memoria Procesador Control Memoria Memoria Memoria Ruta de Datos Velocidad: Más rápida Tamaño: Más pequeña Coste: Más cara Memoria Memoria Más lenta Más grande Más barata Fundamentos de Computadores 2 - ITIG 2004/2005 – Tema 4. Subsistema de memoria 10 5 4.1 I N T R O ¿Por qué funciona la jerarquía de memorias? • Los programas no acceden de forma aleatoria a su código y a sus datos, sino que tienden a tener un comportamiento predefinido que sigue un determinado patrón. • Principio de localidad de referencia: Los programas acceden en cualquier instante de tiempo a una porción de memoria relativamente pequeña del espacio de direcciones total. Probabilidad de referencia en un instante de tiempo determinado 0 n Espacio de direcciones 2 -1 Fundamentos de Computadores 2 - ITIG 2004/2005 – Tema 4. Subsistema de memoria 11 4.1 I N T R O Principio de localidad • Localidad Temporal: Si se referencia una posición de memoria en un instante de tiempo determinado, existe una alta probabilidad de que vuelva a ser referenciada en los instantes siguientes. – Ejemplo: Instrucciones en bucles, variables • Localidad Espacial: Si se referencia una posición de memoria en un instante determinado, existe una alta probabilidad de que en los instantes siguientes se referencien las posiciones de memoria cercanas. – Ejemplo: Acceso a los elementos de un vector de datos, acceso a instrucciones secuenciales. Fundamentos de Computadores 2 - ITIG 2004/2005 – Tema 4. Subsistema de memoria 12 6 4.1 I N T R O Niveles de la jerarquía y tecnologías asociadas • Aplicando el Principio de Localidad: – Presentamos al usuario tanta memoria como sea posible en la tecnología más barata. – Proporcionamos acceso a la velocidad ofrecida por la tecnología más rápida. CPU Procesador Tipo de memoria Semiconductor SRAM Semiconductor L1 Cache SRAM Semiconductor L2 Cache SRAM Semiconductor Memoria principal DRAM Registros Registros Sistema Tarjeta Nivel jerárquico L1 Cache L2 Cache Memoria principal Disco Cinta Magnética Tecnología Tamaño Tiempo acceso 512 bytes 5 ns 32 KB 10 ns 512 KB 25 ns 32 MB Disco magnético Disco duro 2 GB Disco óptico CD-ROM xx GB Cinta magnética Cinta xx GB 75 ns 10 ms 10 MB/seg 300 ms 600 KB/seg seg-min 10 MB/min Discos ópticos Fundamentos de Computadores 2 - ITIG 2004/2005 – Tema 4. Subsistema de memoria 13 4.1 I N T R O Terminología (1) • Nivel superior e inferior – Entre dos niveles adyacentes de la jerarquía de memoria se denomina nivel superior al que está más cerca del procesador y nivel inferior al que está más lejos. – El nivel superior es siempre mas pequeño y rápido que el inferior. • Bloque – Es la unidad mínima de información que está presente o no en un nivel de la jerarquía. → Las transferencias de información se realizan siempre entre niveles adyacentes de la jerarquía. → La cantidad mínima de información que se transfiere es un bloque. Fundamentos de Computadores 2 - ITIG 2004/2005 – Tema 4. Subsistema de memoria 14 7 4.1 I N T R O Terminología (2) • Acierto y Fallo – Si los datos que se piden a un nivel se encuentran allí, se dice que se ha producido un acierto (hit). En caso contrario se produce un fallo (miss). – Cuando se produce un fallo en un nivel se accede al nivel inmediatamente inferior para buscar esa información. • Tasa de fallos y de aciertos – La tasa de aciertos de un nivel (hit rate) Æ porcentaje de accesos encontrados en ese nivel, sobre el total de accesos realizados a dicho nivel. – La tasa de fallos de un nivel (miss rate) Æ porcentaje de accesos no encontrados en ese nivel, sobre el total de accesos realizados a dicho nivel. También se define como (1-tasa de aciertos). Fundamentos de Computadores 2 - ITIG 2004/2005 – Tema 4. Subsistema de memoria 15 4.1 I N T R O Terminología (3) • La tasa de aciertos y/o la tasa de fallos se usan a menudo como medida del rendimiento de la jerarquía de memoria. – Menor tasa de fallos Æ menos veces hay que recurrir a los niveles más bajos (y más lentos) de la jerarquía Æ tiempo medio de acceso a memoria es mucho menor. – Una tasa de fallos baja indica que se accede pocas veces a los niveles más lentos de la jerarquía de memoria. Fundamentos de Computadores 2 - ITIG 2004/2005 – Tema 4. Subsistema de memoria 16 8 4.1 I N T R O Terminología (4) • Tiempo de acierto – Tiempo necesario para acceder a un datos en el nivel superior de la jerarquía. – Incluye el tiempo necesario para detectar si se trata de un acierto o de un fallo. • Penalización de fallo – Tiempo necesario para reemplazar un bloque del nivel superior por el correspondiente bloque del nivel inferior + Tiempo de suministrar este bloque al procesador. Tiempo de acierto << Penalización de fallo Fundamentos de Computadores 2 - ITIG 2004/2005 – Tema 4. Subsistema de memoria 17 4.1 I N T R O Evaluación del rendimiento de una jerarquía de memoria • Métrica de rendimiento – Tiempo medio que se tarda en hacer un acceso a memoria TMEDIO= Tiempo de acierto + Tasa de fallos * Penalización de fallos Fundamentos de Computadores 2 - ITIG 2004/2005 – Tema 4. Subsistema de memoria 18 9 4.1 I N T R O Cuestiones sobre cualquier nivel de la jerarquía de memoria • Q1: ¿Dónde puede ubicarse un bloque en el nivel superior? – Ubicación de bloque • Q2: ¿Cómo se encuentra un bloque si está en el nivel superior? – Identificación del bloque • Q3: ¿Qué bloque debe reemplazarse en caso de fallo? – Sustitución de bloque • Q4: ¿Qué ocurre en una escritura? – Estrategias de escritura • A continuación analizaremos cada una de estas cuestiones para los niveles de cache (nivel superior) y memoria principal (nivel inferior). Fundamentos de Computadores 2 - ITIG 2004/2005 – Tema 4. Subsistema de memoria 19 10