Unit 4. The processor Exercises

Anuncio

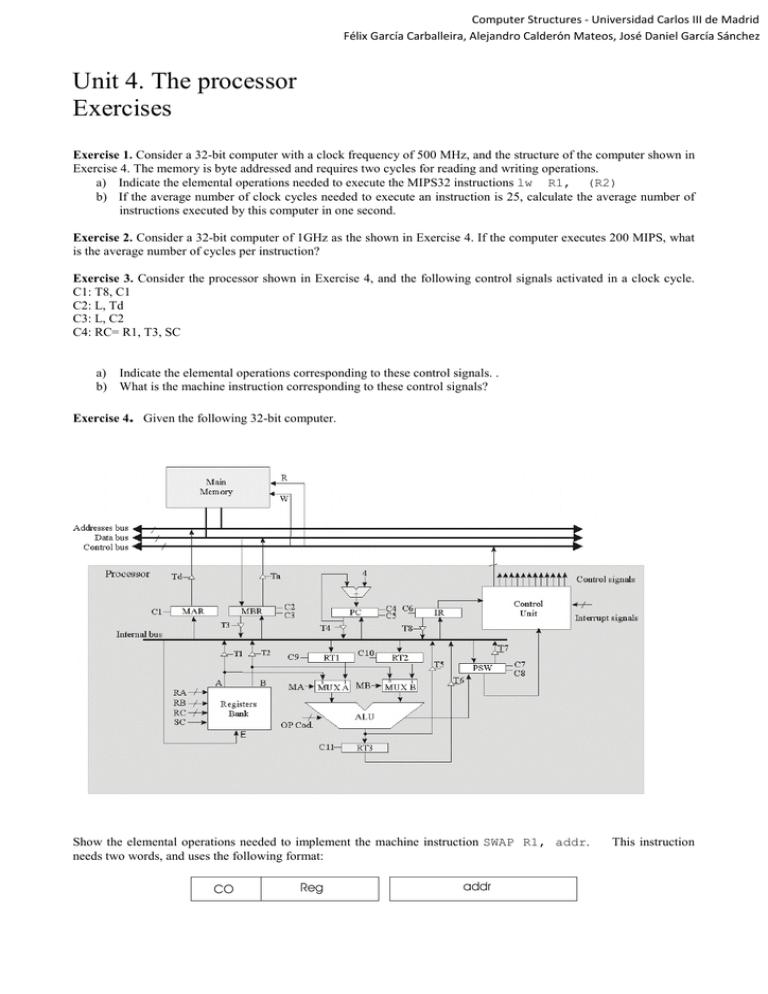

Computer Structures - Universidad Carlos III de Madrid Félix García Carballeira, Alejandro Calderón Mateos, José Daniel García Sánchez Unit 4. The processor Exercises Exercise 1. Consider a 32-bit computer with a clock frequency of 500 MHz, and the structure of the computer shown in Exercise 4. The memory is byte addressed and requires two cycles for reading and writing operations. a) Indicate the elemental operations needed to execute the MIPS32 instructions lw R1, (R2) b) If the average number of clock cycles needed to execute an instruction is 25, calculate the average number of instructions executed by this computer in one second. Exercise 2. Consider a 32-bit computer of 1GHz as the shown in Exercise 4. If the computer executes 200 MIPS, what is the average number of cycles per instruction? Exercise 3. Consider the processor shown in Exercise 4, and the following control signals activated in a clock cycle. C1: T8, C1 C2: L, Td C3: L, C2 C4: RC= R1, T3, SC a) Indicate the elemental operations corresponding to these control signals. . b) What is the machine instruction corresponding to these control signals? Exercise 4. Given the following 32-bit computer. Show the elemental operations needed to implement the machine instruction SWAP R1, addr. needs two words, and uses the following format: CO Reg addr This instruction This instruction exchange the content of the register Reg with the content of the memory address addr. Exercise 5. Given the computer shown in Exercise 4, with 32 registers, which is connected to a memory addressed by bytes. This memory uses two cycles in reading and writing operations. a) Describe the addressing modes used in the following instruction: sw $t1, 80($t2). b) Describe he elemental operations and control signals needed to execute the above instruction. Exercise 6. Next figure shows a simplified CPU of 32 bits. This CPU can execute 200 MIPS, and is connected to a memory addressed by bytes. The memory requires two cycles for reading and writing operations. The register bank has 16 registers, and two outputs (A and B), and one input (C). The register (R0) has always a zero value. UC REST C Banco de Registros SP PC RI A B BUS INTERNO DE LA CPU RDIR RT1 RDAT BUS DIRECCIONES BUS DATOS RT2 RT3 ALU Memoria Principal Reply: a) Describe the control signals used by this computer. b) Which elements are needed to interconnect the elements to the buses? Draw these components in the figure. c) Show the elemental operations and control signals corresponding to the fetch. Is there any problem in the fetch cycle? How can be solved? d) Show the elemental operations and control signal corresponding to the instruction ADD [R2], [R3]. This instruction adds the operand addressed by R2 to the operand addressed by R3, and stores the result in the operand addressed by R2. R2 and R3 use indirect register addressing. Exercise 7. A 32-bit computer as the shown in Exercise 4 has 32 registers, and a memory addressed by bytes with two cycles for reading and writing operations. Consider the instruction ADD, R1, addr. This instruction adds the value stored in R1 to the value stored in the memory address addr, and stores the result in the register R1. a) Show a possible format for this instruction, having into account that the computer has 100 machine instructions and the addresses are represented using 32 bits. b) Indicate the elemental operations and control signals needed to execute the previous instruction. Exercise 8. A computer A executes a program in 10 seconds, and a computer B executes the same program in 15 minutes. Which sentence is correct? a) A is 50% faster tan B b) A is 33% faster tan B