Construcción de la ruta de datos multiciclo

Anuncio

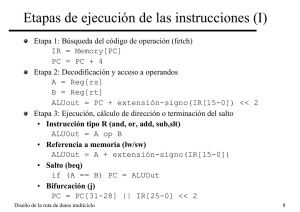

Diseño de la ruta de datos multiciclo para la arquitectura MIPS Diseño de la ruta de datos multiciclo 1 ¿Qué vamos a ver? Introducción Descripción del camino de datos multiciclo • Análisis del repertorio de instrucciones a implementar. Requisitos del camino de datos. • Selección de componentes • Construcción del camino de datos • Análisis de la implementación de cada instrucción. Puntos de control. Diseño de la ruta de datos multiciclo 2 Introducción Implementación MULTICICLO • División de la ejecución de las instrucciones en varias etapas o pasos Se ejecuta un paso de la instrucción en cada ciclo de reloj. Ventajas • Reutilización de las unidades funcionales Una unidad puede utilizarse más de una vez por instrucción siempre que se haga en ciclos de reloj distintos. • CPI variable Instrucciones sencillas Ö necesitan pocos ciclos de reloj para ejecutarse Instrucciones complejas Ö necesitan más ciclos de reloj que las anteriores Diseño de la ruta de datos multiciclo 3 Implementación multiciclo: componentes básicos Instruction register PC Address Memory Data Data A Instruction or data Memory data register Register # Registers Register # ALU ALUOut B Register # Una sola memoria para datos e instrucciones Una sola ALU en vez de 1 ALU y 2 sumadores Uso de registros temporales a la salida de las unidades funcionales principales. Dos tipos de registros: • Tipo A: Actualizan su contenido en cada instrucción (IR) • Tipo B: Actualizan su contenido en cada ciclo de reloj (MDR, A,B,ALUOut) Diseño de la ruta de datos multiciclo 4 Camino de datos multiciclo IorD PC 0 M u x 1 MemRead MemWrite IRWrite RegDst RegWrite Instruction [25– 21] Address Memory MemData Write data Instruction register Instruction [15– 0] Memory data register 0 M u x 1 Read register 1 Read Read data 1 register 2 Registers Write Read register data 2 Instruction [20– 16] Instruction [15– 0] ALUSrcA 0 M Instruction u x [15– 11] 1 A B 0 M u x 1 16 Sign extend 32 Shift left 2 ALUOut 0 4 Write data Zero ALU ALU result 1 M u 2 x 3 ALU control Instruction [5– 0] MemtoReg ALUSrcB ALUOp Compartición de unidades funcionales (reducción del hardware) Ö uso de multiplexores Ejecución en múltiples ciclos Ö cada ciclo requiere un conjunto determinado de señales de control Señales de control Diseño de la ruta de datos multiciclo 5 Etapas de ejecución de las instrucciones ¿Qué operaciones realizamos en cada ciclo de reloj? • Objetivo: equilibrar la carga computacional de cada etapa Ö Minimización del tiempo de ciclo • En cada etapa se va a realizar alguna de las siguientes operaciones: Un acceso a registro Actualización en cada ciclo (Registros temporales: MDR, A, B, ALUOut) Actualización según una señal de escritura (PC, IR) Un acceso a memoria Una operación de ALU ¿Cómo se determina el tiempo de ciclo mínimo? • Todas las operaciones de un ciclo se ejecutan en paralelo • Etapas o pasos de la instrucción se ejecutan en serie Diseño de la ruta de datos multiciclo 6 Camino de datos multiciclo completo con las señales de control PCWriteCond PCSource PCWrite IorD Outputs ALUSrcB MemRead MemWrite Control ALUSrcA RegWrite MemtoReg IRWrite ALUOp Op [5– 0] RegDst 0 M 26 Instruction [25– 0] PC 0 M u x 1 Shift left 2 Instruction [31-26] Address Memory MemData Write data Instruction [25– 21] Read register 1 Instruction [20– 16] Read Read register 2 data 1 Registers Write Read register data 2 Instruction [15– 0] Instruction register Instruction [15– 0] Memory data register 0 M Instruction u x [15– 11] 1 B 0 M u x 1 16 Sign extend 32 Shift left 2 x 2 Zero ALU ALU result ALUOut 0 4 Write data 1 u PC [31-28] 0 M u x 1 A 28 Jump address [31-0] 1 M u 2 x 3 ALU control Instruction [5– 0] Diseño de la ruta de datos multiciclo 7