Unidad Aritmético Lógica de 3 bits

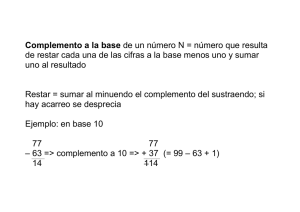

Anuncio

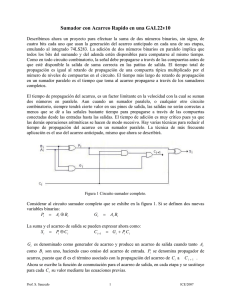

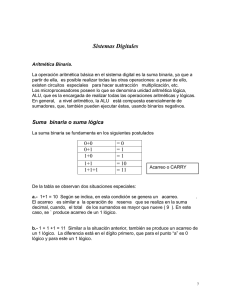

Unidad Aritmético Lógica de 3 bits Se trata de un circuito que realice el conjunto de operaciones definido en la Tabla 1 sobre dos números A y B de tres dígitos cada uno. Toma como base para la realización de las operaciones aritméticas un circuito sumador de dos números de cuatro bits (7483A) M S1 S0 Operación xi yi c0 A ai 0 0 Lógicas Aritméticas 0 0 0 Complemento 0 0 1 AND A⋅B a i⋅b i 0 0 0 1 0 Identidad A ai 0 0 0 1 1 OR A B a ibi 0 0 1 0 0 Decremento A−1 ai 1 0 1 0 1 Suma A B ai bi 0 1 1 0 Resta A− B ai bi 1 ai A1 1 1 1 Incremento 0 1 Tabla 1: Operaciones de la Unidad Aritmético Lógica (ALU) de tres bits El circuito trabaja con números en complemento a 2 para las operaciones aritméticas. Para la generación del desbordamiento (overflow) en las operaciones de suma o resta en complemento a 2 necesitamos generar la función siguiente: desbor=c 2⊕c 3 pero no disponemos de ninguno de los dos acarreos de forma externa, puesto que estos acarreos se generan y utilizan internamente en el sumador. Vamos a ver cómo generar estos acarreos. El acarreo c2 lo generamos con un circuito independiente (recordar la generación de acarreo en paralelo). La expresión algebraica para c2 es la siguiente: c 2=a 2 b 2a 1 b1 a 2b2 c 0 a 1b 1 a2 b2 Introduciendo esta expresión algebraica en el programa Boole Deusto, obtenemos el mapa de Karnaugh de la Figura 1 y la siguiente expresión simplificada correspondiente al acarreo c 2=b 2 b1 c0 a 1 b 2 c0 a 1 b 2 b1a 2 b1 c 0a 2 a 1 c0 a 2 a 1 b 1a 2 b2 Figura 1: Mapa de Karnaugh para c2 Para obtener el acarreo c3 introducimos un cero lógico en las entradas A4 y B4 del sumador y la salida SUM4 será igual a lo que valga el acarreo c3 (ver Figura 2) Como la versión de Pspice de evaluación no posee varias de las puertas necesarias se ha implementado los extensores lógicos y el generador de acarreo mediante puertas NAND. Se ha utilizado lo puerta NAND de 8 entradas (componente 7430) y se ha puesto a 1 las entradas de dicho componente no utilizadas. A continuación se presentan los distintos circuitos utilizados así como una simulación en que se puede ver los resultados para todos los casos posibles (verificación). Figura 2: Unidad Aritmético Lógica (ALU) de 3 bits Figura 3: Extensor aritmético Figura 4: Extensor lógico Figura 5: Circuito correspondiente al acarreo c2 Operaciones Lógicas Observamos que en estos valores la variable C3 (el acarreo final) es siempre cero. Figura 6: Resultados operación complemento A Figura 7: Resultados operación AND Figura 8: Resultados operación identidad A Figura 9: Resultados operación OR Operaciones Aritméticas En este caso el acarreo corresponde a las operaciones aritméticas realizadas sobre dos números representados en complemento a 2. Para analizar los valores obtenidos es interesante tener en cuenta el significado de los códigos o combinaciones binarias. Lo reflejamos en la Tabla 2 a continuación: a2 a1 a0 Binario Natural C2 0 0 0 0 0 0 0 1 1 1 0 1 0 2 2 0 1 1 3 3 1 0 0 4 -4 1 0 1 5 -3 1 1 0 6 -2 1 1 1 7 -1 Tabla 2: Equivalente decimal de las combinaciones en binario natural y complemento a 2 Figura 10: Resultados operación decremento A-1 Figura 11: Resultados operación suma aritmética A+B Figura 12: Resultados operación resta A - B Figura 13: Resultados operación incremento A + 1