PREGUNTAS TIPO TEMA 5A : Lenguaje VHDL

Anuncio

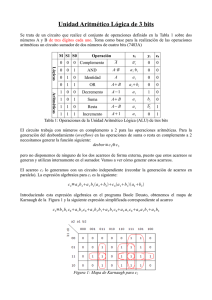

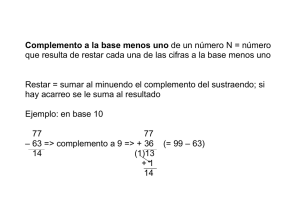

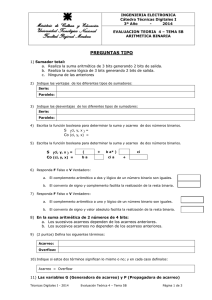

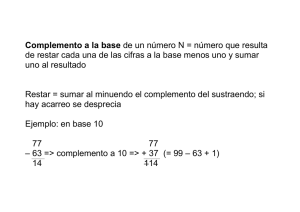

INGENIERIA ELECTRONICA Cátedra Técnicas Digitales I 3º Año 2014 EVALUACION TEORIA 4 – TEMA 5A-5B ARITMETICA BINARIA LENGUAJE VHDL PREGUNTAS TIPO TEMA 5A : Lenguaje VHDL 1) Una con na flecha los conceptos de cada nivel de abstracción en el diseño electrónico ARQUITECTURAL Materialización a nivel eléctrico y geométrico para una determinada tecnología FUNCIONAL Algoritmos y funciones que indican la relación E/S FÍSICO Componentes funcionales interconectados 2) Elija la opción que más adecuada al concepto de METODOLOGÍA DE DISEÑO. a) Es el ordenamiento de los procesos que relacionan la complejidad y abstracción por los que atraviesa el diseño de un Sistema Electrónico. b) Es el ordenamiento de los elementos que permiten seleccionar la Tecnología a usar en la construcción de un Sistema Electrónico. c) Es la selección del lenguaje HDL más conveniente para la síntesis final del Sistema Electrónico. d) Ninguna de las anteriores. 3) Ordene con números, las sig. acciones para un Diseño TOP-DOWN(descendente) - Definir la estructuración de los distintos niveles jerárquicos. - Realizar una descomposición jerárquica definiendo nuevas abstracciones e interrelaciones entre las mismas. - Seleccionar la tecnología. - Definir el nivel de abstracción inicial. - Desarrollar la arquitectura necesaria. 4) Ordene con números, las sig. acciones para un Diseño BOTTON-UP (ascendente) - Definir la estructuración de los distintos niveles jerárquicos. - Realizar una descomposición jerárquica definiendo nuevas abstracciones e interrelaciones entre las mismas. - Seleccionar la tecnología. - Definir el nivel de abstracción inicial. - Desarrollar la arquitectura necesaria. 5) Un lenguaje HDL es propio de las siguientes consideraciones: a) Es un Lenguaje de alto nivel b) Posee una Sintaxis y semántica adecuada para el modelado y descripción de circuitos electrónicos c) Permite descripciones con distintos niveles de abstracción, precisión y estilos de modelado d) Permite la Simulación global del circuito modelado. e) Todas las anteriores d) Ninguna de las anteriores. Técnicas Digitales I - 2014 Evaluación Teórica 4 – Tema 5A-5B Página 1 de 5 6) Marque la o las opciones que considere correctas en referencia a las características generales de un VHDL. a) Permite la utilización de variados tipos de datos b) No permite el control de flujo c) Permite la estructuración del código. d) No permite el desarrollo y utilización de bibliotecas. e) Ninguna de las anteriores 7) Marque la o las opciones que considere correctas en referencia a las características propias de un VHDL. a) Permite un MODELO DE ESTRUCTURA b) No permite MODELO DE CONCURRENCIA c) Permite un MODELO DE TIEMPO d) Ninguna de las anteriores. 8) Una con flechas según corresponda. Modelo de Estructura Modelo de Tiempo Modelo de Concurrencia Sentencias PROCESS, WAIT Sentencias ENTITY, ARCHITECTURE Ciclo de Simulación (estímulo-respuesta) 9) Una con flechas según corresponda para las siguientes Unidades de diseño en VHDL ENTITY con una entidad Selecciona la arquitectura que se asocia CONFIGURATION (interface) Define la visión externa de un dispositivo ARQUITECTURE Define la funcionalidad de la entidad 10) Una con flechas según corresponda para los siguientes estilos descriptivos FLUJO DE DATOS Define la funcionalidad del dispositivo mediante un algoritmo ALGORITMICO Define la funcionalidad del dispositivo mediante ecuaciones ESTRUCTURAL Define los componentes interconectados mediante señales. Técnicas Digitales I - 2014 Evaluación Teórica 4 – Tema 5A-5B Página 2 de 5 TEMA 5B : Aritmética Binaria 1) Sumador total: a. Realiza la suma aritmética de 3 bits generando 2 bits de salida. b. Realiza la suma lógica de 3 bits generando 2 bits de salida. c. Ninguna de las anteriores 2) Indique las ventajas de los diferentes tipos de sumadores: Serie: Paralelo: 3) Indique las desventajas de los diferentes tipos de sumadores: Serie: Paralelo: 4) Escriba la función booleana para determinar la suma y acarreo de dos números binarios. S (ci, y, x ) = Co (ci, y, x) = 5) Escriba la función booleana para determinar la suma y acarreo de dos números binarios. S (ci, y, x ) = Co (ci, y, x) = ( + ba b a* ) ci a ci + 6) Responda F Falso o V Verdadero: a. El complemento aritmético a dos y lógico de un número binario son iguales. b. El convenio de signo y complemento facilita la realización de la resta binaria. 7) Responda F Falso o V Verdadero: a. El complemento aritmético a uno y lógico de un número binario son iguales. b. El convenio de signo y valor absoluto facilita la realización de la resta binaria. 8) En la suma aritmética de 2 números de 4 bits: a. Los sucesivos acarreos dependen de los acarreos anteriores. b. Los sucesivos acarreos no dependen de los acarreos anteriores. 9) (2 puntos) Defina los siguientes términos: Acarreo: Overflow: 10) Indique si estos dos términos significan lo mismo o no; y en cada caso definalos: Acarreo = Overflow 11) Las variables G (Generadora de acarreo) y P (Propagadora de acarreo) a.Dependen del acarreo de entrada al sumador total. b.No dependen del acarreo de entrada al sumador total. 12) Con el convenio de signo/complemento a uno, restando dos números positivos, tenemos Técnicas Digitales I - 2014 Evaluación Teórica 4 – Tema 5A-5B Página 3 de 5 n c. a2 – b2 = a2 + 2 – 1 - b2 : Resultado correcto más un Overflow d. a2 – b2 = a2 + 2 – 1 - b2 : Resultado incorrecto en – 1 más un Overflow. n n a2 – b2 = a2 + 2 – 1 - b2 : Resultado correcto pues se anula 2 con 1. e. f. n n n a2 – b2 = a2 + 2 – 1 - b2 : Resultado incorrecto pues 2 – 1 - b2 es un numero negativo. 13) Con el convenio de signo/complemento a dos, restando dos números positivos, tenemos n a. a2 – b2 = a2 + 2 - b2 : Resultado incorrecto más un Overflow b. a2 – b2 = a2 + 2 c. a2 – b2 = a2 + 2 ceros. d. a2 – b2 = a2 + 2 n n n - b2 : Resultado correcto más un Overflow. - b2 : Resultado correcto pues 2 n es la unidad seguida de n - b2 : Resultado incorrecto pues 2 – b2 es un numero negativo 14) Dibuje el Diagrama en bloques de un Generador de Acarreo 15) Dibuje el diagrama en bloques de un Sumador total de 4 bits 16) En un Sumador Total de 4 bits con acarreo serie a. Los acarreos se obtienen de las salidas de acarreo de los sumadores anteriores, por lo tanto el Tiempo de Suma será aproximadamente 4 veces el Tiempo de Suma de cada sumador total. b. Los acarreos se obtienen de las salidas de acarreo de un generador de acarreo, por lo tanto el Tiempo de Suma será aproximadamente el tiempo de retardo del Generador de acarreo más el Tiempo de Suma de un sumador total c. Ninguna de las anteriores 17) En un Sumador Total de 4 bits con acarreo paralelo a. Los acarreos se obtienen de las salidas de acarreo de los sumadores anteriores, por lo tanto el Tiempo de Suma será aproximadamente 4 veces el Tiempo de Suma de cada sumador total. b. Los acarreos se obtienen de las salidas de acarreo de un generador de carreo, por lo tanto el Tiempo de Suma será aproximadamente el tiempo de retardo del Generador de acarreo más el Tiempo de Suma de un sumador total c. Ninguna de las anteriores 18) Es posible realizar la resta binaria mediante una suma usando el Complemento a 2: a. Sí, pero si se produce acarreo hay que sumárselo al resultado. b. Sí, pero si se produce acarreo hay que despreciarlo. c. No es posible d. Ninguna de las anteriores. 19) Es posible realizar la resta binaria mediante una suma usando el Complemento a 1: a. Sí, pero si se produce acarreo hay que sumárselo al resultado. b. Sí, pero si se produce acarreo hay que despreciarlo. c. No es posible d. Ninguna de las anteriores. 20) Dibuje el diagrama en bloques de un Sumador/Restador de 4 bits usando C2 21) Dibuje el diagrama en bloques de un Sumador/Restador de 4 bits usando C1 22) ¿El rebasamiento (overflow) en los circuitos aritméticos debe tenerse en cuenta? a. Sí, porque es posible que la capacidad del circuito sea superada. b. Sí, pero solamente en la suma c. Sí, pero solamente en la resta. Técnicas Digitales I - 2014 Evaluación Teórica 4 – Tema 5A-5B Página 4 de 5 d. No es necesario ya que se puede utilizar el acarreo más significativo para verificar que la capacidad del circuito aritmético no sea superada. e. Ninguna de las anteriores. 23) El complemento a 10 en aritmética decimal a. Tiene la misma interpretación y aplicación que el complemento a 2 en aritmética binaria. b. No es correcto el planteo del punto a). 24) El complemento a 9 en aritmética decimal a. Tiene la misma interpretación y aplicación que el complemento a 1 en aritmética binaria. b. No es correcto el planteo del punto a). ooo O ooo Técnicas Digitales I - 2014 Evaluación Teórica 4 – Tema 5A-5B Página 5 de 5