Se desea diseñar un sistema para jugar a Piedra, papel o tijera

Anuncio

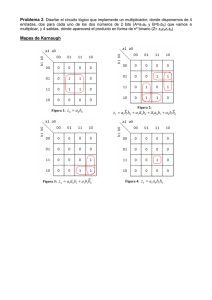

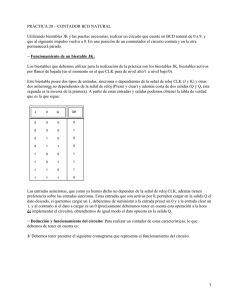

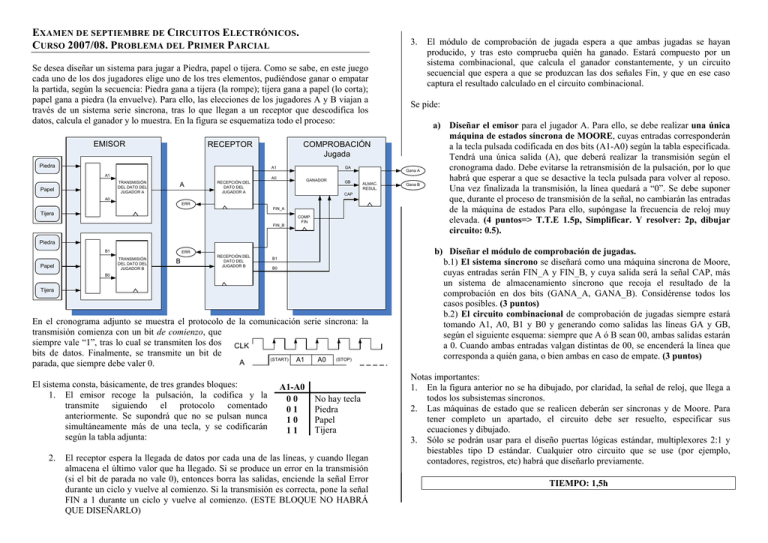

EXAMEN DE SEPTIEMBRE DE CIRCUITOS ELECTRÓNICOS. CURSO 2007/08. PROBLEMA DEL PRIMER PARCIAL 3. Se desea diseñar un sistema para jugar a Piedra, papel o tijera. Como se sabe, en este juego cada uno de los dos jugadores elige uno de los tres elementos, pudiéndose ganar o empatar la partida, según la secuencia: Piedra gana a tijera (la rompe); tijera gana a papel (lo corta); papel gana a piedra (la envuelve). Para ello, las elecciones de los jugadores A y B viajan a través de un sistema serie síncrona, tras lo que llegan a un receptor que descodifica los datos, calcula el ganador y lo muestra. En la figura se esquematiza todo el proceso: EMISOR Piedra GA A1 A1 A0 TRANSMISIÓN DEL DATO DEL JUGADOR A Papel A Se pide: COMPROBACIÓN Jugada RECEPTOR GANADOR RECEPCIÓN DEL DATO DEL JUGADOR A GB Gana A ALMAC. RESUL. CAP A0 ERR FIN_A Tijera FIN_B COMP. FIN El módulo de comprobación de jugada espera a que ambas jugadas se hayan producido, y tras esto comprueba quién ha ganado. Estará compuesto por un sistema combinacional, que calcula el ganador constantemente, y un circuito secuencial que espera a que se produzcan las dos señales Fin, y que en ese caso captura el resultado calculado en el circuito combinacional. Gana B a) Diseñar el emisor para el jugador A. Para ello, se debe realizar una única máquina de estados síncrona de MOORE, cuyas entradas corresponderán a la tecla pulsada codificada en dos bits (A1-A0) según la tabla especificada. Tendrá una única salida (A), que deberá realizar la transmisión según el cronograma dado. Debe evitarse la retransmisión de la pulsación, por lo que habrá que esperar a que se desactive la tecla pulsada para volver al reposo. Una vez finalizada la transmisión, la línea quedará a “0”. Se debe suponer que, durante el proceso de transmisión de la señal, no cambiarán las entradas de la máquina de estados Para ello, supóngase la frecuencia de reloj muy elevada. (4 puntos=> T.T.E 1.5p, Simplificar. Y resolver: 2p, dibujar circuito: 0.5). Piedra B1 ERR TRANSMISIÓN DEL DATO DEL JUGADOR B Papel B RECEPCIÓN DEL DATO DEL JUGADOR B B1 B0 B0 Tijera En el cronograma adjunto se muestra el protocolo de la comunicación serie síncrona: la transmisión comienza con un bit de comienzo, que siempre vale “1”, tras lo cual se transmiten los dos CLK bits de datos. Finalmente, se transmite un bit de (START) (STOP) A1 A0 A parada, que siempre debe valer 0. El sistema consta, básicamente, de tres grandes bloques: 1. El emisor recoge la pulsación, la codifica y la transmite siguiendo el protocolo comentado anteriormente. Se supondrá que no se pulsan nunca simultáneamente más de una tecla, y se codificarán según la tabla adjunta: 2. A1-A0 00 01 10 11 No hay tecla Piedra Papel Tijera El receptor espera la llegada de datos por cada una de las líneas, y cuando llegan almacena el último valor que ha llegado. Si se produce un error en la transmisión (si el bit de parada no vale 0), entonces borra las salidas, enciende la señal Error durante un ciclo y vuelve al comienzo. Si la transmisión es correcta, pone la señal FIN a 1 durante un ciclo y vuelve al comienzo. (ESTE BLOQUE NO HABRÁ QUE DISEÑARLO) b) Diseñar el módulo de comprobación de jugadas. b.1) El sistema síncrono se diseñará como una máquina síncrona de Moore, cuyas entradas serán FIN_A y FIN_B, y cuya salida será la señal CAP, más un sistema de almacenamiento síncrono que recoja el resultado de la comprobación en dos bits (GANA_A, GANA_B). Considérense todos los casos posibles. (3 puntos) b.2) El circuito combinacional de comprobación de jugadas siempre estará tomando A1, A0, B1 y B0 y generando como salidas las líneas GA y GB, según el siguiente esquema: siempre que A ó B sean 00, ambas salidas estarán a 0. Cuando ambas entradas valgan distintas de 00, se encenderá la línea que corresponda a quién gana, o bien ambas en caso de empate. (3 puntos) Notas importantes: 1. En la figura anterior no se ha dibujado, por claridad, la señal de reloj, que llega a todos los subsistemas síncronos. 2. Las máquinas de estado que se realicen deberán ser síncronas y de Moore. Para tener completo un apartado, el circuito debe ser resuelto, especificar sus ecuaciones y dibujado. 3. Sólo se podrán usar para el diseño puertas lógicas estándar, multiplexores 2:1 y biestables tipo D estándar. Cualquier otro circuito que se use (por ejemplo, contadores, registros, etc) habrá que diseñarlo previamente. TIEMPO: 1,5h EXAMEN DE SEPTIEMBRE DE CIRCUITOS ELECTRÓNICOS. CURSO 2007/08. SOLUCIÓN AL PROBLEMA DEL PRIMER PARCIAL Para resolver el primer apartado, nos exigen que se realice una máquina de estados síncrona de Moore. Realmente, no es la solución más sencilla, pero es la que nos piden. Para ello, lo primero es tener claro los diferentes estados posibles. Necesitamos que la salida, una vez se activen las entradas (o sea cuando valgan cualquier cosa distinta de 00) valga 1 durante un ciclo de reloj (bit de Start), tras lo cual valdrá A1 y A0. Finalmente, debe quedarse a 0 hasta que vuelva al reposo (entradas en 00). Un primer esquema de los estados, transiciones y valor de la salida sería el siguiente: En el esquema se representa que, una vez que A1A0 es distinto de 00, paso al estado 1, en el que la salida valdrá 1. Desde ahí, dependiendo de lo que valgan las entradas, paso a los estados 2, 4 ó 6. En esos estados transmito el valor de A1, tras lo cual transmito A0 en los estados 3, 5 y 7. Finalmente, llego al estado 8, en el que esperaré a que se acabe la pulsación (A1A0=00), momento en el que volveré al estado 0. 0 A=0 A1A0=00 A1A0? 00 1 A=0 A1A0=10 A1A0=01 A1A0=11 Es importante notar que nos dicen que las entradas no cambian durante el proceso. Esto significa que una vez estoy en el estado 2, por ejemplo, las entradas seguirán siendo 01 hasta que valgan 00 al final del ciclo. Esto es muy importante para tratar de simplificar el sistema, que de otra forma necesitaría 4 biestables (9 estados). 2 A=0 A1A0=11 A1A0=01 3 A=1 Veamos cómo queda la tabla de transición de estados: A1A0=10 7 A=0 5 A=1 A1A0=01 A1-A0 Estado 00 01 11 10 A 0 (0) 1 1 1 0 1 -2 4 6 1 2 -3 -- -- 0 3 -8 -- -- 1 4 -- -5 -- 1 5 -- -8 -- 1 6 -- -- -7 1 7 -- -- -8 0 8 0 (8) (8) (8) 0 6 A=1 4 A=1 A1A0=11 A1A0=10 8 A=0 A1A0=00 A1A0?00 Para poder simplificar la tabla, debemos ver qué estados tienen la misma salida, y cuáles pueden ser pseudo-equivalentes. Para ello realizaríamos la tabla de inferencias, de la que se obtienen las siguientes pseudoequivalencias: 7-8, 7-2, 6-5, 6-4, 6-3, 5-3, 4-3 Con estas pseudo-equivalencias se pueden eliminar en total 3 estados. Elegiremos de entre ellas las siguientes: 2-7, 3-5, 4-6 Una vez elegidas tres de ellas, se ve que las demás no se pueden usar (por ejemplo, 7-8 ya no es compatible con 2-7, porque 2 y 8 no son pseudoequivalentes, o 4-3 tampoco porque no es compatible con 3-5). Con esta simplificación, la tabla de transición simplificada queda como: A1-A0 Estado 00 01 11 10 A 0 (0) 1 1 1 0 1 -2 4 4 1 2 -3 -8 0 3 -8 8 -- 1 4 -- -3 2 1 8 0 (8) (8) (8) 0 Con esta tabla simplificada, con sólo 6 estados, observo que necesitaré únicamente 3 biestables, lo que simplifica tremendamente el problema. Para codificar los estados, puedo usar una codificación “estándar” (por ejemplo, su número binario tal cual) o puedo ser un poco más astuto, y codificar para que la salida sea uno de los bits de estado. Haremos esto segundo, usando como codificación de los estados la siguiente: Estado 0 1 2 3 4 8 Q2-Q1-Q0 0-0-0 0-0-1 0-1-0 0-1-1 1-0-1 1-0-0 De esta manera, conseguimos que la salida A sea igual a Q0, evitando el diseño del circuito combinacional de salida. Una vez hecha la asignación de estados en la tabla simplificada, se procede a realizar la Tabla de Excitación de los biestables, esto es la tabla de verdad del circuito combinacional de entrada, que calcula las entradas de los biestables en función del estado (sus salidas) y de las entradas del circuito: Q2 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 Q1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 Q0 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 A1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 A0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 D2 0 0 0 0 -0 1 1 -0 -1 -1 1 ---0 0 0 1 1 1 D1 0 0 0 0 -1 0 0 -1 -0 -0 0 ---1 1 0 0 0 0 D0 0 1 1 1 -0 1 1 -1 -0 -0 0 ---1 0 0 0 0 0 Una vez especificada la tabla de excitaciones, sólo queda resolver las ecuaciones de cada bit en función de las entradas del circuito combinacional de entrada (Q2, Q1, Q0 Q1 y A0): Resolvemos por Karnaugh, separando en dos tablas de 4 entradas según el valor de Q2: Q2=0 A1-A0 00 01 11 10 Q1-Q0 00 0 0 0 0 01 -- 0 1 1 11 -- 1 1 -10 -- 0 -- 1 01 11 10 1 1 1 -- 0 0 -- -- --- -- -- D2=Q1·Q0+/Q2·Q0·A1+Q1·A1+Q2·/Q0·A1+Q2·/Q0·A0 Q2=0 A1-A0 00 01 11 10 Q1-Q0 00 0 0 0 0 01 -- 1 0 0 11 -- 0 0 -10 -- 1 -- 0 D1=Q2·Q0+/Q1·Q0·/A1+Q1·/Q0·/A1 Q2=0 A1-A0 Q1-Q0 00 01 11 10 00 0 1 1 1 01 -- 0 1 1 11 -- 0 0 -10 -- 1 -- 0 Q2=1 A1-A0 Q1-Q0 00 00 0 01 -11 -10 -- Q2=1 A1-A0 Q1-Q0 00 00 0 01 -11 -10 -- 01 11 10 0 0 0 -- 1 0 -- -- --- -- -- D0=/Q2·/Q0·A0+/Q2·/Q1·A1+Q2·Q0·A0 Q2=1 A1-A0 Q1-Q0 00 00 0 01 -11 -10 -- 01 11 10 0 0 0 -- 1 1 -- -- --- -- -- Con esto quueda resueltaa la máquina de estados del d primer ap partado, dadoo que el circuuito combinaacional de sallida es simplemeente la expreesión: A=Q0. En la imageen adjunta see muestra el circuito. En la siguieente imagen se s observa unna simulacióón del circuitto en el que se s envían succesivamente 01, 10 y 11. SEPT0 08.CIR d(CLK) Sta art 0 1 S Start 1 0 Stop Stop Start 1 1 Stop d(A) hex(q2, q1, q Q0) 0 1 2 3 4 0 1 5 2 4 0 1 5 3 4 0 d(A1) d(A0) (A1-A0=10) 11) (A1-A0=1 (A1-A0=01) 0.000m 2.000m 4.000m 6.000m m T 8.000m 10.000m Para el segundo apartado del problema, necesitamos realizar dos sistemas. Un primer sistema síncrono, que almacene el resultado una vez se produzca, y otro sistema combinacional que calcule cuál de los dos ha ganado o si ha habido empate. El sistema secuencial estará formado por una pequeña máquina de estados que controlará la llegada de las dos jugadas, y un registro de captura que almacenará la salida del circuito combinacional. La máquina de estados tendrá como entradas las señales FIN_A y FIN_B, y como salida la señal FIN. Es necesaria esta máquina porque las señales duran un solo ciclo de reloj y tengo que saber que han llegado las dos. La tabla de transición de estados en este caso será: FIN_A-FIN_B Estado 00 01 11 10 FIN 0 (0) 1 2 3 0 1 (1) (1) 3 3 0 2 (2) 3 (2) 3 0 3 0 0 0 -1 A la hora de realizar la tabla, se han tenido en cuenta los siguientes supuestos: • puede ser (aunque es poco probable, no es imposible), que lleguen a la vez las dos señales de fin, si ambos jugadores pulsan en el mismo ciclo de reloj. • Una vez que estoy en el estado 1 (llegó fin_a), al siguiente ciclo de reloj seguro que está desactivado, por lo que probablemente el siguiente valor de entradas será el 00, en cuyo caso permanezco en 1 hasta que llegue 10. Pero si mientras espero llega un nuevo FIN_A (el jugador A cambia la jugada), permanezco en 1. Esto hace que tampoco sea imposible la combinación 01 en el estado 1. • Análogamente, en el estado 2 tampoco resulta imposible la combinación 10, aunque lo más normal será esperar en 2 hasta que se produzca un 01. De la misma forma, también es posible (aunque altamente improbable, pero no imposible) que lleguen ahora dos señales de FIN a la vez. • Una vez estoy en el estado 3 (ya han llegado las dos señales), de lo único que estoy seguro es que las entradas no pueden valer 11, ya que una de ellas acaba de ser 1 (si no, no habría llegado a 3). En cualquier otro caso, iré al estado 0. Una vez realizada la tabla de estados, y codificando cada estado con su valor binario, la tabla de excitaciones queda: Q1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 Q0 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 FA 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 FB D1 D0 0 0 0 1 0 1 1 1 1 0 1 0 0 0 1 1 0 1 1 1 1 0 1 1 0 1 0 1 1 1 1 1 1 0 1 0 0 0 0 1 0 0 1 0 0 0 --- Y a partir de esta tabla, se construyen las tablas de Karnaugh para cada una de las dos entradas de los biestables, D1 y D0, como: D1 FA-FB 00 01 11 10 Q1-Q0 00 0 0 1 1 01 0 0 1 1 11 0 0 -- 0 10 1 1 1 1 D1= Q1·/Q0 + /Q1·FIN_A D0 FA-FB Q1-Q0 00 01 11 10 ... 00 0 1 1 0 01 1 1 1 1 11 0 0 -- 0 10 0 1 1 0 D0= /Q0·FIN_B + /Q1·Q0 Como cabía esperar, la solución es “simétrica”, pudiendo reemplazarse FIN_A por FIN_B cambiando Q1 por Q0. Finalmente, el circuito combinacional de salida queda reducido al producto de los dos bits de estado, FIN= Q1·Q0, por lo que el circuito completo queda como: Para redonddear este apaartado, solo nos n queda reaalizar el circu uito que capttura y almacena el resultado. Éste esttará formado por dos biestabbles que almaacenarán el resultado r del circuito com mbinacional: Mien ntras la señall FIN valga 00, cada biestaable mantenddrá el vaalor anterior, que corresponderá a la jugada anteriior. Cuan ndo FIN sea 1, los valorees de GA y GB G se almaacenan en el registro corrrespondiente. Por último, queda realizzar un circuitto combinaciional que resuelva el ganaador de la juugada. Para ello, las entraadas serán A1, A0, A B1 y B0, representanddo la eleccióón de cada jugador. Se pidde que GA y GB representen cuál de los dos ha ganaado, siendo 00 0 si cualquieer entrada ess 00 (no ha ju ugado todavíía uno de loss dos jugadorres) y siendoo 11 cuando se produzca p un empate. e Con esto, y aplicando laas reglas del juego j piedraa-papel-tijeraa, se obtiene la l tabla de veerdad: Tras lo cuall, realizamoss las tablas dee Karnaugh para p las salid das del circuiito combinaccional, GA y GB: A1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 A0 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 B1 B 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 B0 GA A GB 0 0 0 Espera 1 0 0 Espera Espera 1 0 0 Espera 0 0 0 Espera 0 0 0 1 1 1 Empate 1 1 0 Piedra > Tijeraa 0 0 1 Pieedra < Papeel 0 0 0 Espera 1 1 0 Paapel > Piedraa 1 0 1 Paapel < Tijeraa 0 1 0 Empate Espera 0 0 0 1 0 1 Tij ijera < Piedraa 1 1 1 Empate 0 1 0 Tiijera > Papell GA B1-B0 A1--A0 00 00 0 01 0 11 0 10 0 01 11 10 0 0 0 1 1 0 0 1 1 1 0 1 GA=/A1·/A0·B0 A1·/A0··/B1·B0 GB B1-B0 00 A1-A0 A 00 0 01 0 11 0 10 0 + A1·A0·B1 1+A1·B1·/B B0+ 01 11 10 0 0 0 1 0 1 1 1 0 0 1 1 ·A0 GB=/B1·/B B0·A0 + B11·B0·A1+B11·A1·/A0+ B1·/B0·/A1 B Se puede comprobar fáácilmente tam mbién la sim metría de la solución, enn la que cam mbiando los A por los B, la salida GA y GB son inteercambiabless, como es lóógico. El circcuito quedaráá: Con lo que acaba el probblema.