S - RUA

Anuncio

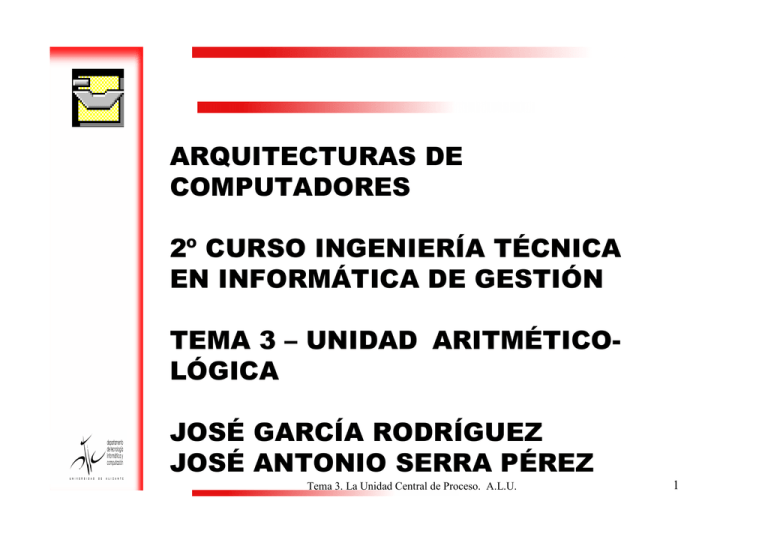

ARQUITECTURAS DE COMPUTADORES 2º CURSO INGENIERÍA TÉCNICA EN INFORMÁTICA DE GESTIÓN TEMA 3 – UNIDAD ARITMÉTICOLÓGICA JOSÉ GARCÍA RODRÍGUEZ JOSÉ ANTONIO SERRA PÉREZ Tema 3. La Unidad Central de Proceso. A.L.U. 1 La Unidad Aritmética y Lógica La ALU Introducción Operaciones Lógicas La suma y la resta La multiplicación Sumador con propagación de acarreo (CPA) Circuito sumador-restador Desbordamiento Sumadores con anticipación de acrreo (CLA) Multiplicación binaria sin signo Multiplicación binaria con signo Algoritmo de Booth La división Conclusiones Tema 3. La Unidad Central de Proceso. A.L.U. 2 Introducción Introducción B A TEMP C D E ALU Z C O Operador aritmético y lógico (uno o varios) El Acumulador Uno o varios registros temporales Indicadores de resultado Acarreo (C) Negativo (N) Desbordamiento (O o V) Cero (Z) Tema 3. La Unidad Central de Proceso. A.L.U. 3 Operaciones lógicas Operaciones Lógicas Fáciles de implementar ⇒ Correspondencia directa con Hardware. Puertas lógicas AND, OR, OR-EXCLUSIVA, INVERSORES,... Operación A 00 B Resultado 01 10 Tema 3. La Unidad Central de Proceso. A.L.U. 4 La suma y la resta Semisumador Binario (H.A.) Semisumador Entradas Salidas X Y S C S = X ⋅Y + X ⋅Y = X ⊕ Y 0 0 0 0 C = X ⋅Y 0 1 1 0 1 0 1 0 1 1 0 1 H.A. S A B H.A. C A C B S Tema 3. La Unidad Central de Proceso. A.L.U. 5 Sumador completo (F.A.) Entradas La suma y la resta Cin A S B F.A. Cout Salidas A B Cin S Cout 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1 S = A ⋅ B ⋅ Cin + A ⋅ B ⋅ Cin + A ⋅ B ⋅ Cin + A ⋅ B ⋅ Cin Cout = A ⋅ B + A ⋅ Cin + B ⋅ Cin S = ( A ⊕ B ) ⊕ Cin Cout = AB + Cin ( A ⊕ B ) Tema 3. La Unidad Central de Proceso. A.L.U. 6 Sumador completo (F.A.) La suma y la resta • Con semi-sumadores (H.A.) F.A. H.A. H.A. A S S B C C S Cout Cin Tema 3. La Unidad Central de Proceso. A.L.U. 7 Sumador completo (F.A.) La suma y la resta • Con puertas Tema 3. La Unidad Central de Proceso. A.L.U. 8 Sumador con propagación de acarreo La suma y la resta Para sumar dos números de n bits se necesita colocar en cascada n sumadores completos. El acarreo se propaga de una etapa a la siguiente: Sumador con Propagación de Acarreo (Carry Propagated Adder) B3 C4 FA S3 A3 B2 C2 FA S2 A2 B1 C2 FA A1 B0 C1 S1 Tema 3. La Unidad Central de Proceso. A.L.U. FA A0 C0 S0 9 Sumador con propagación de acarreo La suma y la resta Sumadores construidos con puertas lógicas a partir de la expresión: S = A ⋅ B ⋅ Cin + A ⋅ B ⋅ Cin + A ⋅ B ⋅ Cin + A ⋅ B ⋅ Cin Cout = A ⋅ B + A ⋅ Cin + B ⋅ Cin B3 A3 B2 A2 C2 C4 FA FA FA A0 C0 FA 2T 7T S2 B0 C1 4T 9T S3 A1 C2 6T 8T B1 5T S1 Tema 3. La Unidad Central de Proceso. A.L.U. 3T S0 10 Sumador con propagación de acarreo La suma y la resta Sumadores completos construidos con semisumadores: A S B Cout Cin B3 A3 B2 A2 C2 C4 FA FA 8T S3 A1 C2 7T 9T B1 A0 C1 FA C0 FA 5T 3T 6T S2 B0 4T S1 2T S0 Tiempo _ Total = (2 ⋅ n + 1)T Tema 3. La Unidad Central de Proceso. A.L.U. 11 Sumador 74ls83 La suma y la resta Sumadores integrado Tema 3. La Unidad Central de Proceso. A.L.U. 12 Sumador 74ls83 La suma y la resta Tema 3. La Unidad Central de Proceso. A.L.U. 13 Circuito restador La suma y la resta Suponer que se trabaja con números expresados en complemento a 2. A - B = A + (C1(B) + 1) B3 A3 B2 C2 C4 A2 B1 A1 C2 B0 C1 FA FA FA FA S3 S2 S1 S0 Tema 3. La Unidad Central de Proceso. A.L.U. A0 C0=1 14 Circuito Sumador-Restador La suma y la resta R/S Bi Entrada al FA 0 0 0 0 1 1 1 0 1 1 1 0 A3 B3 B2 Tiempo _ Total = 2(n + 1)T A2 B1 A1 A0 B0 R/S C4 FA S3 C2 FA S2 C2 FA C1 S1 Tema 3. La Unidad Central de Proceso. A.L.U. FA C0 S0 15 Detección de desbordamiento La suma y la resta Sumador-Restador en complemento a 2 con detección de desbordamiento. A3 B3 B2 A2 A1 B1 A0 B0 R/S FA C4 S3 C3 FA S2 C2 FA C1 S1 FA C0 S0 V Tema 3. La Unidad Central de Proceso. A.L.U. 16 Detección de desbordamiento La suma y la resta 1. Caso suma de S C4 C3 0 1 0 0 1 dos positivos 2. Caso suma de S C4 C3 1 0 1 1 0 dos negativos C2 C1 1 1 1 1 1 1 1 1 C2 C1 1 1 0 0 0 1 1 0 1 1 0 1 1 0 OV OV Tema 3. La Unidad Central de Proceso. A.L.U. 17 Sumador con anticipación de acarreo La suma y la resta Carry Lookahead Adder (CLA) Suponer A y B números de 4 bits Señal generadora de acarreo : Gi = ai ⋅ bi Señal propagadora de acarreo: Pi = ai ⊕ bi Pi = ai + b i Acarreo de la etapa i: Ci = Gi + Pi ⋅ Ci − 1 Particularizando para A y B: C 0 = G 0 + P0 ⋅ C − 1 C 1 = G 1 + P1 ⋅ C 0 C 2 = G2 + P2 ⋅ C1 C 3 = G3 + P3 ⋅ C 2 Tema 3. La Unidad Central de Proceso. A.L.U. 18 Sumador con anticipación de acarreo La suma y la resta Desarrollando las expresiones y poniéndolas en función de C-1: C 0 = G0 + P0 ⋅ C − 1 C 1 = G 1 + P1 ⋅ G 0 + P1 ⋅ P0 ⋅ C − 1 C 2 = G 2 + P 2 ⋅ G 1 + P 2 ⋅ P1 ⋅ G 0 + P 2 ⋅ P1 ⋅ P0 ⋅ C − 1 C 3 = G 3 + P 3 ⋅ G 2 + P 3 ⋅ P 2 ⋅ G 1 + P 3 ⋅ P 2 ⋅ P1 ⋅ G 0 + P 3 ⋅ P 2 ⋅ P1 ⋅ P0 ⋅ C − 1 Todos los acarreos dependen de ai y bi. Estas expresiones se resuelven como suma de productos. Tres niveles de puertas lógicas para obtener cada uno de los acarreos. Tema 3. La Unidad Central de Proceso. A.L.U. 19 Sumador con anticipación de acarreo La suma y la resta a3 b3 ∑ c2 g3 p3 ∑ c1 ∑ S2 a0 b0 c0 g1 p1 g2 p2 S3 a1 b1 a2 b2 ∑ c-1 g0 p0 S1 S0 c3 Generador de acarreo anticipado Tema 3. La Unidad Central de Proceso. A.L.U. 20 Sumador con anticipación de acarreo b3 a3 La suma y la resta ∑ g3 p3 4T 1T 1T S3 c3 a2 b2 3T ∑ 3T c2 a1 c1 b1 4T 1T 1T S2 3T ∑ g1 p1 g2 p2 a0 ∑ c0 4T 1T 1T S1 b0 c-1 g0 p0 4T 1T 1T S 0 Generador de acarreo anticipado 3T F.A. 4T ai bi H.A. Ci-1 H.A. 1T Si ci Sumadores construidos con semisumadores 3T Tema 3. La Unidad Central de Proceso. A.L.U. 21 Ejemplo (Sumador CLA de 8 bits) La suma y la resta a7 b7 ∑ c6 g7 p7 S7 c7 a5 b5 a6 b6 ∑ c5 g6 p6 S6 ∑ c4 g5 p5 S5 a3 b3 a4 b4 ∑ g4 p4 c3 S4 ∑ a1 b1 a2 b2 c2 g3 p3 S3 Generador de acarreo anticipado ∑ c1 g2 p2 S2 ∑ a0 b0 c0 g1 p1 S1 ∑ g0 p0 Generador de acarreo anticipado Calcular los retardos en este CLA suponiendo que los sumadores se construyen con semisumadores. Comparar el resultado con el de un sumador CPA de 8 bits. Tema 3. La Unidad Central de Proceso. A.L.U. 22 c-1 S0 La multiplicación La multiplicación Algoritmo de sumas y desplazamientos Si multiplicando de n bits y multiplicador de m bits, entonces el producto tendrá una longitud de n+m bits. Multiplicación binaria: sencilla ya que hay que multiplicar por 1 o por 0. Multiplicando 5 3 2 Multiplicador 4 3 1 5 3 2 6 Producto 1 5 9 2 1 2 8 2 2 9 2 9 Tema 3. La Unidad Central de Proceso. A.L.U. 2 23 Multiplicación binaria sin signo Repetir n veces La multiplicación Si el bit 0 del multiplicador=1 entonces Sumar el multiplicando a la mitad izquierda del producto y colocar el resultado en la mitad izquierda del producto. Fin entonces Versión preliminar Desplazar 1 bit a la derecha el registro producto Desplazar 1 bit a la derecha el registro multiplicador Fin repetir Despl. derecha Multiplicando n bits Multiplicador n bits Suma ALU Despl. derecha C Control Producto 2n bits Escribir Tema 3. La Unidad Central de Proceso. A.L.U. 24 Multiplicación binaria sin signo La multiplicación Multiplicando 1 0 1 1 Multiplicador 1 1 0 1 1 0 1 1 0 0 0 0 1 0 1 1 1 0 1 1 0 0 0 1 Producto 1 1 1 Versión preliminar 1 Despl. derecha Multiplicando n bits Multiplicador n bits Suma ALU Despl. derecha C Control Producto 2n bits Escribir Tema 3. La Unidad Central de Proceso. A.L.U. 25 Multiplicación binaria sin signo Repetir n veces La multiplicación Si el bit 0 del registro producto=1 entonces Sumar el multiplicando a la mitad izquierda del producto y colocar el resultado en la mitad izquierda del producto. Fin entonces Versión final Desplazar 1 bit a la derecha el registro producto Fin repetir Multiplicando n bits Suma ALU Despl. derecha C Producto Control Multiplicador 2n bits Escribir Tema 3. La Unidad Central de Proceso. A.L.U. 26 Multiplicación binaria sin signo La multiplicación 1010 Multiplicando 10(d Iteración 0 valores iniciales Suma ALU Despl. derecha 0 0000 0 1 0 Control 1 Escribir Producto Multiplicador 5(d Tema 3. La Unidad Central de Proceso. A.L.U. 27 Multiplicación binaria sin signo La multiplicación 1010 Multiplicando Iteración 1 suma P y Mando Suma ALU Despl. derecha 0 1 0 1 0 0 1 0 Control 1 Escribir Producto Multiplicador Tema 3. La Unidad Central de Proceso. A.L.U. 28 Multiplicación binaria sin signo La multiplicación 1010 Multiplicando Iteración 1 despla. P dcha. Suma ALU Despl. derecha 0 0 1 0 1 0 0 1 Control 0 Escribir Producto Multiplicador Tema 3. La Unidad Central de Proceso. A.L.U. 29 Multiplicación binaria sin signo La multiplicación 1010 Multiplicando Iteración 2 despla. P dcha Suma ALU Despl. derecha 0 0 0 1 0 1 0 0 Control 1 Escribir Producto Multiplicador Tema 3. La Unidad Central de Proceso. A.L.U. 30 Multiplicación binaria sin signo La multiplicación 1010 Multiplicando Iteración 3 suma P y Mando Suma ALU Despl. derecha 0 1 1 0 0 1 0 0 Control 1 Escribir Producto Multiplicador Tema 3. La Unidad Central de Proceso. A.L.U. 31 Multiplicación binaria sin signo La multiplicación 1010 Multiplicando Iteración 3 despla. P dcha. Suma ALU Despl. derecha 0 0 1 1 0 0 1 0 Control 0 Escribir Producto Multiplicador Tema 3. La Unidad Central de Proceso. A.L.U. 32 Multiplicación binaria sin signo La multiplicación 1010 Multiplicando Iteración 4 despla. P dcha. Suma ALU Despl. derecha 0 0 0 1 1 0 0 1 Control 0 Escribir Producto 50(d Multiplicador Tema 3. La Unidad Central de Proceso. A.L.U. 33 Multiplicación binaria sin signo Multiplicando = 1010 La multiplicación Multiplicador = 0101 Producto Multiplicando Acción 0000 0101 1010 Valores iniciales 0 1010 0101 1010 Sumar prod. y multiplicando 1 0101 0010 1010 Desplazar prod. a derecha 1 0010 1001 1010 Despl. producto 1 bit a la derecha 2 1100 1001 1010 Sumar prod. y multiplicando 3 0110 0100 1010 Despl. producto 1 bit a la derecha 3 0011 0010 1010 Despl. producto 1 bit a la derecha 4 Tema 3. La Unidad Central de Proceso. A.L.U. Iteración 34 Multiplicación rápida La multiplicación Tema 3. La Unidad Central de Proceso. A.L.U. 35 Multiplicación binaria con signo La multiplicación Supongamos números expresados en Ca2 A = 1010 y B = 0011 Apliquemos algoritmo de sumas y desplazamientos 1 0 1 0 1 0 1 0 x 0 0 1 1 x 0 0 1 1 1 0 1 0 1 1 1 1 1 0 1 0 1 1 1 1 0 1 0 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 0 1 1 1 0 1 1 1 0 Versión errónea Versión correcta Tema 3. La Unidad Central de Proceso. A.L.U. 36 Algoritmo de Booth La multiplicación Supongamos Multiplicando = 2 y Multiplicador = 7 (en binario 0010 x 0111) Booth expresó 7 = 8 - 1 y sustituyo el multiplicador por esta descomposición: 0111 = 1000 - 0001 = +100-1 0 0 1 0 Multiplicando x +1 0 0 -1 Multiplicador según A. Booth 1 0 Restamos el multiplciadndo 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 1 2 despl. (2 ceros en el multiplicador) Sumamos el multiplicando 1 1 0 Tema 3. La Unidad Central de Proceso. A.L.U. 37 Algoritmo de Booth La multiplicación Bit actual Bit a la izquierda Sustitución 0 0 0 0 1 -1 (transición hacia negativoo) 1 0 +1 (transición hacia positivo) 1 1 0 (no hay transición) (no hay transición) Ejemplo: Multiplicando = 11101110 y Multiplicador = 01111010 Recodificación del multiplicador según Booth = +1000-1+1-10 0 0 1 0 1 1 0 0 1 0 1 1 0 0 1 0 1 1 0 0 1 0 1 1 0 0 1 0 0 0 0 0 1 0 1 1 0 0 1 0 1 1 x 0 0 1 0 1 1 1 +1 0 0 1 1 0 0 1 0 0 0 0 0 0 1 1 0 0 1 1 0 0 1 0 0 0 0 1 1 0 0 Tema 3. La Unidad Central de Proceso. A.L.U. 1 -1 0 0 1 0 1 +1 0 1 0 1 0 -1 0 0 0 0 1 1 0 0 38 Algoritmo de Booth Inicialmente q-1=0 La multiplicación Repetir n veces Si q0 = 1 y q-1 = 0 entonces Productoh = productoh - Multiplicando Si q0 = 0 y q-1=1 entonces Productoh = Productoh + Multiplicando Desplazamiento aritmético a la derecha de Producto y q-1 Fin repetir. Multiplicando n bits Suma/Resta ALU Despl. derecha Producto Multiplicador q0 q-1 Control 2n bits Tema 3. La Unidad Central de Proceso. A.L.U. 39 Algoritmo de Booth Multiplicando = 1010 Multiplicador = 1110 La multiplicación Multiplicando Producto q-1 Acción 1010 0000 1110 0 Valores iniciales 0 1010 0000 1110 0 00 → Ninguna operación 1 1010 0000 0111 0 Desplazamiento dcha. 1 1010 0110 0111 0 10 → Resta 2 1010 0011 0011 1 Desplazamiento dcha. 2 1010 0011 0011 1 11 → Ninguna operación 3 1010 0001 1001 1 Desplazamiento dcha 3 1010 0001 1001 1 11 → Ninguna operación 4 1010 0000 1100 1 Desplazamiento dcha. 4 Tema 3. La Unidad Central de Proceso. A.L.U. Iteración 40 La división La división La división la podemos expresar como: Dividendo = Cociente x Divisor + Resto El resto es más pequeño que el divisor. Hay que reservar el doble de espacio para el dividendo. Supondemos operandos positivos. Dividendo → 10010011 1011 ←Divisor 10010 01101 ←Cociente 1011 001110 1011 001111 1011 0100 ←Resto Tema 3. La Unidad Central de Proceso. A.L.U. 41 Algoritmo con restauración La división Repetir n veces Desplazar el Dividendo a la izquierda Dividendoh = Dividendoh - Divisor Si Dividendoh < 0 entonces (no cabe) q0=0 Dividendoh = Dividendoh + Divisor (restaurar) Sino q0=1 Fin Si Divisor Fin Repetir n bits Suma/Resta ALU Despl. izquierda Dividendo Cociente q0 Control Resto 2n bits Tema 3. La Unidad Central de Proceso. A.L.U. 42 Algoritmo con restauración La división Dividendo Divisor 0101 0011 0110 Valores iniciales 0 1010 011_ 0110 Desplazar un bit a izquierda 1 0100 011_ 0110 Restar 1 0100 0111 0110 Dividendoh > 0 ⇒ q0 = 1 1 1000 111_ 0110 Desplazar un bit a izquierda 2 0010 111_ 0110 Dividendoh - Divisor (Restar) 2 0010 1111 0110 Dividendoh > 0 ⇒ q0 = 1 2 0101 111_ 0110 Desplazar un bit a izquierda 3 1111 111_ 0110 Dividendoh - Divisor (Restar) 3 1111 1110 0110 Dividendoh <= 0 ⇒ q0 = 0 3 0101 1110 0110 Dividendoh + Divisor (Restaurar) 3 1011 110_ 0110 Desplazar un bit a izquierda 4 0101 110_ 0110 Dividendoh - Divisor (Restar) 4 0101 1101 0110 Dividendoh > 0 ⇒ q0 = 1 4 ↑ Acción Iteración ↑ Resto Cociente Tema 3. La Unidad Central de Proceso. A.L.U. 43 Algoritmo sin restauración La división Dividendoh = Dividendoh - Divisor Repetir n veces Si Dividendoh < 0 entonces Desplazar el Dividendo a la izquierda Dividendoh = Dividendoh + Divisor Sino Desplazar el Dividendo a la izquierda Dividendoh = Dividendoh - Divisor Fin Si Si Dividendoh < 0 entonces q0=0 Sino q0=1 Fin Si Fin Repetir Divisor n bits ALU Suma/Resta Despl. izquierda Dividendo Resto Cociente 2n bits Tema 3. La Unidad Central de Proceso. A.L.U. q0 Contro l 44 Algoritmo sin restauración Dividendo Divisor Acción Iteración 0000 0111 0010 Valores iniciales 0 1110 0111 0010 Dividendoh - Divisor 0 1100 111_ 0010 Dividendoh < 0 ⇒ Desplazar Izda 1 1110 111_ 0010 Dividendoh + Divisor 1 1110 1110 0010 Dividendoh < 0 ⇒ q0 = 0 1 1101 110_ 0010 Dividendoh < 0 ⇒ Desplazar Izda 2 1111 110_ 0010 Dividendoh + Divisor 2 1111 1100 0010 Dividendoh < 0 ⇒ q0 = 0 2 1111 100_ 0010 Dividendoh < 0 ⇒ Desplazar Izda 3 0001 100_ 0010 Dividendoh + Divisor 3 0001 1001 0010 Dividendoh >= 0 q0 = 1 3 0011 001_ 0010 Dividendoh > 0 ⇒ Desplazar Izda 4 0001 001_ 0010 Dividendoh - Divisor 4 0001 0011 0010 Dividendoh > 0 ⇒ q0 = 1 4 La división ↑ ↑ Resto Cociente Tema 3. La Unidad Central de Proceso. A.L.U. 45 Conclusiones Conclusiones Sumadores Multiplicación Problemática temporal de los Sumadores con Propagación de Acarreo (CPA), especialmente si n elevado. Los Sumadores con anticipación de acarreo (CLA) mejoran el tiempo de respuesta de los sumadores. Problemática de la multiplicación de números con signo. El algoritmo de Booth permite multiplicar números en Ca2 y en algunos casos reduce el números de operaciones si aparecen cadenas de 1’s o 0’s en el multiplicador. La División Algoritmo para la división con restauración para números positivos. Si números negativos, entonces tratamiento previo del signo, y en función de éste se obtiene el signo del resultado. Tema 3. La Unidad Central de Proceso. A.L.U. 46