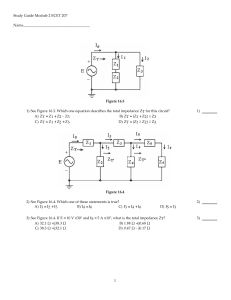

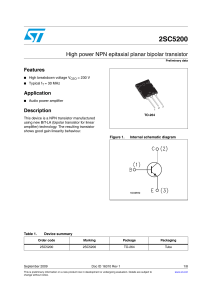

See discussions, stats, and author profiles for this publication at: https://www.researchgate.net/publication/304369015 A novel DC-DC multilevel SEPIC converter for PEMFC systems Article in International Journal of Hydrogen Energy · June 2016 DOI: 10.1016/j.ijhydene.2016.06.042 CITATIONS READS 34 675 7 authors, including: Julio Cesar Rosas Caro Victor M. Sanchez Universidad Panamericana Sede Guadalajara University of Quintana Roo 174 PUBLICATIONS 2,615 CITATIONS 52 PUBLICATIONS 531 CITATIONS SEE PROFILE SEE PROFILE Rene F. Vazquez-Bautista Luis Morales-Mendoza Universidad Veracruzana Universidad Veracruzana 25 PUBLICATIONS 92 CITATIONS 95 PUBLICATIONS 631 CITATIONS SEE PROFILE All content following this page was uploaded by Jonathan Mayo-Maldonado on 11 November 2017. The user has requested enhancement of the downloaded file. SEE PROFILE A novel DC-DC Multilevel SEPIC Converter for PEMFC systems. Julio Cesar Rosas-Caro1, Victor M. Sanchez2,*, Rene Fabian Vazquez-Bautista3, Luis Javier MoralesMendoza3, Jonathan Carlos Mayo-Maldonado4, Pedro Martin Garcia-Vite5, Romeli Barbosa2 1 Universidad Panamericana UP Campus Guadalajara, Av. Circunvalacion Poniente #49, CP 45010 Zapopan, Jalisco, Mexico. 2 Depto. Ingeniería, Universidad de Quintana Roo, Blvd. Bahía s/n Esq. I. Comonfort, 77019, Chetumal, Q. Roo, Mexico. 3 Universidad Veracruzana, Campus Poza Rica, Av. Venustiano Carranza s/n, C.P. 93396. Poza Rica Ver., Mexico 4 Instituto Tecnologico y de Estudios Superiores de Monterrey Av. Eugenio Garza Sada 2501, CP 64849 Monterrey, N.L., Mexico 5 Universidad Politecnica de Altamira Nvo. Libramiento Altamira Km 3, Sta. Amalia, CP 89602, Altamira, Tamps. Mexico *Corresponding author: Tel.: +52 983 50300, Fax: +52 983 8329656; E-mail address: [email protected] (Victor M. Sanchez). Abstract Electrical power processing is an essential sub-system of Proton exchange membrane fuel cell PEMFC systems, it is usually composed by a dc-dc converter for customizing the electrical energy before feeding the load, the SingleEnded Primary-Inductor Converter or simply SEPIC, is one of the converters with continuous input current, and it has been applied to a variety of industrial applications. This work explores the capability of the traditional dc-dc SEPIC to achieve high voltage gain by combining the converter with a diode-capacitor voltage multiplier and their applications to PEMFC systems. The continuous input current and high voltage gain is adequate for the power conditioning in fuel cell systems. For the discussed application, the voltage gain is regulated by PWM and may be extended by increasing the diode-capacitor multiplier structure. Main characteristics of the converter are: continuous input current, high-voltage gain, avoiding the use of extreme duty cycles and transformers, low voltage stresses in the power switches, besides the converter topology only employs a switch controlled and two inductors which allows a relatively simple implementation. Simulation and experimental results are provided to verify the theoretical analysis and proof of the operating principle for the dc-dc power converter proposed Keywords: DC-DC converter, voltage multilevel, high voltage gain. 1. Introduction For several renewable energy applications such as PEMFC systems, the voltage generated by the power source has to be customized to feed the load or get connected to another converter such as a grid-tie inverter, this power customization is usually performed by a dc-dc converter [1-3]. The main challenges in the design of a power conditioning system for FCs, it is to provide a high gain voltage as well as an input current with a low ripple. The voltage generated by the PEMFC system has to be customized to feed the load or get connected to another converter such as a grid-tie inverter, this power customization is usually performed by a dc-dc converter [1-3]. The DC voltage produced by a fuel cell ranges between 50-100% of their nominal value as well as it has a low magnitude too. Typically, DC-DC converters based on high frequency transformers are commonly used in order to provide a voltage gain. However, power transformers increase the cost and size of the power conditioning stage [4]. On the other hand, when a high level of current ripple is drawn to the FC, it accelerates the aging of the electrodes [5]. Usually, power converter topologies with input inductor are used in order to reduce the FC’s current ripple. The input inductor provides a trade-off between input current ripple and the converter dynamic response. Using a transformer-based converter to boost the voltage is an option but an extreme turns ratio enhances the transformer non-idealities [6-7]. Traditional transformer-less converters can achieve a relatively high voltage gain when they operate with a large duty cycle, but the transistor switching delay limits the switching frequency when the duty ratio is extreme. The use of high switching frequency allows reducing the size of converters, because it results in small inductors and capacitors with equivalent current and voltage ripples, this is the motivation to use a high switching frequency [6-7]. A methodology to achieve high voltage gain with a non-extreme duty cycle and transformer-less is highly desirable. To solve these issues, a novel DC-DC converter topology which has a high gain voltage and low ripple at the input current is proposed. The power converter is comprised by SEPIC converter cascaded with a voltage multiplier based on diode-capacitor multipliers. The SEPIC (Single-Ended Primary-Inductor Converter) is one of the traditional topologies and many industrial applications are based on the SEPIC, combinations or modifications of that topology [8-18], such as LED driving [8-9], power factor correction [10-12], and applications where a symmetric voltage is needed [13], see Fig. 1(a). Some important characteristics are: (i) it has a positive output voltage, (ii) when the converter is off, there is no dc-current from the input to the output, as may occur in other topologies [1-3]. The output voltage is provided in C2, its voltage can be expressed as: VC 2 D Vin 1 D (1) The duty cycle D can theoretically take values from 0 to 1, which means the maximum theoretically boost factor is infinite, but parasitic elements limit the upper limit usually to 0.8, also for increasing the switching frequency it is better the duty cycle to be around 0.5. High voltage gain conversion has been also realized with converter with quadratic gain [19-20] with good results but for PEMFC and other renewable energy applications non-quadratic converters are more common [1-3, 8-18]. For the SEPIC, several improvements have been proposed, one way of increasing the voltage gain is the cascaded connection of several converters, but this increase the complexity of the system [14]. The SEPIC can be extended with the voltage-lift technique, especially the re-lift and multiple lift techniques [14] with good results in voltage gain increase but an increase in the number of inductors, which are the heaviest components of the converter and transistors which requires more gate drives circuits. Another way of increasing the voltage gain is combining the SEPIC with diode-capacitors voltage multipliers [15-17]. [15] presents a methodology of combination of traditional converters with diode-capacitor voltage multipliers and the multilevel SEPIC was briefly introduced, [16] presented a different combination in which the voltage multiplier is connected to the transistor instead of the output, this provides two different outputs but may lead to sub-utilization of the system if only one output is required, which is usually the case in PEMFC systems, [17] develop a steady state space dynamic modeling of the multilevel SEPIC introduced in [15]. This work explores the capability of the SEPIC topology to get a higher voltage gain and hybridized with diodecapacitor multipliers and their applications in PEMFC systems. The topology was briefly introduced in [15], a dynamic model was developed in [17]; other extensions of the topology can be derived by extending the diodecapacitor voltage multiplier. The proposed structures achieve high voltage gain without extreme duty cycles and transformer-less, which allow high switching frequency, they have low voltage stresses in switching devices, modular structures, and more output levels can be added without modifying the main circuit, those characteristics are highly desirables in PEMFC systems. 2. Analysis of the power converter proposed. Fig. 1(a) shows the SEPIC, so-called 1x multilevel SEPIC, in the framework of this paper, the 2x multilevel SEPIC is shown in Fig. 1(b). The designation of nx multilevel converter is according with the number of output capacitors n in the converter. The transistor stays open during a time ton and then stay closed a time toff. T is the total period, which is equal to ton+toff, a duty cycle D may be defined as: t D on T ; (1 D ) toff (2) T The basic operation of the Multilevel SEPIC, see Fig. 1(a), can be summarized as: 1- The transistor closes, connecting L1 to the input voltage, the current in L1 increases with a constant slope and positive sign (according with the sign definition in Fig. 2). 2- When the transistor opens, the current in L1 charges C1 with a positive voltage (according with the sign definition). 3- When the transistor closes connects L2 in parallel with C1 and C1 charges L2 with a positive current. 4- When the transistor opens again the current in L2 closes d1 charging C2 with a positive voltage. This operation explained for the 1x Multilevel SEPIC in Fig. 1(a) applies also for the converter in Fig. 1(b) with next considerations: 5- When the transistor opens and the current in L2 closes d1, see Fig. 2(a), the negative side of C3 and C4 are connecter together, and then C3 can close d3 to charge C4 with a positive voltage. 6- When the transistor closes, C1 gets in series connection with C2, see Fig. 2(b) and the can charge C3 by closing d2. The SEPIC drives a diode-capacitor voltage multiplier, in this case is a 2x multiplier, but it can be extended by adding diodes and capacitors. Averaging the voltage in L1 during one switching cycle and considering the standard small ripple approximation [18] leads to: L1 d iL1 dt 1 t on v L1ton t off v L1toff T Where vL1ton is the voltage in L1 when the transistor is on and vL1toff is the voltage when the transistor is off, this expression can be written in terms of the duty cycle defined in (2) as: L1 d iL1 dt (3) DvL1ton (1 D)v L1toff The voltage in L1 in each switching state can be obtained from the equivalent circuits in Fig. 2. v L1ton Vin (4) v L1toff Vin VC1 VC 2 (5) In steady state, the voltage in inductors is zero, leading to a constant current, from (3) and substituting (4) and (5) this is expressed as: DVin (1 D )(Vin VC1 VC 2 ) 0 (6) In the other hand, the average voltage in L2 can be written as: L2 d iL 2 dt (7) DvL 2ton (1 D)v L 2toff In the same way as L1, the voltage across L2 during the switching states can be found from the equivalent circuits in Fig. 2. v L 2ton VC1 v L 2toff VC12 (8) (9) In steady state the average voltage across L2 is zero, this can be expressed from (7) by substituting (8) and (9): D ( VC1 ) (1 D)VC 2 0 (10) From (10), the voltage in C2 can be expressed as: D VC 2 VC1 1 D (11) Substituting (11) in (6) leads to: VC1 Vin (12) From Fig. 2(b) it can be observed that C3 is charged by C1 and C2 in series and then: D 1 VC 3 VC1 VC 2 Vin Vin Vin 1 D 1 D From Fig. 2(a) it can be observed that the voltage in C4 is the same as in C3: (13) 1 VC 4 VC 3 Vin 1 D (14) The output voltage is provided by VC2+VC4, and then it can be expressed as: D 1 1 D Vout VC 2 VC 4 Vin Vin 1 D 1 D 1 D (15) The voltage gain is high Fig. 3 shows the voltage gain again the duty cycle for different cases of n in (17), it is evidently higher than in the boost converter. From Fig. 2(a) it can be observed that the voltage blocked by the transistor is low, compared with the output voltage, this is good because a high voltage converter can be implemented with low voltage transistors, which is the principle of the multilevel converters. In other topologies such as the cascaded boost converter, the last transistor blocks the full output voltage, and this limits the maximum output voltage to the voltage handled by the transistor, furthermore high voltage transistors have higher on-resistance, compared with low voltage transistors. As it can be observed from Fig. 1, the SEPIC is used to drive a diode-capacitor voltage multiplier also called the Dickson charge pump, in this way a 3x Multilevel SEPIC and nx Multilevel SEPIC can be implemented, see Fig. 4. All capacitors over c3 in the Dickson charge pump get the same voltage of c3, and then the output voltage of the 3x Multilevel SEPIC is: 2D Vout3 x VC 2 VC 4 VC 6 Vin 1 D (16) And for the nx multilevel SEPIC the voltage gain is given by: n 1 D Voutnx Vin 1 D (17) The number of inductors, transistors, diodes and capacitors for developing the proposed topology is shown in the Table I. Another advantage of the Multilevel SEPIC is that the voltage gain can be increased without increasing the number of inductors, inductors are heavy, expensive and difficult to encapsulate, furthermore, only one transistor is needed regardless on the number of levels, increasing the number of transistors would require more circuitry. 3. Power losses in devices. This section explains how to calculate important parameters to calculate power losses in the dc-dc converter sub- system, the purpose of this chapter is to provide with straight-forward calculations that can be used in practical implementations, the procedure should be to calculate the losses in each device and ensure it can dissipate it. Inductors have different source of losses, but inductors manufacturers usually provide a parameter called the Equivalent Series Resistance ESR, the real inductor behaves such as an ideal lossless inductor in series with a resistor, and losses can be easily approximated. The dc current in inductor L1 is equal to the input current, which can be expressed as the output current Vout/R multiplier by the voltage gain, see (17), it can be finally expressed as (19), V æ n 1 D æ I L1 in æ æ R æ 1 D æ 2 (18) Where R is the load resistance, modern inductors have a low ESR, but the quadratic term on the current means that the input current increases rapidly when the voltage gain increases, this is reasonable since a for converter with a gain of 10, the input current would be 10 times larger than the output current. Multiplying the ESR by the square of (18) give us a good approximation of the inductor losses, since the current is a dc plus a triangular small ripple, a more accurate approximation would be multiplying the ESR by the RMS current, which is slightly larger than the dc current, it depends on the current ripple, if the current ripple is 10% of the dc current, the RMS current would be 0.167% larger than the dc current, see page 56 of [18], for a more accurate calculation see appendix A in [18]. It is important to notice than the ESR method is already an approximation, but the result is good enough for being used in most of industrial applications. If ripple need to be considered it can be calculated as: V D iL1 in 2 L1 f s (19) Where D is the duty cycle, and fs is the switching frequency. In the experimental prototype both inductors are 1140331K-RC from Bourns Inc. with an ESR of 75mΩ. For L2 the calculation is the same, the dc current in L2 is equal to the output current. The transistor has well known conduction and switching losses there are several approaches to calculate losses, all of them require the voltage the transistor blocks when is open, the current the transistor drains when is closed, and the duty cycle which in this case is the duty cycle of the SEPIC, the voltage the transistor blocks when is open is the voltage in C1 plus the voltage in C2, regardless on the number of capacitors in the output multiplier, from (11) and (12) this can be expressed as: 1 Vswopen Vin 1 D (20) The current the transistor conducts when is closed (see Fig. 2(b)) is equal to the current throw L1 plus the current throw L2, IL2 is equal to the output current and IL1 is equal to the input current as expressed in (18), and then the current the transistor drains when is closed is equal to: V n n 1 D I sw in R 1 D 1 D (21) In the experimental prototype the transistor is the IPP110N20NA from Infineon Technologies. Diodes drain the output current, the important parameter is the on-voltage, since their voltage is nearly insensitive to the current, the dc current multiplied by their on-voltage is a good approximation of the power losses, in power converters like this, diodes are the element that dissipate more power, their losses are larger than the transistors, since their on-voltage may be around 1V, fortunately in this case diodes drain the output current, which is the smallest current in the converter, any way it is important to care than the on-voltage times the output current is not larger than diodes maximum dissipation power. Finally, capacitors as the same as inductors have an Equivalent Series Resistance, ESR provided by the manufacturer, in our case capacitors are all B32524R3106K from EPCOS in this case, in this kind of converters capacitors dissipate few power when film capacitors are used, it is recommended not to use aluminum electrolytic capacitors, since their equivalent series resistance and equivalent series inductance is much larger, in the other hand, capacitors in the voltage multiplier have a non-rectangular waveform, multiplying the square output current times the ESR can give us a good approximation, but for non-rectangular current waveforms, losses calculation deserves a special discussion that is out of the scope of this paper, there are some references like [21], that are exclusively detonated to the estimation of power losses in capacitors with non-rectangular current. 3.1 Comments and discussion of power losses As it can be seen from equations, then the voltage gain is large, the input current is large, this may lead to high power losses in devices near the input, this happen in all high gain converters, the input current is as big as the voltage gain times the output current, special expertise and attention to power losses is necessarily when designing a high gain converter, and the power losses calculation must be considered before experimentation. 4. Simulation and experimental results. The 2x multilevel SEPIC was simulated and prototyped in order to demonstrate the operating principle. The schematic is shown in Fig. 5 with all capacitors equal to 10μF and both inductors equal to 330μH, the input voltage is 25V and the switching frequency is 50 kHz. The proposed converter was simulated in Simulink™ and the Piece-wise Linear Electrical Circuit Simulation (PLECS) software. A PEMFC stack model is used in the simulation as the DC input voltage. PEMFC model simulates a stack of 24 VDC volts and 1.2 kW. Fig. 6 shows the system simulated. Fig. 7 depicts the output voltage of the multilevel SEPIC with a resistive load of 100 Ω. Simulation results displayed in Fig. 7 demonstrate that the output voltage of the multilevel SEPIC is increased almost three times according with (17). Besides, the current drawn to the PEMFC is non-pulsed which contributes to increase the time life of the stack. The experimental prototype is showed in Fig. 8. Film capacitors were used and a Texas Instruments microcontroller MSP430G2553 provides the switching function. A resistor bank is used as a variable load for the multilevel SEPIC. Fig. 9 shows important waveforms, for an operating condition of low load, where the input current, output and switch voltages are shown for a load of 225Ω. On the other hand, Fig. 10 shows the waveforms for an operating condition of heavy load with a load of 35Ω. As can be seen the voltage ripple in capacitors is higher; the current ripple in the inductor is not different but seems lower because the different scale (2A/div). Fig. 11 shows a graphic of the efficiency versus output power, the efficiency is over 90% in most of the operating points. Fig. 12 shows a severe load-change test with a time scale of 1ms/div, it can see that the current step is very high, but the output voltage change is relatively small. The voltage change under this condition may be minimized by increasing the capacitance if necessary. 5. Conclusions This work explores the capability of the traditional dc-dc SEPIC topology to achieve high voltage gain by combining the converter with a diode-capacitor voltage multiplier and its applications to a PEMFC energy system. The toology demonstrate good results for the stablished requirements. The proposed structures have high voltage gain without the use of extreme duty cycles and without the use of transformers, this allows high switching frequency, they have low voltage stress in switching devices, modular structures, and more output levels can be added without modifying the main circuit, furthermore, when the converter is off, there is no dc path for current to flow from the Fuel Cell to the load. The voltage gain can be increased without increasing the number of inductors which are difficult to encapsulate and without increasing the number of switches which require more circuitry, by using few inductors converters get reach high efficiency, high power density and simple structures, experimental results are provided. 6. Acknowledgments This work was supported by Universidad Panamericana Campus Guadalajara, Mexico, under project UP-CI-2015FING-01. Besides, Victor M. Sanchez and Romeli Barbosa wish to thank to CONACyT under the project 252003 “Programa de Redes Tematicas (RTH2)”. 7. References [1] S. Somkun, C. Sirisamphanwong, S. Sukchai, “A DSP-based interleaved boost DC–DC converter for fuel cell applications”, International Journal of Hydrogen Energy 2015 (40), pp. 6391-404. [2] D. Guilbert, M. Guarisco, A. Gaillard, A. N'Diaye, A. Djerdir “FPGA based fault-tolerant control on an interleaved DC/DC boost converter for fuel cell electric vehicle applications”, International Journal of Hydrogen Energy 2015 (40), pp. 15815-15822. [3] P. Hong, J. Li, L. Xu, M. Ouyang, C. Fang, “Modeling and simulation of parallel DC/DC converters for online AC impedance estimation of PEM fuel cell stack”, International Journal of Hydrogen Energy 2016 (41), pp. 3004-3014. [4] L. Palma, M.H. Todorovic and P. Enjeti , “A high gain transformer-less DC-DC converter for fuel cell applications”, Proc. IEEE Power Electronics Specialists Conference, Jun. 2005, pp. 2514. [5] G. Fontes, C. Turpin, R. Saisset, T. Meynard and S. Astier, “Interactions between fuel cells and power converters influence of current harmonics on a fuel cell stack”, Proc. IEEE Power Electronics Specialists Conference, Jun. 2004, pp. 4729. [6] Z. Dongyan, A. Pietkiewicz, S. Cuk, “A three-switch high-voltage converter”, IEEE Trans on Power Electronics 1999 (14), pp. 177-83. [7] J. C. Rosas-Caro, J. M. Ramirez, F. Z. Peng, A. Valderrabano, “A DC-DC multilevel boost converter”, IET Power Electron 2010 (3) pp. 129-37. [8] Y. Wang, J. Huang, G. Shi, W. Wang and D. Xu, "A Single-Stage Single-Switch LED Driver Based on the Integrated SEPIC Circuit and Class-E Converter," in IEEE Transactions on Power Electronics, vol. 31, no. 8, pp. 5814-5824, Aug. 2016. [9] I. Burgardt, E. Agostini Junior, C. H. Illa Font and C. B. Nascimento, "Dimmable flicker-free power LEDs lighting system based on a SEPIC rectifier using a regenerative snubber," in IET Power Electronics, vol. 9, no. 5, pp. 891-899, 4 20 2016. [10]C. Shi; A. Khaligh; H. Wang, "Interleaved SEPIC Power Factor Pre-Regulator Using Coupled Inductors in Discontinuous Conduction Mode with Wide Output Voltage," in IEEE Transactions on Industry Applications , vol.PP, no.99, pp.1-1. [11]B. Poorali and E. Adib, "Analysis of the Integrated SEPIC-Flyback Converter as a Single-Stage SingleSwitch Power-Factor-Correction LED Driver," in IEEE Transactions on Industrial Electronics, vol. 63, no. 6, pp. 3562-3570, June 2016. [12]A. M. Al Gabri, A. A. Fardoun and E. H. Ismail, "Bridgeless PFC-Modified SEPIC Rectifier With Extended Gain for Universal Input Voltage Applications," in IEEE Transactions on Power Electronics, vol. 30, no. 8, pp. 4272-4282, Aug. 2015. [13]M. B. Ferrera, S. P. Litrán, E. Durán Aranda and J. M. Andújar Márquez, "A Converter for Bipolar DC Link Based on SEPIC-Cuk Combination," in IEEE Transactions on Power Electronics, vol. 30, no. 12, pp. 6483-6487, Dec. 2015. [14]M. Zhu, F.L. Luo, “Series SEPIC implementing voltage-lift technique for DC-DC power conversion”, IET Power Electronics 2008 (1) pp. 109-121. [15] J. C. Rosas-Caro, J. C. Mayo-Maldonado, A. Gonzalez-Rodriguez, E. N. Salas-Cabrera, M. GomezGarcía, O. Ruiz-Martinez, R. Castillo-Ibarra and R. Salas-Cabrera, “Topological Derivation of DC-DC Multiplier Converters”, Lecture Notes in Engineering and Computer Science 2010 (2187) pp. 904. [16]Mahajan Sagar Bhaskar Ranjana, Nandyala SreeramulaReddy and Repalle Kusala Pavan Kumar, "A novel sepic based dual output DC-DC converter for solar applications," Power and Energy Systems Conference: Towards Sustainable Energy, 2014, Bangalore, 2014, pp. 1-5. [17] J.C. Rosas-Caro, J.C. Mayo-Maldonado, J.E. Valdez-Resendiz, R. Salas-Cabrera, A. GonzalezRodriguez, E.N. Salas-Cabrera, H. Cisneros-Villegas, J.G. Gonzalez-Hernandez, "Multiplier SEPIC converter," Electrical Communications and Computers (CONIELECOMP), 2011 21st International Conference on, San Andres Cholula, 2011, pp. 232-238. [18] R. Erickson, D. Maksimovic, Book: Fundamentals of Power Electronics. Second Edition, USA: Kluwer Academic Publishers, 2001. [19]J. A. Morales-Saldaña, R. Loera-Palomo, E. Palacios-Hernández, J. L. González-Martínez, “Modelling and control of a DC-DC quadratic boost converter with R2P2”: IET Power Electronics 2014 (7) pp. 11-22. [20]R. Loera-Palomo and J. A. Morales-Saldaña, "Family of quadratic step-up dc–dc converters based on non-cascading structures," in IET Power Electronics, vol. 8, no. 5, pp. 793-801, 5 2015. [21] J.C. Mayo-Maldonado, J.C. Rosas-Caro and P. Rapisarda, "Modeling Approaches for DC–DC Converters With Switched Capacitors," in IEEE Transactions on Industrial Electronics, vol. 62, no. 2, pp. 953-959, Feb. 2015. - A novel dc-dc multilevel SEPIC converter is proposed. - The converter proposed is designed to power conditioning of a PEMFC - The converter proposed operates in continuous conduction mode which allows a nonpulsed current drawn from Fuel Cell. - The output voltage in the multilevel SEPIC converter can be increased by a diodecapacitor voltage multiplier - The voltage gain in the Multilevel SEPIC converter can be increased without increasing the number of inductors and employing one transistor. TABLE I Number of components for different Multilevel SEPIC converters Inductors Transistors Capacitors Diodes 1x 2 1 2 1 2x 2 1 4 3 3x 2 1 6 5 nx 2 1 2n 2n-1 Figure Captions Fig. 1. Multilevel SEPIC converter (a) 1x (b) 2x. Fig. 2. Equivalent circuits when (a) the transistor is off (b) the transistor is on. Fig. 3. Voltage gain vs. duty cycle. Fig. 4. 3x Multilevel SEPIC converter and extension of nx. Fig. 5. Multilevel SEPIC converter implemented. Fig. 6. PEMFC system simulated. Fig. 7. Simulation results. Fig. 8. Experimental protoype. Fig. 9. Experimental waveforms in the proposed converter with low load. Fig. 10. Experimental waveforms in the proposed converter with heavy load. Fig. 11. Efficiency vs output power. Fig. 12. Dynamic response of the Multilevel Sepic Converter. L1 Vin c1 s d1 L2 (a) Fig. 1a c2 R d3 Vin d2 c3 L1 c4 R d1 s c2 c1 L2 (b)1b Fig. Vout d3 L1 c4 d2 c3 R d1 c2 c1 Vin L2 Fig. 2a (a) d3 L1 d2 c3 R d1 c2 c1 Vin c4 L2 (b) Fig. 2b 20 18 V Vin 16 14 n=5 12 n=4 10 8 6 n=3 4 n=2 2 0 0.1 0.2 0.3 0.4 0.5 0.6 Fig. 3 0.7 0.8 0.9 1 D d5 c8 d4 c7 d5 c6 d4 c5 d3 c4 d2 c3 R d1 L1 Vin s c2 c1 L2 Fig.4 L1=L2=330μH c1=c2=c3=c4=10μF iin Vin 25V L1 sFrec 50kHz d3 c4 d2 c3 R V out d1 c2 c1 Vswitch Fig. 5 L2 Fig. 6 100 Voutput Vswitch Iinput 4.5 80 4 70 3.5 60 3 50 2.5 40 2 30 1.5 20 1 10 0.5 0 0.04 0.04 0.04 0.04 0.04 time (s) Fig. 7 0.0401 0.0401 0.0401 0.0401 0 0.0401 Iinput (A) Voltage (V) 90 5 L2 Diodes L1 Capacitors Mosfet Microcontroller Fig. 8 2A/div iin=iL1 Vout 6A 0A 80V Vswitch 0V 20V/div Fig. 10 0.5A/div iin=iL1 1.5A Vout 0A 80V Vswitch 0V 20V/div Fig. 9 2A/div Vout 80V 8A iin=iL1 0V 0A 20V/div Time: 1ms/div Fig. 12 93 92 91 90 89 88 87 0 50 100 Fig. 11 View publication stats 150 200 250