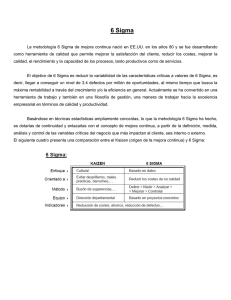

UNIVERSIDAD DE BUENOS AIRES FACULTAD DE INGENIERÍA Año 2011 – 2° Cuatrimestre REDES NEURONALES (66.63) TEMA: DETECCION DE SPIKES NEURONALES A TRAVES DE FILTROS ADAPTADOS RESULTANTES DE UNA RED DE KOHONEN ALUMNOS: Gena, Anabella Cecilia- # 86343 [email protected] Yegier, Ariel Alejandro- # 86888 [email protected] Índice Objetivo Especificaciones FPGA: Diagramas en bloques FPGA: Descripción de las arquitecturas FPGA: Diagrama de flujo de la CPU Matlab: Red de Kohonen Matlab: Código de la red de Kohonen Matlab: Instructivo de uso del aplicativo 3 3 3 6 8 10 11 12 Objetivo Clasificar spikes a través de filtros adaptados, para poder identificar a qué neurona pertenece cada uno de los detectados con un mismo electrodo. Esto es necesario pues cada uno de ellos sensa el comportamiento de más de una neurona, con el incremento de ruido en el mecanismo de toma de muestras. Los patrones se obtendrán a través de una red de Kohonen y se implementarán en una FPGA, en la cual se realizará el filtrado correspondiente de la señal. Especificaciones Se implementó en lenguaje descriptor de hardware VHDL: una interfaz serie UART, un controlador para la memoria RAM externa, una arquitectura compuesta por un arreglo de tres filtros adaptados FIR y una CPU que controle todo el sistema de transmisión de datos entre los bloques. Se sintetizó con la herramienta ISE la descripción de hardware para la FPGA: - Fabricante: Xilinx - Familia: Spartan 3 - Modelo: xc3s200 - Encapsulado: FT256 - Speed: -4 Se implementó la descripción en el kit de desarrollo “Spartan-3 Starter Board" de la empresa Digilent. Se utilizó además para la programación de la red de Kohonen el programa Matlab versión R2009B. Para la comunicación con la PC es necesario un cable serie RS232 derecho. FPGA: Diagramas en bloques A continuación se presentan los diagramas en bloques y de entradas y salidas de la estructura en general del sistema, los filtros FIR, el controlador de la RAM externa y la uart, cuyos funcionamientos se describirán luego: FIGURA 1: Diagrama en bloques del sistema de filtrado implementado en la FPGA FIGURA 2: Diagrama de entradas y salidas de la arquitectura filterFir FIGURA 3: Diagrama en bloques del controlador de la RAM FIGURA 4: Diagrama en bloques de la UART FPGA: Descripción de las arquitecturas El proyecto está compuesto de tres bloques de comportamiento que son: uart, ram_controler y tres instancias de filterFir, los cuales están comandados y se relacionan entre sí a través de la cpu. Todas las arquitecturas mencionadas son instanciadas en el archivo de vhdl Top_board_TP_FINAL.vhd, en donde también son definidos cuáles de los switches y pulsadores de la placa experimental serán utilizados para controlar la comunicación y el filtrado de las señales. Todos los archivos cuyo nombre comience con “Simul”, son archivos de simulación, utilizados para la prueba de los archivos de proceso. UART: Consta de tres bloques básicos: timing: setea las bases de tiempo para la correcta sincronización entre la PC y la FPGA, dada la velocidad de transmisión, que en nuestro proyecto se ha impuesto a 115,2Kbps. Un parámetro importante a definir ha sido la variable Divisor, la cual se calcula fCLOCK 50MHz 27 y define la base de tiempos de la transmisión. 16. fTRANSMISION 16.115200bps receive: controla la recepción de bits serie, para devolver NDBits-1 en paralelo, a través de una programación secuencial. transmit: controla la transmisión de NDBits-1 bits en paralelo, para devolver bits en serie, a través de una programación secuencial. Luego se controlan estos tres bloques con un cuarto bloque llamado uart, el cual sólo los instancia. Un quinto bloque llamado uart_comps, declara los tres componentes. RAM_CONTROLER: Es un único bloque que, mediante una programación secuencial, controla el flujo de datos entre la FPGA y la RAM externa, a través de señales que son seteadas desde la cpu. El principal objetivo es controlar el puerto input-output que es triestado, según si se encuentra en modo lectura o escritura. La memoria es asincrónica, debido a que la lectura y escritura de la misma se realiza con señales de esta naturaleza. FILTERFIR: Es un bloque de comportamiento secuencial, en donde recibe las 60 muestras de señal a filtrar y las guarda en una memoria RAM circular de doble acceso (escritura y lectura simultánea). Con dichas muestras realiza las multiplicaciones sucesivas con las muestras correspondientes al filtro, y su resultado lo suma con la acumulación de las multiplicaciones anteriores. De esta manera se implementa la definición de convolución de ambas señales, con un tiempo de desplazamiento de los vectores que conforman los multiplicadores de un ciclo de reloj de 50MHz de frecuencia. El retardo del filtro, es decir el tiempo que demora el filtro en procesar una muestra de la señal de entrada, se obtiene de la siguiente manera: longitud del buffer 60 1 4.ciclos de reloj= 4. 1, 28 s f clock 50MHz 50MHz Los cuatro ciclos de clock son los necesarios para acondicionar la señal en el filtro. Este tiempo es óptimo, pues se desea que sea superior a la frecuencia de muestreo que es de 30KHz. Por último el resultado se coloca en un buffer de salida. El comportamiento es esquematizado en la figura 5. Se utiliza la memoria RAM circular para ser direccionada a través de dos punteros, uno para lectura y otro para escritura, desplazados en una posición de memoria para escribir donde se ha leído y de esta manera optimizar el tiempo de procesamiento. FIGURA 5: Esquema de comportamiento del filtro adaptado CPU: La CPU es una máquina de estados que controla cada uno de los bloques componentes: uart, ram_controler y los tres filterFir. El proceso que se realiza está ilustrado en el diagrama de flujo de la siguiente página. Todo está comandado por los switches y pulsadores que se encuentran en la plaza experimental. Es importante mantener el orden de cada uno de los pasos, como puede verse en el diagrama de flujo, para lograr los resultados correctos. FPGA: Diagrama de flujo de la CPU Matlab: Red de Kohonen Se implementó una red de Kohonen para obtener los filtros mediante template matching utilizando los pesos de las neuronas. La red es unidimensional y las entradas son 60, pues ese es el largo del vector de muestras que representan a cada spike. Se utilizó en el algoritmo el doble de neuronas (6) que de spikes que se desean detectar, pues cada electrodo sensa el comportamiento de aproximadamente esa cantidad de neuronas físicas. La constante de aprendizaje para la corrección de los w es de 1 . La función de vecindad utilizada es de la forma: e r r *2 2 2 Donde r * es el vector correspondiente a la neurona ganadora, que es la cual su peso es el más cercano a la entrada presentada a la red en esa iteración. La manera de variar el valor de de tal forma que converja la vecindad hacia sólo la neurona ganadora en las últimas iteraciones, de 2000 que se realizan en total, fue asignarle el siguiente valor: num _ it 2000 sigma _ cte con sigma _ cte 10 sigma _ partition 200 aux Incrementando el valor de la variable aux cada sigma _ partition iteraciones. Luego cuando se cumple que 1 , se aplica el siguiente cambio de sigma para cada una de las iteraciones: 1 log(aux sigma _ cte 10) La función recibe tres parámetros: W = Kohonen_Learning(Sample,w_orig,N); Donde Sample son vectores de las muestras de la señal que se desea aprender, w_orig son los pesos de las neuronas iniciales antes de comenzar el algoritmo y N es la cantidad de neuronas. La función devuelve W que son los pesos de las neuronas, cuyos valores luego se utilizarán en los filtros. Matlab: Código de la red de Kohonen function W = Kohonen_Learning(Sample,w_orig,N); % Sample deben ser tantos vectores columna como cantidad de señales se % desea aprender % Las filas de w_orig son cada uno de los vectores pesos aleatorios para % cada neurona % N es la cantidad de neuronas num_it = 2000; Eta = 1; num_ent = size(Sample,1); num_signals = size(Sample,2); w = w_orig; % valores iniciales de los pesos de las neuronas ind = [1:N]'; sigma = 10; sigma_partion = 200; % en intervalos de sigma_partion se cambiara el valor de Sigma sigma_cte = num_it/sigma_partion; aux = 2; % variable que se incrementara cada cierta cantidad de iteraciones distanc = zeros(N,1); for i = 1:num_it for k = 1:num_signals for j = 1:num_ent distanc = distanc + (w(:,j)-Sample(j,k)).^2; end distanc = sqrt(distanc); [min_distancance,winer_neuron] = min(distanc); if mod((i-1),sigma_partion)==0 sigma = sigma_cte/aux; aux = aux+1; end if sigma<=1 sigma = 1/log10(aux-sigma_cte+10); aux = aux + 3; end vec_function = exp(-((ind-winer_neuron).^2)/(2*sigma^2)); for m = 1:num_ent delta_w(:,m) = Eta*vec_function.*(Sample(m,k)-w(:,m)); end w = w + delta_w; end end W = w; return Matlab: Instrucciones de uso del aplicativo Se deberá ejecutar el archivo tpFinal.m en Matlab versión R2009B para que se haga visible la interfaz que se muestra en la figura 6. Desde allí se podrá, tanto para un vector de muestras de una señal neuronal o para una señal de prueba compuesta de tres patrones de 60 muestras con distintas formas y sin ruido añadido: Procesar la señal por una red de Kohonen para obtener los filtros mediante el método de template matching. Ellos podrán ser observados en la interfaz para elegir luego los que se consideren más representativos. Enviar a la memoria de la placa experimental la señal Enviar a la memoria interna de la FPGA los filtros Enviar a la memoria interna de la FPGA los umbrales de detección para ser utilizados por las arquitecturas implementadas. Reenviar desde la FPGA la señal original almacenada en la memoria de la placa experimental para verificar el correcto funcionamiento de la comunicación. Enviar desde la FPGA hacia la PC la señal filtrada por cierto filtro, pudiendo elegir uno por vez. Enviar una secuencia de números compuesto por la ocurrencia del spike detectado según cada filtro preseleccionado. Ej: 1-2-1-3-2. La secuencia detectada será: o 1º spike correpondiente al 1º filtro seleccionado o 2º spike correpondiente al 2º filtro seleccionado o 3º spike correpondiente al 1º filtro seleccionado o 4º spike correpondiente al 3º filtro seleccionado o 5º spike correpondiente al 2º filtro seleccionado Realizar el mismo procesamiento que se realizó con la FPGA mediante Matlab. FIGURA 6: Interfaz de Matlab para control de comunicación y procesamiento El esquema de la placa experimental se presenta en la figura 7. Allí pueden verse los pulsadores y switches para comandar la comunicación y filtrado de las señales. FIGURA 7: Esquema de la disposición de los componentes de la placa experimental En la figura 8 se detallan los nombres utilizados para cada uno de los pulsadores y los switches. FIGURA 8: Esquema de disposición de los pulsadores y switches de la placa experimental Los pasos a seguir para el correcto filtrado de la señal son: 1. Cargar la señal pulsando el botón correspondiente, ya sea de la señal de prueba o de la neuronal. Sobre esta última se pueden seleccionar la cantidad de muestras a analizar, las cuales se deben colocar en el rectángulo blanco que se encuentra debajo del botón “Cargar señal neuronal”. Cuando finaliza este proceso se muestra una figura con la señal cargada. En la figura 9 se presenta un ejemplo de la señal de prueba. FIGURA 9: Señal de prueba compuesta por tres patrones que se suceden de manera aleatoria 2. Procesar la señal presionando el botón correspondiente. Se obtendrán de esta manera los pesos de la red neuronal, los cuales conforman los filtros que se muestran en pantalla. FIGURA 10: Resultado del procesado de la señal neuronal 3. A continuación se seleccionan los tres filtros más representativos, para el posterior envío y uso en la FPGA. 4. En primera instancia se deberá resetear la FPGA presionando el pulsador L14. 5. A partir de este paso se comienzan a enviar las herramientas necesarias para el filtrado. Se debe preparar la FPGA para la recepción de la señal colocando todos los switches en posición baja (la que se muestra en la figura 8) y presionando luego el pulsador L13. Para comenzar la transmisión se coloca la opción en el aplicativo de Matlab “Señal” y se presiona “Enviar”. 6. La recepción finaliza cuando los leds de la placa experimental terminan de parpadear, y para colocar a la FPGA nuevamente en reposo se deberá presionar el pulsador M14. 7. Para enviar los filtros se repiten los pasos 5 y 6 pero se deberá seleccionar en el aplicativo la opción “Filtros” y todos switches en posición baja con excepción del F12. 8. Para enviar los umbrales, los cuales se pueden ver en la parte inferior derecha de la ventana, se deberán repetir los pasos 5 y 6 pero seleccionando la opción “Umbrales” y todos los switches en bajo con excepción del G12. Se ilustra en la figura 11. 9. A partir de ahora se podrá filtrar la señal y enviar los resultados a la PC, pero también es posible enviar la señal original para verificar la correcta comunicación. Para ello se debe preparar para la recepción a la PC seleccionando “Señal original” y presionando “Recibir”. Luego se colocan todos los switches en bajo y se presiona el pulsador M13. 10. Para enviar a la PC las señales filtradas, se deberá aplicar a cada uno por vez. Primero se debe preparar a la PC para la recepción colocando la opción “Señal filtrada” y según por qué filtro se desee procesar se pondrá en alto el Switch correspondiente: a. Primer filtro: K13 en alto b. Segundo filtro: K14 en alto c. Tercer filtro: J13 en alto 11. Una vez seleccionado el filtro se presionará el pulsador M13. Finalizado el envío se representará en la pantalla el resultado, como puede verse en la figura 12. FIGURA 11: Envío de umbrales hacia la FPGA FIGURA 12: Señal de prueba filtrada por los tres filtros 12. Se puede enviar también desde la FPGA la secuencia de spikes detectados en el fragmento de señal analizado. Se puede seleccionar la cantidad de datos a recibir colocando la cantidad en el cuadrado blanco del extremo inferior derecho, como se ilustra en la figura 13. En la figura 14 se presenta un ejemplo de secuencia detectada, los resultados serán siempre 1,2 o 3. FIGURA 13: Selección de la cantidad de datos a enviar a la PC FIGURA 14: Secuencia de spikes detectados enviados a la PC 13. Por último se pueden comparar los resultados obtenidos con el procesamiento equivalente realizado por Matlab presionando el botón “Procesar con Matlab”.