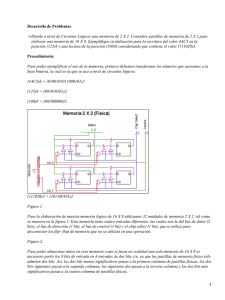

Universidad Nacional Autónoma de México Facultad de Ingeniería Alumnos: Carrasco Mora Carlos Fernando Fernández Carrillo Paul Andrés Ibarra Olvera Javier Profesor: Roberto Mandujano Wild Asignatura: Diseño Digital Proyecto: Sumador de 2 Palabras de 4 Bits Con Carry Look Ahead Proyecto: Sumador de 2 Palabras de 4 Bits con Carry Look Ahead Introducción: En este proyecto presentaremos la descripción y la teoría necesaria para comprender las bases del circuito el cual tiene la función de sumar dos palabras de 4 bits cada una, utilizando el método “Carry Look Ahead”, el cual tendrá la ventaja de realizar la suma lo más rápida y eficientemente posible. Se presentará en un principio la teoría que describe la manera de armarlo, y luego se presentará el diagrama de conexión para ser armado en la tarjeta prototipo. Cabe mencionar también que el “Carry Look Ahead” puede ser adquirido ya en un circuito integrado. Sin embargo el objetivo es armar el circuito completo con puras compuertas lógicas. Como el objetivo del proyecto es sumar 2 palabras de 2 bits, tendremos a continuación una descripción de los métodos de suma. A) Half Adder: Traducido como “medio sumador”, es un método de suma binario que no considera el carrier anterior para sumar, es decir, las únicas entradas que tiene son dos variables, y como salida, una suma y un carry. Aquí tenemos su diagrama ejemplificado, tabla de verdad y función equivalente: Ai 0 0 1 1 Bi 0 1 0 1 Ci+1 = AiBi Ci+1 0 0 0 1 Si 0 1 1 0 Si = Ai Bi B) Full Adder: Este método, traducido como sumador completo, aparte de sus 2 variables de entrada, considera el carrier anterior de alguna otra suma, como se observa a continuación: Ai 0 0 0 0 1 1 1 1 Bi 0 0 1 1 0 0 1 1 Ci 0 1 0 1 0 1 0 1 Si = Ai Ci+1 0 0 0 1 0 1 1 1 Bi Ci Ci+1 = AiBi + AiCi + BiCi Si 0 1 1 0 1 0 0 1 Así, con estos elementos tenemos la posibilidad de realizar sumas de cualquier cantidad de bits, iniciando primero con un Half Adder, ya que no hay carry al inicio, y después utilizando tantos Full Adder como sean necesarios. Para este caso, el tiempo que tardaría una implementación así sería de (2n – 1)Δt. El problema que tenemos es que para obtener la suma completa, se necesita esperar a que se genere el carry. Pero existe una manera más rápida de efectuar la suma. Si se prevee cuál será el valor del carry, se puede efectuar toda la suma al mismo tiempo. A éste método se le llama Carry Look Ahead. Para el Carry Look ahead: Partimos de las funciones del Full Adder: Si= Ai Bi Ci Ci+1 = AiBi + AiCi + BiCi = AiBi + (Ai Bi)Ci De la expresión Ci+1, llamaremos: AiBi = Gi (Generador) Ai Bi = Pi (Propagador) Con estas 2 funciones se puede prever qué va a suceder en cada etapa: si se va a generar un carry, y segundo, si se va a propagar el carry. Entonces tenemos: Ci+1 = Gi + PiCi Para el proyecto necesitaremos sumar hasta 4 bits, entonces desarrollaremos hasta el carry no. 4: Desarrollando para i = 0, 1, 2, 3, 4: Para i = 0 C1 = G0 + P0C0 = G0 Para i = 1 C2 = G1 + P1C1 = G1 + P1G0 Para i = 2 C3 = G2 + P2C2 = G2 + P2(G1 + P1G0) C3 = G2 + P2G1 + P2P1G0 Para i = 3 C4 = G3 + P3G3 = G3 + P3(G2 + P2G1 + P2P1G0) Ahora tenemos el diagrama del CLA con compuertas: Por último, mostramos el diagrama del Full Adder con Generador Propagador: Por último, el diagrama general es el siguiente: A continuación mostraremos la implementación de este circuito.