En las aplicaciones de circuitos de conmutación, casi todos los elementos de

memoria son circuitos electrónicos biestables; es decir, existen indefmidamente en uno

de dos posibles estados estables, 0 y 1. Los datos binarios se guardan en un elemento

de memoria haciendo que el elemento pase al estado 0 para almacenar un o y al

estado 1 para almacenar un 1. La salida Q del circuito indica el estado presente de la

memoria. Cada circuito de memoria tiene una o más entradas de excitación, llamadas

asf por que sirven para "excitar" o llevar el circuito a un estado deseado. Los distintos

dispositivos de memoria reciben por lo general su nombre con base en sus entradas

de excitación particulares, diferentes de iln dispositivo a otro.

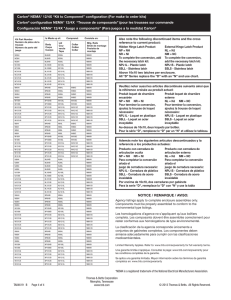

Los dos tipos de elementos de memoria comúnmente utilizados en los circuitos

de conmutación son los latches y Io sflip-f/ops.Un latch (latch) es un elemento de

memoria cuyas señales de entrada de excitación controlan el estado del dispositivo. Si

un latch tiene una sef\al de entrada de excitación que obliga a la salida del dispositivo

a asumir el valor 1, ésta es un latch set. Si el latch tiene una señal de entrada de

excitación que obliga al dispositivo a asumir el valor 0, ésta es un latch reset. Si el

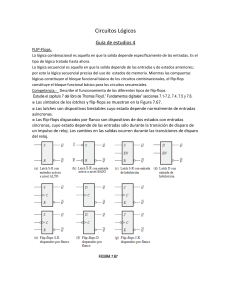

dispositivo tiene señales de excitación set y reset, es un latch set-reset. La figura 6.4a

muestra la operación de un latch.

.

figura 6.4a El latch responde de inmediato a la excitación

Un jlip-jlop difiere de un latch por el hecho de que tiene una señal de

control llamada reloj. La seHal de reloj emite una instrucción· al jlip-jlop,

permitiéndole cambiar de estado de acuerdo con las señales de entrada de

excitación. En Jos latches y losjlip-flops, el siguiente estado queda determinado

por las entradas de excitación. Sin embargo, como muestra la figura 6.4, un

latch cambia de estado de inmediato, según sus seftales de excitación de entrada,

mientras que unjlip-jlop espera la señal de su reloj antes de cambiar de estado.

El estado final de unjlip-jlop está determinado por sus valores de excitación en

el instante en que se presenta la señal de reloj. De esta manera, se pueden

sincronizar varios jlip-jlops de un circuito secuencial con una señal de reloj

común para que cambien de estado todos juntos.

En el capítulo 1 O presentaremos algunos procedimientos formales para

diseftar circuitos conjlip-jlops y latches. En este capítulo describiremos circuitos

jlip-jlop y latch genéricos, así como diversos módulos TTL que contienen estos

dispositivos. La tabla 6.1 tiene la lista de los dispositivos que analizaremos.

Muchos otros dispositivos están disponibles en el comercio. Hemos elegido éstos

como introducción a las diversas características disponibles. El lector deberá

comprender estas características para poder elegir un dispositivo adecuado a

cada situación al disefiar circuitos secuenciales.

1 Latch set-reset

Uso de retroalimentación para crear latches simples

Considere la compuerta OR de la figura 6.5a. Suponga que ambas entradas se

encuentran en 0 lógico. Si conectamos la salida de nuevo a una de las entradas, como

en la figura 6.5.b, la compuerta se estabiliza con una salida de Q en 0. Si aplicamos un

1 lógico a la entrada no conectada S, como en la figura 6.5.c, ¿qué le sucede a la

salida de la compuerta OR? Cambia a 1 lógico. Así, hemos establecido (set) La salida

del dispositivo Q como 1 lógico. Si cambiamos la entrada S de nuevo a 0 lógico, la

salida Q sigue con el valor 1 lógico, debido a la retroalimentación a la otra entrada de

la compuerta OR, como en la figura 6.5.d Así, este dispositivo asume el valor 1 lógico

de manera permanente y lo llamamos un latch set.

Fig.6.5. Latch set. (a) Compuerta OR. (b) Con retroalimentación. (e) Salida con valor 1.

(d) La retroalimentación mantiene Q = 1.

Reemplacemos la compuerta OR de la figura 6.5 por compuertas NOR y NOT

en cascada, como en la figura 6.6a. Éste es un circuito de latch set equivalente. Si

utilizamos la salida de la compuerta NOR como salida Q del latch, generamos el

circuito de la figura 6.6b. Examine el funcionamiento de estas compuertas en cascada.

La salida de la compuerta NOR se encuentra inicialmente en 1 lógico si sus dos

entradas tienen el valor 0 lógico. La señal de retroalimentación de la compuerta NOT

es 0 lógico, lo que produce una condición estable. Al colocar un 1 lógico en la entrada

no conectada R de la compuerta NOR, su salida debe ser 0 lógico, como se muestra

en la figura 6.6c, lo que hace que la señal de retroalimentación sea 1 lógico. Así, la

salida del latch Q se restablece (reset) a 0 lógico. Si R vuelve a asumir el valor 0

lógico, como se muestra en la figura 6.6d, no habrá cambios en la salida, debido a la

señal de retroalimentación. Por tanto, la salida Q mantendrá el valor 0 lógico,

ignorando los cambios posteriores en la entrada R. Este circuito se llama un latch

reset. La figura 6~6e presenta otra vista del circuito.

Figura 6.6 Latch reset. (a) Latch set redibujada. (b) Latch reset estable con Q = 1. (e)

R = 1 reestablece la latch como Q = 0. (d) los cambios posteriores son inhibidos. (e)

Vista alternativa del latch reset.

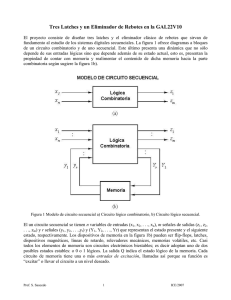

Latch set-reset: Estructura NOR Los dispositivos que se estabiliz.an en un

estado lógico no son muy útiles, excepto en situaciones de disefio poco usuales. Si

combinamos las características de los dos /atch_es ya descritos en un único circuito,

podemos activar o desactivar el circuito latch según sea necesario. Remplacemos la

compuerta NOT del circuito de la figura 6.6a por una compuerta NOR de dos entradas,

N2, conectadas a modo de operar como una compuerta NOT, como en la figura 6.7a.

El dispositivo aún opera como latch set. Ahora bien, si desconectamos la entrada

inferior de la compuerta NOR N2 como en la figura 6.7b, esta entrada funcionará como

una excitación reset para el dispositivo (la misma función que en la figura 6.6e). Así,

hemos creado un latch set-reset (latch SR) con dos compuertas NOR de dos entradas.

El diagrama tradicional del circuito es la forma con acoplamiento cruzado de la figura

6.7c. Adoptaremos el símbolo lógico de la figura 6.7d para representar el latch SR. Lo

utilizaremos como bloque de construcción para otros circuitos en esta sección.

Figura 6. 7 Latch set-reset {Latch SR). (a) Latch S redibujada. (b) Latch SR.

(e} Vista tradicional del latch SR. (d) Símbolo lógico del Latch SR.

Latch SR: Estructura NAND

¿Podemos obtener los mismos dispositivos funcionales que dedujimos con

compuertas NOR utilizando compuertas NAND? Consideremos las compuertas NAND

con acoplamiento cruzado de Ja figura 6.8a. Si las dos ·entradas S y R asumen el

valor O lógico, las compuertas NOT aplican seftales 1 lógicas a las compuertas NAND

con acoplamiento cruzado. Pero si una de las entradas de una compuerta NANO de

dos t>ntradas se coloca en 1 lógico, actúa como una compuerta NOT; es decir,

Compuerta N 1 (S = 0); (S’ · Q’)’ = (1 · Q’)’ = Q’’ = Q, o bien

Compuerta N2 (R = 0): (R’ · Q)’ = (1 · Q)’ = Q

Así, las compuertas con acoplamiento cruzado de la figura 6.8 asumen la función

de un par de compuertas NOT cuando las entradas son S = R =O, como se muestra

en la figura 6.8b. (Indicamos las compuertas NOT con lineas punteadas dentro de las

compuertas NAND para ilustrar que éstas últimas re~ente actúan como inversores). El

bucle de compuertas NOT de la figura 6.8b forma la celda de almacenamiento

biestable para el latch. La salida Q se introduce en una compuerta NOT para generar

Q, y Q se introduce en la segunda compuerta NOT para regenerar Q.

Si alguna de las entradas So R está activa, es decir, con el valor 1 lógico, y la otra

biene el valor O lógico, una parte de la configuración con acoplamiento cruzado

simétrico se altera cuando se aplica un O lógico a la entrada de una de las compuertas

NAND; es decir,

Compuerta N 1 (S = 1); (S’ · Q’)’= (0 · Q’)’ = 0 = 1, o bien

Compuerta N2 (R = 1): ´(R·Q) = (0 · Q)’ = 0’ = 1

Así, una entrada 0 lógica a la compuerta NANO hace que su salida asuma elvalor 1

lógico. El 1 lógico en la salida de la compuerta NAND activa hace que la salida de la

otra NANO del par asuma el valor O lógico, ya que

Compuerta N2 (S = 1, R =0): Q’ = (R’ · Q) =(0’ · 1)’ = (1 · 1)’ = 1’ =0, o bien

Compuerta Nl (S =0, R = 1): Q = (S’ · Q’)’ = (0’ · 1)’ = (1 · 1)’ = 1’ =0

Figura 6.8 Latch SR NANO. {a) Diagrama lógfico. (b) Modo de almacenamiento.

(e) Lógica reducida. (d) Símbolo lógico 1. (e) Símbolo lógico 2.

Así, un 1 lógico en S hace que Q asuma el valor 1 lógico, por lo que Q asume el

valor 0 lógico. En otras palabras, un 1 lógico en S establece el latch. De la misma

manera, un 1 lógico en la entrada R hace que Q asuma el valor 1 lógico, por lo que la

salida asume el valor 0 lógico, restableciendo el latch. Eliminemos las dos compuertas

NOT de las entradas del circu~, como en la figura 6.8c. Las entradas del dispositivo se

convierten en S y R. En otras palabras, las entradas del lalch son activas bajas

(normalmente, altas en el estado activo y pasan a bajas para activar el dispositivo).

Adoptaremos los símbolos lógicos de las figuras 6.d y e para representar un latch SR

con entradas activas bajas.

Diagramas de tiempos y parámetros de retar,do en un latch SR Podemos describir

el funcionamiento de cualquier latch mediante un diagrama de tiempos. La figura 6.9a

muestra la acción inducida en el latch NOR con acoplamiento cruzado de la figura 6.7c

al aplicar secuencias de pulsos a las entradas set y reset, S y R. Elegimos las formas

de onda para S y R a modo de ilustrar varias características del latch. Supondremos

que el estado inicial del latch es O lógico (Q = O). El dispositivo responde al primero

de una serie de pulsos sobre una de sus entradas, pero ignora los demás pulsos hasta

que un pulso interviene en la otra entrada.

Observe que al colocar las seflales con el valor 1 lógico en ambas entradas R y S,

las salidas Q y Q asumen el valor 0 lógico. Cuando las dos entradas vuelven al valor 0

lógico, se crea una condición de competencia y, por tanto, no podemos detenninar con

certeza el estado que asumirá el dispositivo. En el mundo real, es virtualmente

imposible que dos eventos sucedan exactamente al mismo tiempo, ¡aunque asf lo

desee! Si la seflal R regresa al 0 lógico antes que S, el estado final de Q será 1 lógico.

Si Sregresa primero al 0 lógico, el dispositivo asume el valor 0 lógico. Si R y S

regresan al 0 lógico al mismo tiempo, o casi al mismo tiempp, las dos compuertas

NOR competirán para ganar el control de la salida Q. Si ambas son equivalentes

desde el punto de vista eléctrico, ¡la salida oscilará! En los circuitos prácticos, gana

una de las compuertas, pero no podemos

Figura 6.9 Diagrama de tiempos del fstch set-reset. (a) Caso Ideal (retardo por

compuertas nulo). (b) Tiempos reales con retardos de compuerta distintos de cero.

predecir cuál de ellas. Por tanto, restringimos el uso del latch SR excluyendo la

combinación de entradas S = R = 1.

El diagrama de tiempos de la figura 6.9a representa una situación ideal en la que

todos los retardos por propagación en la compuerta se consideran como 0. En

realidad, cada salida del circuito requiere un tiempo distinto de cero para responder a

las modificaciones de sus entradas, como lo especifican los parámetros de retardo

tPLH y tPHL' definidos en el capítulo 2. Re1cuerde que tprn denota al tiempo de

retardo entre un cambio en la entrada y una transición de baja a alta de la salida

correspondiente. De igual manera, tPHL es el retardo entre un cambio en la entrada y

una transición de alta a baja de la salida correspondiente.

Para un circuito de latch, los parámetros tPLH y tPm. representan la suma de los

retardos por propagación a través de las compuertas entre la entrada y salida de un

/atch dado; por lo general se especifican parámetros de retardo distintos para cada par

entrada/salida.

Por ejemplo, la figura 6.1 O ilustra el comportamiento del latch SR de la figura 6. 7 c

con respecto al tiempo. Después de un cambio en S de O ~ 1, observe que la salida Q

cambia de 1 ~ O después del retardo por propagación tPHL a través de la compuerta

NOR NI; a continuación, la seftal de retroalimentación hace que la salida Q cambie de

O ~ 1 después del tiempo de propagación /PLH a través de la compuerta N2. Así, la

salida Q siempre cambia entes que la salida Q cuando ponemos en 1 un latch SR

construida a partir de compuertas NOR con acoplamiento cruzado. Por tanto, el tiempo

/PHL de la entrada S a la salida Q del /atch sólo implica un retardo de compuerta,

mientras que /PLH de la entrada S a la salida Q tiene dos retardos de compuerta.

Existe una relación similar entre la entrada R y las dos salidas. Al poner en cero el

latch con un pulso en la entrada R, .la salida Q cambia antes que la salida Q, como en

la figura 6.10. En vista de estos retardos por propagación distintos de cero a través de

las compuertas del circuito latch, la figura 6.9b presenta una imagen del

luncionamiento del latch más real que el diagrama de tiempos ideal de la figura 6.9a.

Tabla de excitación y ecuación característica del latch SR

La tabla de excitación de la figura 6.11 a resume el funcionamiento lógico del

latch SR. La tabla de excitación es simplemente la tabla de estados del latch y muestra

las transiciones de estado para cada combinación de las entradas de excitación. Las

columnas S y R son las entradas aplicadas a un latch SR mientras

está en el estado Q. La columna rotuláda Q es el estado del latch SR antes de aplicar

una combinación de entradas a S y R. La columna Q* es el estado del latch SR

después de aplicar las entradas SR y obtener un resultado estacionario.

La columna Q es el estado presente del latch SR y la columna Q* es el siguiente

estado.

Podemos representar la información de la figura 6.11 como un diagrama de estados

(Fig. 6.11 b) o como un mapa K (Fig. 6.11 e), donde damos el valor del siguiente

estado Q* en función de las entradas, S y R, y del estado presente Q. El mapa K nos

permite deducir la siguiente expresión lógica para Q*, llamada ecuación característica

del latch SR:

Q* =S+ RQ (6.10)

La ecuación característica recibe ese nombre porque caracteriza el funcionamiento del

latch. Por ejemplo, podemos clasificar el funcionamiento del latch en tres casos.

Caso 1: S = R =O. La ecuación 6.1 O se reduce a Q• = Q, lo que indica que el estado

no cambia.

Caso 2: s = 1, R =o. La ecuación 6.1 O se reduce a Q* = 1, lo que representa la

operación de establecimiento (set).

Caso 3: S = O, R = 1. La ecuación 6.1 O reduce a Q• =o, representando la operación

de restablecimiento (reset).