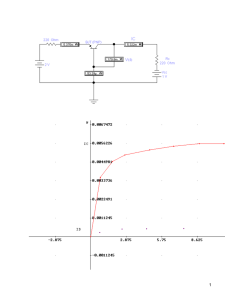

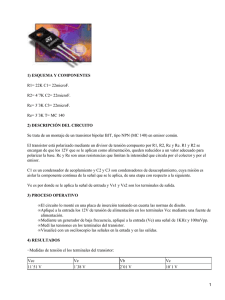

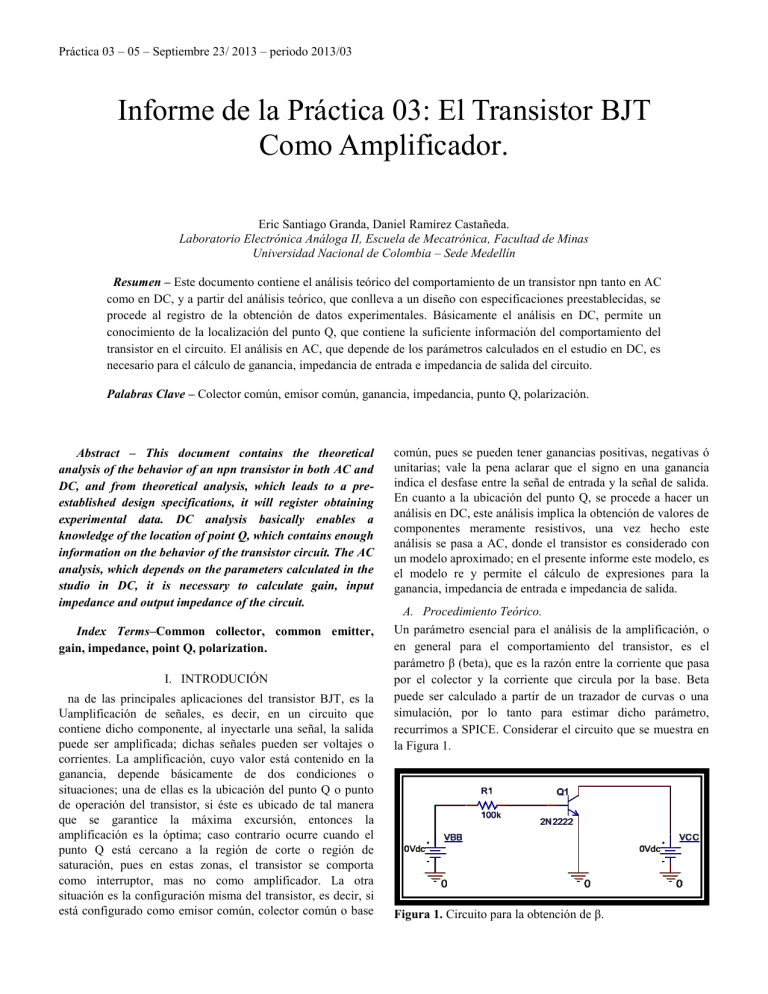

Práctica 03 – 05 – Septiembre 23/ 2013 – periodo 2013/03 Informe de la Práctica 03: El Transistor BJT Como Amplificador. Eric Santiago Granda, Daniel Ramírez Castañeda. Laboratorio Electrónica Análoga II, Escuela de Mecatrónica, Facultad de Minas Universidad Nacional de Colombia – Sede Medellín Resumen – Este documento contiene el análisis teórico del comportamiento de un transistor npn tanto en AC como en DC, y a partir del análisis teórico, que conlleva a un diseño con especificaciones preestablecidas, se procede al registro de la obtención de datos experimentales. Básicamente el análisis en DC, permite un conocimiento de la localización del punto Q, que contiene la suficiente información del comportamiento del transistor en el circuito. El análisis en AC, que depende de los parámetros calculados en el estudio en DC, es necesario para el cálculo de ganancia, impedancia de entrada e impedancia de salida del circuito. Palabras Clave – Colector común, emisor común, ganancia, impedancia, punto Q, polarización. Abstract – This document contains the theoretical analysis of the behavior of an npn transistor in both AC and DC, and from theoretical analysis, which leads to a preestablished design specifications, it will register obtaining experimental data. DC analysis basically enables a knowledge of the location of point Q, which contains enough information on the behavior of the transistor circuit. The AC analysis, which depends on the parameters calculated in the studio in DC, it is necessary to calculate gain, input impedance and output impedance of the circuit. Index Terms–Common collector, common emitter, gain, impedance, point Q, polarization. I. INTRODUCIÓN na de las principales aplicaciones del transistor BJT, es la Uamplificación de señales, es decir, en un circuito que contiene dicho componente, al inyectarle una señal, la salida puede ser amplificada; dichas señales pueden ser voltajes o corrientes. La amplificación, cuyo valor está contenido en la ganancia, depende básicamente de dos condiciones o situaciones; una de ellas es la ubicación del punto Q o punto de operación del transistor, si éste es ubicado de tal manera que se garantice la máxima excursión, entonces la amplificación es la óptima; caso contrario ocurre cuando el punto Q está cercano a la región de corte o región de saturación, pues en estas zonas, el transistor se comporta como interruptor, mas no como amplificador. La otra situación es la configuración misma del transistor, es decir, si está configurado como emisor común, colector común o base común, pues se pueden tener ganancias positivas, negativas ó unitarias; vale la pena aclarar que el signo en una ganancia indica el desfase entre la señal de entrada y la señal de salida. En cuanto a la ubicación del punto Q, se procede a hacer un análisis en DC, este análisis implica la obtención de valores de componentes meramente resistivos, una vez hecho este análisis se pasa a AC, donde el transistor es considerado con un modelo aproximado; en el presente informe este modelo, es el modelo re y permite el cálculo de expresiones para la ganancia, impedancia de entrada e impedancia de salida. A. Procedimiento Teórico. Un parámetro esencial para el análisis de la amplificación, o en general para el comportamiento del transistor, es el parámetro β (beta), que es la razón entre la corriente que pasa por el colector y la corriente que circula por la base. Βeta puede ser calculado a partir de un trazador de curvas o una simulación, por lo tanto para estimar dicho parámetro, recurrimos a SPICE. Considerar el circuito que se muestra en la Figura 1. R1 100k Q1 2N2222 VBB VCC 0Vdc 0Vdc 0 0 Figura 1. Circuito para la obtención de β. 0 Práctica 03 – 05 – Septiembre 23/ 2013 – periodo 2013/03 En el circuito de la Figura 1, tenemos la siguiente ecuación: (1) Procedemos a hacer un barrido en DC, de tal modo que VCC varíe de 0V hasta 10V y VBB de 2,7V hasta 10,7V, pues si VBE es igual a 0,7V, entonces IB varía entre 20uA y 100Ua. La figura 2 muestra las curvas características del transistor para el barrido antes indicado. El voltaje colector-emisor se escoge de 5V para garantizar la máxima excursión y suponiendo que el voltaje de saturación es 0V. Procedemos a analizar el circuito emisor común, cuyo esquema se muestra en la Figura 3 10Vdc VCC R1 RC 0 C2 C1 2N2222 Q1 5u RL 5u VS 0 RE 0 C3 10u R2 0 Figura 3. Esquema de la configuración emisor común. Para el análisis, podemos simplificar el circuito, obteniendo lo siguiente (ver Figura 3): Figura 2. Curvas características del transistor. De la Figura 2, obtenemos lo siguiente contenido en la Tabla 1: TABLA 1. Determinación de beta. IC (mA) IB (mA) 2 5 7 10 12 RC RTH VTH Q2 BETA 0,02 0,04 0,06 0,08 0,1 2N2222 0 100 125 116,67 125 120 RE 0 Según la Tabla 1 y las especificaciones en la hoja de datos del transistor utilizado, estimamos que β es igual a 125. Figura 4. Simplificación del circuito emisor común para el análisis en DC. Vale la pena aclarar que para el análisis en DC, los capacitores se han sustituido por circuitos abiertos. Tras aplicar las leyes básicas de circuitos obtenemos lo siguiente en la malla de entrada: Los parámetros fijos de diseño se resumen en la Tabla 2. TABLA 2. Parámetros de diseño. CORRIENTE DEL COLECTOR GANANCIA VOLTAJE DE POLARIZACIÓN GANANCIA DE CORRIENTE VOLTAJE BASE-EMISOR VOLTAJE COLECTOREMISOR (2) IC (A) AV 0,12 60 VCC (V) BETA (β) VBE(V) 10 125 0,7 VCE(V) 5 (3) (4) En la malla de salida obtenemos la siguiente ecuación: Práctica 03 – 05 – Septiembre 23/ 2013 – periodo 2013/03 consideramos el modelo re en AC para el transistor. Los modelos para el transistor en emisor común y colector común se muestran en las figuras 6 y 7 respectivamente: (5) Reemplazando los valores recolectados de la Tabla 2, obteniendo la siguiente ecuación de diseño: + (6) BIb RC Por lo tanto si escogemos =24Ω, entonces =18Ω aproximadamente, estos valores nos dan la información suficiente para la localización del punto Q. La Figura 5 muestra la recta de carga y la ubicación del punto Q. RL Bre + VO - VI - R2 0 RECTA DE CARGA PARA EL TRANSISTOR R1 0 0 0 0 250 RECTA DE CARGA PUNTO Q Figura 6. Modelo re en AC para el transistor en emisor común. 200 IC (mA) 150 BIb RC Bre + 100 VI RL - + RE 50 R2 VO R1 - 0 0 1 2 3 4 5 VCE (V) 6 7 8 9 0 10 0 0 0 0 Figura 5. Recta de carga y punto Q. Figura 7. Modelo re en AC para el transistor en colector común. A partir de las ecuaciones (1), (2) y (3) podemos obtener una relación directa entre R1 Y R2, si hacemos entonces que R2=600Ω, entonces R1=1KΩ aproximadamente. re se determina a partir de re=26mv/Ie, que en nuestro diseño se aproxima al valor de 0,22Ω, en cuanto a las ganancias tenemos lo siguiente: Este análisis en DC también es válido para la configuración colector común, cuyo esquema se muestra en la Figura 6. 10Vdc VCC R1 (7) La ecuación (7) es una expresión para la ganancia en la configuración emisor común; para la configuración colector común se tiene lo siguiente: RC 0 C1 2N2222 Q1 (8) C5 5u VS RE C3 0 RL R2 0 0 Figura 6. Configuración colector común. Para determinar expresiones para la ganancia (Av), la impedancia de entrada (ZI), la impedancia de salida (ZO), Como el valor de re es muy pequeño entonces la ganancia en la configuración colector común es aproximadamente la unidad, es decir es independiente de RL. De la ecuación (7) ajustando la ganancia a 60, obtenemos que RL=47Ω. A partir de los resultados obtenidos, podemos inferir que si conectamos ambas configuraciones en cascada, obtenemos una ganancia de 60. Práctica 03 – 05 – Septiembre 23/ 2013 – periodo 2013/03 Las impedancias en la configuración en emisor común son tales que: || || (9) Para los valores asignados, entonces la impedancia de entrada es ZI=25,62Ω, y la impedancia de salida es aproximadamente igual a RC, por lo tanto ZO=18Ω. En cuanto a la configuración en colector común tenemos lo siguiente: || || ( || || || ) (10) (11) Obteniendo los valores teóricos: ZI=331Ω aproximadamente y ZO=2,84Ω.. B. Simulación. Para proceder con la simulación, vale la pena aclarar, que debemos considerar tanto un modelo real como un modelo ideal del transistor BJT. En el modelo ideal, no se consideran efectos resistivos que presenta el dispositivo internamente, ambos modelos se exponen a continuación, teniendo presente además que estos modelos son ajustados según las hojas de especificaciones y los resultados obtenidos en las curvas características del transistor: Figura 8. Amplitud de la señal de salida, tras el barrido en frecuencia. A partir de la Figura 8, podemos observar, que la ganancia es 20, pues la máxima amplitud que se muestra es de 20mV, y las frecuencias de corte son aproximadamente 10KHz y 10MHz. Ahora se procede al dominio del tiempo y se pone a operar la señal de entrada a 10KHz y 200Hz con amplitud de 100mV, aunque ahora se considera un modelo ideal para el transistor. Las Figuras 9 y 10, exponen los resultados. Señal de entrada en color verde y señal de salida en color azul. MODELO “REAL” DEL TRANSISTOR. .model Q2N2222 NPN(Is=14.34f Xti=3 Eg=1.11 Vaf=74.03 Bf=125 Ne=1.307 +Ise=14.34f Ikf=.2847 Xtb=1.5 Br=6.092 Nc=2 Isc=0 Ikr=0 Rc=1+Cjc=7.306p Mjc=.3416 Vjc=.75 Fc=.5 Cje=22.01p Mje=.377 Vje=.75+Tr=46.91n Tf=411.1p Itf=.6 Vtf=1.7 Xtf=3 Rb=10) *National pid=19 case=TO18 *88-09-07 bam creation 100mV 50mV 0V -50mV MODELO “IDEAL” DEL TRANSISTOR”. -100mV 0s .model Q2N2222 NPN(Is=14.34f Xti=3 Eg=1.11 Vaf=74.03 Bf=125) *National pid=19 case=TO18 *88-09-07 bam creation Para el barrido en frecuencia, recurrimos al modelo “real” del transistor, donde la frecuencia de la señal de salida se hace variar y su amplitud se fija a 1mV. La Figura 8 muestra lo obtenido para la configuración emisor común. V(C6:2) 2ms V(V2:+) 4ms 6ms 8ms 10ms 12ms 14ms Time Figura 9. Señales de entrada y salida con frecuencia de 200Hz. 16ms 18ms 20ms Práctica 03 – 05 – Septiembre 23/ 2013 – periodo 2013/03 800mV 400mV 0V -400mV -800mV 0s 20us 40us V(C6:2) V(V2:+) 60us 80us 100us 120us 140us 160us 180us 200us 220us 240us 260us 280us 300us Time Figura 10. Señales de entrada y de salida con la frecuencia ajustada a 10Khz. A partir de las Figuras 9 y 10 vemos que cuando la frecuencia es ajustada a 200Hz no hay ganancia, pues la salida es menor a 100mV, y cuando la frecuencia es de 10KHz, hay ganancia, pues el valor pico está entre 600 y 800mV como es de esperarse, pues la ganancia es de 60. Para la configuración colector común, ajustamos la frecuencia de la señal de entrada en 10KHz, como es de esperarse, la ganancia en esta configuración es unitaria, por lo que no hay amplificación. La Figura 11 muestra lo obtenido (señal de entrada en color verde y señal de salida en color rojo). Figura 11. Señales de entrada y salida en la configuración colector común. Cuando conectamos en casacada ambas configuraciones encontramos que la ganancia es igual al de la configuración en emisor común. C. Experimento. El expimento consistió en montar ambas configuraciones, con los parámetros calculados en el análisis teórico, y observar la ganancia, variando la frecuencia en la señal de salida según el diagrama en la Figura 8. El valor de los capacitores, son elegidos casi de manera aleatoria, obviamente de igual valor que los utilizados en las simulaciones, estos valores definen un ancho de banda en la consideración de la ganancia en la señal de salida. II. RESULTADOS EXPERIMENTALES Los resultados experimentales se recopilan en una serie de fotografías tomadas durante la práctica. Para el montaje en cascada de ambas configuraciones, obtenemos similares resultados que en la configuración emisor común. Práctica 03 – 05 – Septiembre 23/ 2013 – periodo 2013/03 CONFIGURACIÓN EN EMISOR COMÚN. (Señal de entrada en color azul y señal de salida en color amarillo. La amplitud de la señal de entrada es de 0,1V) lo que se varía es la frecuencia. Frecuencia=10KHz Frecuencia=5KHz Figura 14. Señales de entrada y salida a 10KHz. Figura 12. Señales de entrada y salida a 5KHz. Frecuencia=200Hz Frecuencia=7KHz Figura 13. Señales de entrada y salida a 7KHz. Figura 15. Señales de entrada y salida a 200Hz. Práctica 03 – 05 – Septiembre 23/ 2013 – periodo 2013/03 Frecuencia=700Hz Frecuencia=500Hz Figura 16. Señales de entrada y salida a 700Hz. CONFIGURACIÓN EN COLECTOR COMÚN. (Señal de entrada en color azul y señal de salida en color amarillo. La amplitud de la señal de entrada es de 1V) lo que se varía es la frecuencia. Figura 18. Señal de salida a 500Hz. Frecuencia=1MHz Frecuencia=10KHz Figura 17. Señales de entrada y salida a 1MHz. Figura 19. Señal de salida a 10KHz. En cuanto a la determinación de la tensión Early, recurrimos a SPICE, La figura 20 muestra lo simulado. Práctica 03 – 05 – Septiembre 23/ 2013 – periodo 2013/03 respectivamente, muestran una ganancia unitaria en la señal de salida, la cual se encuentra en fase con la señal de entrada. 40mA Según las gráficas 17, 18 y 19 tomadas por el osciloscopio, para distintos valores de frecuencia la ganancia en la señal de salida no cambia. IC VS VCE CONCLUSIONES 30mA Los errores obtenidos se deben a que no se usaron los valores de las resistencias y del capacitor calculados, y se usaron resistencias y capacitores aproximados que se encontraban en el laboratorio. 20mA 10mA VA 0A -80V -70V -60V -50V -40V -30V -20V -10V 0V 10V 20V 30V 40V 50V 60V 70V 80V I(Q1:c) V_VCC Figura 20. Determinación de la tensión Early. De la Figura 20, podemos inferir que la tensión Early es aproximadamente 74V, pues las curvas características del transistor, si se extienden como rectas, convergen a este valor de VCE. III. COMPARACIÓN DE RESULTADOS De acuerdo con las gráficas 15 y 16 no se observa una ganancia mayor a 1 para las frecuencias menores a 1KHz, lo que ocurre de manera similar en la simulación según la gráfica 8. En las gráficas 12, 13 y 14 nos damos cuenta que empieza a haber una ganancia mayor que aumenta a medida que tambin aumenta la frecuencia. Pero a partir de 10KHz la ganacia en la señal de salida se mantiene igual, hasta que la frecuencia llega a ser de 1MHz, a partir de dicha frecuencia la señal de salida empieza a atenuarse, lo que ocurre de manera similar en la simulación según la gráfica 8. En las gráficas de simulación y las experimentales tomadas por el osciloscopio ocurre que la señal de salida con la de entrada se encuentra en contrafase con la configuración emisor común. En la configuración colector común, las gráficas 11 y 17 correspondientes a la simulación y al resultado experimental A partir de los resultados obtenidos con respecto a la configuración emisor común, donde obtenemos los esperados, por ejemplo a 10KHz, donde la ganancia debe ser la máxima y de un valor aproximado de 60, y en general para ambas configuraciones; podemos inferir que la estimación del beta del transistor es una buena aproximación a la real, pues con el beta estimado, el análisis teórico no presenta considerables diferencias con los resultados experimentales ó que la estimación del beta no es tan exacta, sino más bien que la polarización montada para el transistor presenta gran estabilidad, es decir que para variaciones importantes para beta, los parámetros que rigen el comportamiento del BJT no se varían de manera importante. Los valores escogidos para los capacitores definen un ancho de banda para el rango de frecuencias en las que la amplificación es la máxima, según su conexión dentro de una configuración específica. Se pudo ratificar experimentalmente, que no a todas las frecuencias, la amplificación es la misma. Aunque experimentalmente no se verifica la ubicación del punto Q(aunque se pudo haber medido la corriente por el colector y el voltaje colector-emisor), podemos inferir que este punto no está cercano a la región de corte o a la saturación, pues las señales obtenidas no mostraban distorsión. Experimentalmente, se ratifica el modelo re para el transistor BJT en AC, pues tras el análisis teórico, el comportamiento real del componente se aproxima de manera efectiva. Práctica 03 – 05 – Septiembre 23/ 2013 – periodo 2013/03 REFERENCIAS [1] [2] Malik, N. Circuitos Electronicos. Análisis, Simulación Y Diseño. Prentice Hall, 1996 Boylestad, N. Electronica: Circuitos y Dispositivos. Prentice Hall Latinoamerica. 2005 Eric Santiago Granda Tobón: 1037620403, 04, Ingeniería Eléctrica, 6 Daniel Ramírez Castañeda:1042064102, 04, Ingeniería Eléctrica, 6.