Always leading the pack

SISTEMAS PROGRAMABLE

Laboratorio Time

DL3155M24HC11

DL3155M24HC11

SISTEMAS PROGRAMABLES

2

DL3155M24HC11

INDICE

GUIA TEORICA:

UNIDAD

1.

Fundamentos de microcomputadoras.

2.

Arquitectura del microprocesador.

3.

Conjunto de instrucciones.

4.

Operaciones con la pila.

5.

Operaciones de entrada y salida.

6.

Programación de la tarjeta DL3155M24HC11.

3

DL3155M24HC11

4

DL3155M24HC11

UNIDAD 1

FUNDAMENTOS DE

MICROCOMPUTADORAS

5

DL3155M24HC11

CONTENIDO

1.1 INTRODUCCIÓN

1.2 TÉRMINO MICROCONTROLADOR

1.3 FUNCIONAMIENTO DEL MICROCONTROLADOR

6

DL3155M24HC11

1.1 INTRODUCCION

Un microprocesador es un circuito electrónico muy complejo responsable de las operaciones

aritméticas y lógicas programadas en una microcomputadora. Esta constituido de cientos de

miles de transistores microscópicos encapsulados dentro de un delgado trozo(chip) de silicio

que no es mayor de algunos milímetros cuadrados. Dicho trozo, está alambrado en un circuito

integrado (chip) normalmente de 40 o más interconexiones entre el CI y el chip.

Los miles de transistores que componen el microprocesador están configurados para formar

diferentes clases de circuitos dentro del chip. Desde el punto de vista, aprendizaje para la

operación del microprocesador, los circuitos más importantes son los registros, contadores y

decodificadores. En esta unidad, usted aprenderá como esos circuitos trabajan juntos para

llevar a cabo tareas simples, pero útiles.

Además de los circuitos estándar, característicos de los microprocesadores, el MC68HC11 que

usted aprenderá a programar, contiene otros circuitos. Se incluye internamente Memoria de

Sólo Lectura (ROM), Memoria de Acceso Aleatorio (RAM), Memoria de Sólo Lectura

Programable y Borrable Eléctricamente (EEPROM), una Interface Periférica Serial (SPI), una

Interface de Comunicaciones Serie (SCI), un Convertidor Analógico-Digital (A/D), Sistema de

Temporización(timer´s) y algunos otros usados principalmente en aplicaciones de interface.

7

DL3155M24HC11

1.2 EL TERMINO MICROCONTROLADOR

Un microprocesador es un dispositivo lógico que es usado en sistemas electrónicos digitales.

Pero, previamente estableceremos una diferencia entre microprocesador y microcontrolador(de

acuerdo a sus características podemos decir que también es llamado una

microcomputadora).

La unidad microprocesadora o CPU, es un elemento lógico complejo que lleva a cabo

operaciones aritmético/lógicas y de control. Comúnmente esta encapsulado en un solo circuito

integrado CI.

Un microcontrolador contiene un microprocesador, además de otros circuitos, tales como

dispositivos de memoria para almacenamiento de información, adaptadores de interface para

conectarse a señales externas y un reloj que actúa como temporizador maestro del sistema.

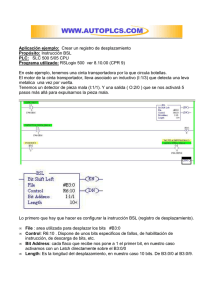

La figura 1-1 muestra un microcontrolador(recuerde que se menciono que tambien es llamada,

una microcomputadora) con los dispositivos basicos he interconectados entre internamente,

aplicandosele solo una señal de reloj.

Reloj

Unidad

Microprocesadora

memoria

memoria

Interfaz

microcomputadora

I/O

Dispositivo de

entrada/salida

Fig. 1-1. Arquitectura básica de un Microcontrolador(microcomputadora).

La microcomputadora está integrada por los componentes ubicados dentro de la línea

punteada. El chip MC68HC11 usado en este curso, contiene esas características en un solo

chip de modo que se hace referencia a una unidad microcomputadora o CPU.

Todo lo situado fuera de la línea punteada en la figura 1-1 se considera como la parte que

permite la interfaz con señales de entrada y salida externas, todas las microcomputadoras

deben tener algún medio de comunicarse así. La información recibida por la

microcomputadora, que procede de señales externas, se le conoce como datos de

entrada(input data). La información transmitida al exterior se considera como datos de

salida(output data). La información puede llegar de dispositivos semejantes a lectoras de cinta

de papel, transductores de varios tipos, switches mecánicos, teclados o aún de otras

computadoras.

8

DL3155M24HC11

Concepto De Programa Almacenado

Una microcomputadora es capaz de llevar a cabo muchas instrucciones distintas. Puede sumar

y restar números, llevar a cabo operaciones lógicas, etc. Puede leer información desde un

dispositivo de entrada y transmitir información a un dispositivo de salida. De hecho, depende

del microprocesador usado, el numero de instrucciones que el micro puede ejecutar pueden ser

100 o más según sea el caso. Más aún para conformar operaciones mucho más complejas se

puede combinar dos o más operaciones individuales.

La compuadora solo recibe instrucciones y las ejecuta. Se esclarece la aplicación y se le dan

las operaciones y el orden en que va a llevarlas a cabo. Dichas operaciones se les llama:

instrucciones. Las más comunes son la de suma, sustracción, cargar registro índice, almacenar

acumulador, de paro, etc., etc.

Un grupo de instrucciones que permiten a la computadora efectuar una tarea específica, se

llama programa. Y es el programador quién escribe dichas instrucciones.. Generalmente, la

longitud de un programa es proporcional a la complejidad de la tarea que la computadora debe

efectuar. Un programa para sumar una lista de números requiere sólo una docena de

instrucciones. Por otro lado, un programa para controlar todos los semáforos de una ciudad

chica puede requerir miles de instrucciones.

Una computadora es frecuentemente comparada con una calculadora, donde se le dice qué

hacer desde el teclado. Aún calculadoras baratas pueden efectuar algunas operaciones

comparables con instrucciones de computadora. Oprimiendo las teclas correctas, usted puede

instruir a la calculadora para sumar, restar, multiplicar, dividir y limpiar la pantalla. Con la

calculadora, usted puede sumar una lista de números tan rápidamente como pueda introducir

los números y las instrucciones. En donde, la operación está limitada por la velocidad y

precisión del operador.

Desde el principio, los diseñadores de computadoras reconocieron que es el operador que en

ocasiones hace lento el proceso de cómputo. Para solucionar esto fue desarrollado el concepto

de programa almacenado. Usando esta aproximación, el programa es almacenado en la

memoria de la computadora. Supongamos por ejemplo, que se tienen 20 números que serán

manipulados por un programa que consta de 100 instrucciones. Supongamos ahora que se

generarán 10 respuestas en el proceso.

Antes que inicie cualquier proceso, el programa de 100 instrucciones más los 20 números son

cargados en memoria. Seguidamente, se apartan 10 localidades de memoria reservadas para

las respuestas. Sólo entonces se permite que la computadora ejecute el programa. El tiempo

de ejecución puede ser menor a un milisegundo. Compare este tiempo con el que podría tomar

introducir manualmente las instrucciones y los números, uno a la vez mientras la computadora

está corriendo. Esta operación automática es una característica que distingue a la computadora

de la simple y no programable calculadora.

Palabras de Computadora

En terminología de computadoras, una palabra es un grupo de dígitos binarios que pueden

ocupar una localidad de almacenamiento. Aunque la palabra está formada por dígitos

9

DL3155M24HC11

individuales, la computadora los maneja como una unidad. Así, la palabra es la unidad de

información fundamental usada por la computadora.

Una palabra puede ser un número binario que es manejado como dato o puede ser una

instrucción que dice a la computadora qué operación llevar a cabo. Puede ser un carácter

ASCII representando una letra del alfabeto. Finalmente, una palabra puede ser una dirección

que dice a la computadora dónde localizar un dato.

Longitud de Palabra

Una de las más importantes características de cualquier microprocesador es qué la longitud de

palabra pueda manejarse, esto se refiere a la longitud en bits de la unidad fundamental de

información.

Aunque actualmente existen muchos microprocesadores de 16 y 32 bits, una longitud de

palabra muy común continúa siendo de 8 bits. En esas unidades, los números, direcciones,

instrucciones y datos son representados por números binarios de 8 bits. El número binario más

pequeño es 0000 00002 o 0016; el mayor es 1111 11112 o FF1 6. En decimal, este rango es

desde 0 hasta 25510. Así, un número binario de 8 bits puede tener uno de 256 10 valores.

Una palabra de 8 bits puede especificar números positivos entre 0 y 25510. O, si la palabra de 8

bits es una instrucción, puede especificar 25610 posibles operaciones. Es también posible que

la palabra de 8 bits represente un carácter ASCII. En éste caso puede ser una letra del

alfabeto, signo de puntuación o numero. Como se puede ver, la palabra de 8 bits puede

representar cosas diferentes, dependiendo de cómo es interpretada. El programador debe

asegurarse de que un carácter ASCII o número binario no sea interpretado como una

instrucción.

Aunque la longitud de palabra de 8 bits es muy popular, se emplean cada vez con mayor

frecuencia las de 16 y 32 bits y, eventualmente, la de 4 bits por el bajo costo del dispositivo.

También en los nuevos microcontroladores de tipo RISC, se emplean longitudes de 12 y 14

bits. Las longitudes mayores permiten trabajar con números grandes usando una sola palabra.

Por ejemplo, una palabra de 16 bits puede representar números hasta 6553610. Sin embargo,

esta capacidad agrega mayor complejidad al microprocesador. De cualquier modo,

restringiremos nuestra discusión a las unidades de 8 bits.

Debe ser puntualizado que la longitud de palabra de 8 bits no significa no poder manejar mas

que números debajo de 25610. Pero en caso de ser necesario, se deberán usar dos o más

palabras para representar números grandes.

La palabra de 8 bits define el tamaño de muchos componentes diferentes en el sistema

microprocesador. Por ejemplo, muchos registros importantes tendrán 8 bits de capacidad.

La memoria deberá ser capaz de mantener números grandes con palabras de 8 bits; y el bus

empleado para transferir palabras de datos consistirá en conductores paralelos de 8.

Aun los microprocesadores de 16 bits usan segmentos de datos de 8 bits, en muchas

aplicaciones; como ejemplo, las entradas de teleimpresores frecuentemente consisten de

caracteres ASCII de 8 bits. Para distinguir esos segmentos de 8 bits de información, de los de

16 bits o mayores, hay un termino de uso general: el byte, que es un grupo de 8 bits, manejado

10

DL3155M24HC11

como una sola unidad. Así, en los microprocesadores de 8 bits, una palabra consiste de un

byte, en tanto que en los de 16 bits, consiste en 2 bytes. La figura 1-2 ilustra estos puntos.

Fig. 1-2 Palabras y bytes

La figura 1-2 también muestra como están numerados los bits que componen la palabra de

computadora. El bit menos significativo (LSB) esta a la derecha, mientras que el bit más

significativo (MSB) a la izquierda. En la palabra de 8 bits, estos se numeran del 0 al 7, de

derecha a izquierda; en la palabra de 16 bits, la numeración va del 0 al 15, en el mismo

sentido. Los 8 bits de la derecha son llamados byte de orden bajo y los de la izquierda byte de

orden alto.

11

DL3155M24HC11

1.3 FUNCINAMIENTO DEL MICROCONTROLADOR

El microprocesador puede tener una docena o más de registros que varían en tamaño desde 1

bit hasta 16 bits. Puede tener docenas de instrucciones, muchas de las cuales pueden

implementarse de diferentes maneras. Puede tener buses de datos, direcciones y control. En

suma, el microprocesador puede parecer desde afuera, complicado para programarse por ser

un micro desarrollado.

Un diagrama de bloques de una microcomputadora básica se muestra en la figura 1-3, la cual

muestra un microprocesador, la memoria y la circuitería de E/S. Por simplicidad, ignoraremos

los circuitos de E/S en ésta unidad. Podemos hacer esto suponiendo que el programa y los

datos se hallan en memoria y que los resultados se mantendrán en registros o en memoria. Al

final de este curso, se esclarecerá el movimiento de datos externos desde o hacia el micro,

dichos procedimientos se estudiarán en una de las ultimas unidades. Esto nos permitirá

concentrarnos en el microprocesador y la memoria.

Fig. 1-3. La Microcomputadora Básica

12

DL3155M24HC11

La unidad Microprocesadora

La unidad microprocesadora es mostrada en detalle en la figura 1-4. Por simplicidad, sólo se

incluyen los principales registros y circuitos. En nuestra unidad elemental, muchos de los

contadores, registros y buses son de 8 bits, por lo que pueden acomodar palabras de ese

tamaño.

CLOCK

AND

CONTROL

LINES

Fig. 1-4. Un microprocesador Elemental

13

DL3155M24HC11

Uno de los circuitos más importantes en el procesador es la unidad lógica-aritmética (ALU). Su

propósito es llevar a cabo operaciones lógicas o aritméticas sobre los datos que le son

entregados. La ALU tiene dos entradas principales. Una viene desde un registro llamado

acumulador, y la otra viene desde el registro de datos. La ALU puede sumar los dos datos de

entrada juntos, o puede restar una de la otra. También puede llevar a cabo algunas

operaciones lógicas, las cuales discutiremos en unidades posteriores. La operación que ejecute

la ALU está determinada por señales en las varias líneas de control.

Generalmente, la ALU recibe dos números binarios de 8 bits desde el acumulador y el registro

de datos como se ilustra en la figura 1-5A. Ya que se ejecuta alguna operación sobre estas

palabras de datos, las dos entradas se llaman operandos.

Fig. 1-5. Unidad Lógica Aritmética

14

DL3155M24HC11

Los dos operandos pueden ser sumados, restados o comparados en alguna forma, y el

resultado de la operación vuelto a almacenar en el acumulador. Por ejemplo, suponga que se

van a sumar dos números (7 y 9). Antes que los números puedan ser sumados, un operando

(9) es colocado en el acumulador, el otro (7) es colocado en el registro de datos. Se activa la

línea de control correspondiente para implementar la operación de suma. La ALU suma los dos

números, enviando su suma (1610) a la salida. La figura 1-5B muestra el proceso; la suma es

almacenada en el acumulador, reemplazando el operando que originalmente se hallaba ahí.

Nótese que todos los números están en forma binaria.

El acumulador es el más útil de los registros. Durante las operaciones aritméticas y lógicas

lleva a cabo una función dual. Antes de la operación, guarda uno de los operandos. Después

de la operación, guarda la suma resultante, diferencia o respuesta lógica. El acumulador recibe

algunas instrucciones en cada microprocesador. Por ejemplo, la instrucción “cargar

acumulador” causa que el contenido de alguna localidad específica de memoria sea transferida

al acumulador. La instrucción “almacenar acumulador” causa que el contenido del acumulador

sea almacenado en alguna localidad específica de memoria.

El registro de datos es una localidad temporal de almacenamiento para los datos que van o

vienen sobre el bus de datos. Por ejemplo, guarda una instrucción mientras es decodificada.

También, guarda un byte de datos mientras la palabra es almacenada en memoria.

La MPU también contiene algunos otros registros y circuitos importantes: el registro de

direcciones, el contador de programa, el decodificador de instrucciones y el controladorsecuencial. Estos son mostrados en la figura 1-4.

El registro de direcciones es otra localidad de almacenamiento temporal. Guarda la dirección

de la localidad de memoria o dispositivo de E/S que es usada en la operación que se está

llevando a cabo.

El contador de programa controla la secuencia en la que las instrucciones serán ejecutadas en

un programa. Normalmente, hace esto contando en secuencia 0, 1, 2, 3, etc.

En un instante dado, la cuenta indica la localidad en memoria de la que debe tomarse el

siguiente byte de información.

El decodificador de instrucciones. Después que una instrucción es sacada de la memoria y

colocada en el registro de datos, la instrucción es decodificada por éste circuito. El

decodificador examina el código de 8 bits y decide que operación debe ser llevada a cabo.

El controlador-secuenciador produce una variedad de señales de control para ejecutar la

instrucción. Ya que cada instrucción es diferente, se produce una combinación diferente de

señales de control para cada instrucción. Este circuito determina la secuencia de eventos,

necesaria para completar la operación descrita por la instrucción.

Más tarde verá como estos circuitos trabajan juntos para ejecutar programas simples. Primero,

demos en vistazo a la memoria de nuestra microcomputadora.

15

DL3155M24HC11

MEMORIA

Un diagrama simplificado de memoria lectura/escritura de 256 palabras a 8 bits, que se usa

nuestra microcomputadora hipotética se muestra en la figura 1-6. La memoria consiste de 25610

localidades, cada una de las cuales puede almacenar una palabra de 8 bits. Este tamaño de

memoria es referido frecuentemente como 256 X 8. Una memoria de lectura/escritura es

aquella en la que los datos pueden ser escritos y leídos con igual facilidad.

Fig. 1-6. Memoria de Acceso Aleatorio

(RAM)

Dos buses y un número de líneas de control conectan la memoria con la unidad del

microprocesador. El bus de direcciones puede contener un número binario de 8 bits, que puede

especificarse como 25610 localidades, desde la MPU al decodificador de direcciones de

memoria. Cada localidad tiene asignado un número único llamado dirección. La primera

localidad tiene la dirección 0. La última localidad tiene la dirección 25510, 1111 1111 en binario

o FF en hexadecimal. Una localidad específica es seleccionada colocando su dirección de 8

bits en el bus de direcciones. El decodificador de direcciones, después de decodificar el

número de 8 bits, selecciona la localidad de memoria apropiada.

La memoria también recibe una señal de control de la MPU. Esta señal dice a la memoria que

operación llevar a cabo. Una señal READ indica que la localidad seleccionada será leída. Esto

implica que el número de 8 bits contenido en la localidad seleccionada debe ser colocado en el

bus de datos, donde puede ser transferido a la MPU.

16

DL3155M24HC11

El procedimiento se ilustra en la figura 1-7. Considere que la MPU va a leer el contenido de la

localidad de memoria 0416. Suponga que el número almacenado ahí es 9716.

Primero, la MPU coloca la dirección 0416 en el bus de dirección. El decodificador reconoce la

dirección y selecciona la localidad de memoria apropiada. Segundo, la MPU envía una señal

READ a la memoria, indicándole que el contenido de la localidad seleccionada esta siendo

colocado en el bus de datos. Tercero, la memoria responde colocando el número 971 6 en el bus

de datos. La MPU puede entonces tomar el número y usarlo como sea necesario.

Fig. 1-7. Leyendo desde memoria

Debe señalarse que el proceso de lectura de memoria no altera el contenido de la localidad

leída. Esto es, el número 9716 permanece en la localidad de memoria 04 después de la

operación de lectura. Esta característica se conoce como lectura no destructiva (NDRO). Es un

rasgo importante puesto que permite leer el dato cuanto sea necesario.

La MPU también puede llevar a cabo la operación de escritura, WRITE. Este procedimiento se

ilustra en la figura 1-8. Durante esta operación, una palabra de datos es tomada del bus de

datos y colocada en la localidad seleccionada. Por ejemplo, veamos como la MPU almacena el

número 5216 en la localidad 03. Primero, la MPU coloca la dirección 03 en el bus de

direcciones. El decodificador responde seleccionando la localidad de memoria 03. Segundo, la

MPU coloca el número 5216 en el bus de datos. Tercero, la MPU envía la señal WRITE.

17

DL3155M24HC11

La memoria responde almacenando el número presente en el bus de datos en la localidad

seleccionada. Esto es, 5216 es almacenado en la localidad 03. El contenido previo se pierde al

haber sobre-escritura.

Fig. 1-8. Escribiendo en memoria

El nombre aceptado para éste tipo de memoria es el de Memoria de Acceso Aleatorio (RAM).

“Acceso Aleatorio” significa que todas las localidades de la memoria son igualmente accesibles.

Sin embargo, en años recientes, la RAM ha llegado a ser memoria de acceso aleatorio de

lectura/escritura. Como usted verá más adelante, hay otro tipo de memoria llamado memoria de

sólo lectura (ROM). También es accesible aleatoriamente, pero no tiene la capacidad de

escritura. De esta manera es llamada ROM, pero nunca RAM.

Secuencia de Búsqueda – Ejecución

Cuando la microcomputadora ejecuta un programa, este lleva una secuencia fundamental que

es repetida una y otra vez. Recuerde que un programa consiste de instrucciones que dicen a la

microcomputadora que operaciones efectuar exactamente. Estas instrucciones deben ser

almacenadas ordenadamente en la memoria. Deben ser extraídas de la memoria, una cada

vez, por la MPU. Entonces pueden ser ejecutadas.

La operación de la microcomputadora puede ser dividida en dos fases, como se muestra en la

Figura 1-9. Cuando se enciende el microprocesador entra a la fase de búsqueda. Durante esta

fase, una instrucción es tomada de la memoria y decodificada por la MPU.

Una vez que la instrucción es decodificada, la MPU conmuta a la fase de ejecución. En esta

fase, la MPU efectúa la operación indicada por la instrucción.

18

DL3155M24HC11

Fig. 1-9. Secuencia de busqueda-ejecución

La fase de búsqueda siempre consiste en la misma serie de operaciones. Por ello siempre

toma el mismo lapso de tiempo. Sin embargo, la fase de ejecución puede consistir de

diferentes secuencias de eventos, dependiendo de que tipo de instrucción se ejecuta. Así, la

fase de ejecución puede variar considerablemente de una instrucción a otra.

UN PROGRAMA DE MUESTRA.

Ahora que usted tiene una idea general de los registros y circuitos que se encuentran en una

microcomputadora, examinaremos cómo trabajan juntos, para ejecutar un programa sencillo.

Aquí estamos interesados sobre todo en la forma en que la microcomputadora opera; por lo

tanto, el programa será muy trivial.

Veamos como la computadora resuelve un problema como 7 + 10 =?. Aunque esto puede

parecer un problema increíblemente fácil, la computadora por si sola aún con todos sus

recursos, no tiene podrá resolverlo.

Antes que usted pueda escribir un programa debe saber que instrucciones están disponibles

entre usted y la computadora. Cada microprocesador tiene un conjunto de instrucciones.

Suponga que después de examinar dicho conjunto, usted decide que son necesarias tres

instrucciones para resolver el problema. Esas tres instrucciones y una descripción de qué

hacen se ilustran en la Figura 1-10.

NOMBRE

Cargar

acumulador

MNEMONICOS

OPCODE

LDA

1000 01102 o 8616

Add

ADD

1000 10112 o 8B16

Stop

STOP

1100 11112 o CF16

DESCRIPCION

Cargar el contenido de la siguiente

localidad de memoria en el acumulador

Sumar el contenido de la siguiente

localidad de memoria al contenido del

acumulador. Deja el resultado en el

acumulador

Detiene todas las operaciones

Fig. 1-10. Instrucciones usadas para el programa ejemplo.

La primera columna de la tabla, nos da el nombre de la instrucción. Cuando escribimos

programas, no es conveniente incluir el nombre completo. Por esta razón, cada instrucción

tiene una abreviatura o ayuda a la memoria llamada mnemónico. Los mnemónicos se dan en

la segunda columna. La tercera columna es la de códigos de operación u opcodes. Este es el

19

DL3155M24HC11

número binario que la computadora y el programador usan para representar la instrucción. El

opcode se da tanto en forma binaria como en hexadecimal. La columna final describe

exactamente que operación es llevada a cabo cuando se ejecuta la instrucción. El tener

presente esta tabla, será muy útil ya que empleará estas instrucciones una y otra vez.

Suponga que desea sumar 7 a 1010 y dejar la suma en el acumulador. El programa es muy

elemental. Primero debe cargar 7 en el acumulador con la instrucción LDA. Enseguida, sumará

1010 al acumulador usando la instrucción ADD. Finalmente, detendrá la computadora con la

instrucción STOP.

Usando los mnemónicos y la representación decimal de los números a sumar, el programa se

verá así:

LDA 7

ADD 10

STOP

La microcomputadora no puede entender mnemónicos o números decimales, solo interpreta

números binarios. Así, debe escribir el programa como una secuencia de números binarios.

Puede hacer esto reemplazando cada mnemónico por su correspondiente opcode y cada

número decimal por su contra parte binaria.

Entonces:

LDA 7

se convierte en

1000 0110

opcode de la

Figura 1-10

0000 0111

representación

binaria de 7

ADD 10 se convierte en

1000 1011

opcode de la

Figura 1-10

0000 1010

representación

binaria de 1010

Y:

Finalmente,

STOP

se convierte en

1100 1111

opcode de la

Figura 1-10

Note que el programa consiste de tres instrucciones. Las primeras dos instrucciones tienen dos

partes: un opcode de 8 bits seguido de un operando de 8 bits. Los operandos son los números

que serán sumados (7 y 1010).

Recuerde que el microprocesador y la memoria trabajan con palabras de 8 bits o bytes. Puesto

que las dos primeras instrucciones consisten de 16 bits de información, deben ser divididas en

dos bytes de 8 bits antes de ser almacenadas en memoria. De esta manera, cuando el

programa es almacenado en memoria, se ve así:

1a. Instrucción

2a. Instrucción

1000 0110

0000 0111

1000 1011

0000 1010

Opcode de LDA

Operando (7)

Opcode de ADD

Operando (1010)

20

DL3155M24HC11

3a. Instrucción

1100 1111 Opcode de STOP

Se requieren cinco bytes de memoria. Puede almacenar estos cinco bytes de programa en

cualquier lugar de la memoria que desee. Suponiendo que los almacena en las primeras cinco

localidades, la memoria se vería como lo muestra la Figura 1-11.

Fig. 1-11. El programa en Memoria

Note que cada localidad de memoria tiene dos números binarios asociados consigo. Uno es su

dirección, el otro, su contenido. La dirección es fija. Se establece cuando se construye la

microcomputadora. Sin embargo, el contenido cambia cada vez que se almacenan nuevos

datos.

21

DL3155M24HC11

UNIDAD 2

ARQUITECTURA DEL

MICROCONTROLADOR

22

DL3155M24HC11

CONTENIDO

2.1 ARQUITECTURA DE MICROPROCESADORES

2.2 ARQUITECTURA DEL MC68HC11

2.3 MODELO DE PROGRAMACION DEL MC68HC11

2.4 DIAGRAMA A BLOQUES DEL MC68HC11

23

DL3155M24HC11

2.1 ARQUITECTURA DE MICROPROCESADORES

En el lenguaje coloquial de las computadoras, la palabra arquitectura se usa para describir el

estilo de construcción de la computadora, su tamaño y arreglo de registros, su configuración de

buses, etc.

La arquitectura de nuestro microprocesador hipotético se muestra por última vez en la Figura 21 Usted debe familiarizarse con esta arquitectura.

Fig. 2-1. Arquitectura del microprocesador hipotético

24

DL3155M24HC11

La única razón para mostrarle los detalles del modelo es darle una idea de lo que se halla en el

interior del circuito integrado. En un microprocesador moderno, la estructura interna es

frecuentemente tan compleja que al intentar analizarlo tan de cerca, nos llenaría en detalles,

creando confusión. Por esta razón, un modelo de programación se usa cuando se hace una

introducción a un microprocesador por vez primera. En el modelo de programación el énfasis va

más allá. Cualquier registro o circuito que no pueda ser controlado directamente por el

programador, simplemente se ignora. Por ejemplo, considere el registro de datos. No hay

instrucciones que den al programador control directo sobre ese registro. Esto es, no hay

instrucciones como Cargar el Registro de Datos, Almacenar el Registro de Datos, etc. Toda la

actividad del registro de datos, es controlada estrictamente por la MPU. Así, el programador

puede ignorar la existencia del registro. Ocurre lo mismo para el registro de direcciones, el

decodificador de instrucciones, el controlador-secuenciador, etc. Por lo tanto, el modelo de

programación de nuestra MPU hipotético puede representarse como en la Figura 2-2. Este

diagrama simple es suficiente para muchas aplicaciones de programación ya que muestra

todos los registros que pueden ser controlados directamente por el programa.

7

0

ACUMULADOR

7

0

CONTADOR DE PROGRAMA

N Z

V C

REGISTROS CODIGO DE CONDICIÓN

Fig. 2-2. Modelo de programación del MPU hipotético

Por definición, una microcontrolador consiste de una Unidad Central de Proceso (CPU),

Memoria de Solo Lectura (ROM), y circuitos de control y temporización. Puesto que el chip

MC68HC11 contiene estos y otros circuitos y características, será referido técnicamente como

la microcomputadora o MPU. Esto es así porque estamos interesados principalmente en la

programación de la CPU de la microcomputadora.

El 68HC11 es un miembro de la familia de microprocesadores MC6800, Motorola que comenzó

en 1974 con la introducción del MC6800. Otros miembros de esta familia incluyen a los

microprocesadores MC6801 y MC6808, además de otros. Una ventaja del concepto de “familia”

de chips, es que muchas de las instrucciones usadas para programar uno de los micros pueden

usarse para programar otros de la familia. En este sentido se dice que el 68HC11 es totalmente

compatible con los otros miembros de la familia. Por ello comparte similitudes de diseño y la

habilidad de entender y ejecutar instrucciones del conjunto de instrucciones de la familia 6800.

Como resultado de esta compatibilidad entre miembros de la familia, un programa en lenguaje

ensamblador escrito para otro microprocesador, correrá casi sin problemas en el MC68HC11; lo

que nos indica que las principales diferencias entre los miembros de la familia tienen que ver

más con el hardware. Esto incluye a los circuitos de soporte interconstruidos, como relojes,

temporizadores, memoria RAM, memoria ROM, memoria EEPROM, y otros circuitos de soporte

para la CPU. La CPU del 68HC11 es básicamente una extensión del diseño de la CPU

MC6800/6801. Además de la posibilidad de ejecutar las 71 instrucciones del MC6800, el

68HC11 tiene un mapa “paginado” de opcodes con un total de 91 nuevos opcodes. Finalmente,

puesto que muchos términos y conceptos que aprenderá se aplican a otros microprocesadores,

25

DL3155M24HC11

el aprendizaje de este material lo habilitará para entender y trabajar con una variedad de

microprocesadores de 8 bits, además del 68HC11.

2.2 ARQUITECTURA DEL MC68HC11

Los 68HC11 son fabricados por Motorola y se diseñan para atender las necesidades

particulares del un sistema y para aplicaciones especializadas de los mercados. Las

aplicaciones de sistemas con microprocesadores requieren un microprocesador que es

expandible y tiene una capacidad de direccionamiento relativamente grande. Por otro lado, las

aplicaciones especializadas (automóviles, aparatos, etc.) requieren un dispositivo single-chip

autónomo que contiene en su interior CPU, memoria, y capacidades de I/O. Dicho dispositivo

se llama a menudo un microprocesador single-chip.

Como usted está a punto de descubrir, los 68HC11 pueden configurarse de dos maneras

diferentes para los dos posibles mercados de aplicaciones. Alternativamente, los 68HC11

pueden configurarse en un modo del single-chip, donde actúa como un microprocesador simple

que usa su propia memoria interna limitada y capacidades de I/O. Ahora, hechemos un vistazo

más a detalle de este dispositivo flexible.

Estructura de chip y características internas

Un diagrama a bloques de la estructura del 68HC11 se muestra en la figura 2-3. Como usted

puede ver, hay varias funciones integradas en el dispositivo. Las funciones interiores del chip le

darán una preparación para el estudio extenso, a lo largo de éste viaje.

Fig. 2-3

Estructura de hardware interna en el 68HC11

CPU

6800

CONVERTIDOR

A/D

RAM

256 x 8

68HC11

I/O

PARALELO

CLOCK

ROM

8k x 8

I/O

SERIAL

EEPROM

512 x 8

TIMER

PROGRAMAB

LE

26

DL3155M24HC11

EL CPU

Los 68HC11 contiene una versión mejorada de los 6800 Motorola. Los registros del CPU se

muestran en Figura 2-4.

7

A

0

7

B

0

15

D

0

Acumulador de 8 bit, A y B,

Acumulador D

15

IX

0

Registro Indice X

15

IY

0

Registro Indice Y

15

SP

0

Apuntador de Pila (Stack Pointer)

15

PC

0

7

Contador de Programa (Program

Counter)

0

S X H I N Z V C

Registro de código de condición.

Acarreo

Sobreflujo

Zero

Negativo

Mascara de

interrupción- IRQ

Medio acarreo o

semiacarreo

Mascara de interrupción

XIRQ

STOP deshabilitado

Fig. 2-4

Los registros del CPU 68HC11

EL RELOJ INTERNO

El 68HC11 emplea un circuito del reloj interno que opera por un cristal externo. El circuito de

reloj interno divide la frecuencia del cristal externa entre cuatro, para obtener la frecuencia de

reloj. Los 68HC11 pueden operarse arriba de 2.1 MHz usando un cristal de 8.4 MHz.

27

DL3155M24HC11

RAM INTERNA

La RAM interna del 68HC11 es 256 bytes. Esta RAM empieza en la dirección 000016 y se

extiende a la dirección 00FF16.

ROM INTERNA

La ROM interna de 12K byte es una programación mascarable, localizada en las direcciones

E00016 a FFFF16. Por supuesto, dado que la ROM es no mascarable, ud debe proporcionar un

programa hacia el chip del fabricante para ser mascarado dentro de la ROM.

EPROM INTERNA

Recuerde que la memoria EEROM es principalmente de lectura. Es decir, puede ser de

escritura y lectura bajo un control de programa. Además, EEROM es no-volátil, siendo atractiva

para usarse al final de un programa largo en el almacenamiento de los datos. Los 68HC11

contienen 512 bytes de EEROM interna localizados en la dirección B60016 a B7FF16. La

información puede escribirse hacia y leída desde la EPROM vía un registro de control interno

especial llamado el registro PPROG.

I/O PARALELO

El 68HC11 proporciona 38 líneas I/O paralelas para interfaces externas, dependiendo de su

modo de operación. La mayoría de estas líneas pueden programarse como entradas o salidas,

por un registro interno asociado, dirección datos. Muchas de las líneas paralelas I/O, también

sirven como una función dual para dar otras características de I/O.

I/O SERIE

Las I/O serie es comunicación y transferencia de datos, un bit en un momento, contra I/O

paralelo qué involucra comunicación datos de multi-bit. Brevemente, hay dos tipos de

comunicaciones serie: asíncrono y síncrono. El 68HC11 tienen internamente la capacidad para

dar ambos tipos de comunicación I/O serie. La sección I/O serie asíncrona del chip 68HC11 se

llama la Interface de Comunicaciones Serie, o SCI. La sección I/O serie síncrona se llama la

Interface Periférica Serie, o SPI.

EL TIMER INTERNO PROGRAMABLE

Los timers programables se utilizan para dar retardos de tiempo, generar señales y pulsos de

control, mide tiempos entre eventos externos, y mide la duración de pulsos externos, sólo para

mencionar algunas de sus aplicaciones.

EL CONVERTIDOR DE A/D INTERNO

El mundo real es analógico, de tal modo que si se desea sensar y controlar los eventos que en

él existen, debe convertirse la señal analógica a señal digital, y entregarla al MPU. Éste es el

trabajo de un convertidor analógico a digital, o A/D. El 68HC11 incluye un convertidor de A/D de

28

DL3155M24HC11

8 canales que pueden usarse para convertir ocho señales analógicas separadas en un valor

digital de 8-bit y procesar por el MPU.

LAS LÍNEAS DE LA CONEXIÓN DEL 68HC11

Para interconectar el microprocesador a los circuitos de soporte o dispositivos externos, es

importante estar familiarizado con la asignación de los pines, las líneas del control, etc. Por ello,

antes de iniciar los comentarios al respecto, necesitamos esta al tanto de las opciones de

configuración generales. El 68HC11 es un dispositivo muy complejo. Primeramente, existen dos

modos de que puede configurarse, como: single-chip o multiplexado. Cuando esta en su modo

de single-chip(chip sencillo), el 68HC11 es un microprocesador completamente autónomo, con

su propio componentes internos como el CPU, memoria y capacidades I/O. Configurado así, en

modo single-chip, es sumamente ventajoso cuando se emplea para las aplicaciones dedicadas

o especializadas, como en instrumentación, y automóviles, sólo para mencionar unos. De

hecho, algunos los fabricantes del automóvil incorporan el modo de single-chip del 68HC11, en

sus productos. Cuando se configura en su modo de single-chip, no hay datos externos o bus de

direcciones disponible, por consiguiente, usted no puede conectar un dispositivo periférico

como un A/D al 68HC11. Solo puede usar las capacidades interiores del dispositivo.

Cuando el 68HC11 se configuran en su modo multiplexado, la configuración de sus pines se

cambia para proporcionar un bus de datos externo de 8-bits y un bus de direcciones de 16-bits.

Como resultado, usted puede interconectar memoria externa y dispositivos periféricos I/O al

68HC11 en este modo.

La figura 2-5 muestras un diagrama funcional de los pines del 68HC11 cuando se configura en

su modo multiplexado. La figura 2-5, muestra la versión del 68HC11 en su paquete cuadrado, o

quad de 52-pines. Hay también otra versión de que es un paquete de doble línea o DIP de 48pines. Observe el punto u orificio, marcado al centro del dispositivo. Esta marca se usa para

localizar el pin 1. De este punto, el pin numerando desde el pin 1 al pin 52, se ubica en sentido

contrario a las manecillas del reloj.

Pin 1, es etiquetado como Vss. Éste es el pin de tierra.

Pines 2 y 3 se etiquetan como MODB y MODA, respectivamente. Estos dos pines se usan para

configurar el 68HC11 en su modo operación durante un operación reset. La lógica aplicada a

estos pins configura el chip de acuerdo a la tabla siguiente:

Tabla 1-1

Configuración del modo de operación

MOD B

1

1

MOD A

0

1

Modo Seleccionado

Single-chip

Multiplexado

29

DL3155M24HC11

LINEAS

DEL

CONVERTIDOR

LINEAS DEL A/D

BUS DE DATOS

Y PARTE BAJA

DEL BUS DE

DIRECCIONES

PARTE SUPERIOR

DEL BUS DE

DIRECCIONES

MC 68HC11

52-FN

I/O

SERIE Y PARALELO

TIMER PROGRAMABLE

Y I/O PARALELO

Fig. 2-5

Pines del 68HC11 asignados en configuración modo multiplexado.

Pin 4 se etiqueta AS, correspondiendo a Address Strobe. La línea AS es una línea de salida

que indica que el 68HC11 han generado una dirección en el bus de direcciones. Cuando la

línea de AS es alta, una dirección dentro del bus de direcciones está presente. Cuando AS es

bajo, los datos están en el bus de datos. Usted averiguará brevemente que el 68HC11

multiplexa medio bus de direcciones y el bus de datos en los mismos ocho pines. El uso

primario para la línea AS, es separar, o demultiplexar, las señales de dirección y datos.

Pin 5 se etiqueta como E que simboliza línea de Enable. Ésta es una línea de salida que genera

una señal de reloj necesario para temporizar el sistema. Esto es requerido en todos los circuitos

para sincronizar la transferencia de datos entre el MPU, la memoria y los dispositivos periféricos

I/0.

Pin 6 la línea Read/Write (R/W), indica a la memoria o los dispositivos periféricos sí el MPU

está en modo lectura o escritura. Una operación de lectura se indica un "1" en esta línea. En

este modo, el MPU lee datos desde la memoria o desde un dispositivo de entrada. Una

operación de escritura es indicada por un "0" en la línea R/W. En este modo, el MPU manda

datos a memoria o a un dispositivo de salida.

Los próximos dos Pines (7 y 8) se etiqueta EXTAL y XTAL, respectivamente. Aquí es donde ud

debe conectar el cristal para generar la frecuencia de reloj interna E. Un oscilador de cristal,

típico, se muestra en la figura 2-6A. Note que la frecuencia de cristal debe ser cuatro veces la

30

DL3155M24HC11

frecuencia de reloj E deseada (4 x E). El diagrama en la figura 2-6B muestra cómo usted puede

usar un circuito oscilador externo para generar una señal de reloj E. La salida del oscilador

debe ser compatible a CMOS y debe aplicarse a la línea de EXTAL al pin 7. La frecuencia de

reloj E, será la frecuencia de oscilador entre cuatro. Con este método de generación, la señal

de reloj se utiliza y la línea de XTAL a la izquierda, en el pin 8, no es conectada.

CRISTAL

4XE

OSCILADOR

EXTERNO

4XE

SIN CONEXIÓN

Fig. 2-6

(A) Cristal conectado al 68HC11

(B) Conexión de un oscilador externo

Pins 9 -16 son multiplexados para servir con un propósito dual:

§ Cuando la línea AS es alta, los pines 9-16 generan las ocho líneas de dirección más

bajas (A0 - A7), del bus de direcciones externo.

§ Cuando la línea AS es baja, los pines 9-16 generan las ocho líneas de datos (D0 - D7)

del bus de datos externo.

Así, el bus de datos y la mitad más baja del bus de direcciones son multiplexados en estas

ocho líneas, se ahorra el número total de pines requerido para el chip. Por supuesto, la

información de datos y direcciones debe separarse, o demultiplexarse, externamente para

interconectarlos en orden al 68HC11.

La línea de 2%S%T (pin 17) se usa para restablecer e iniciar el MPU cuando el sistema es

inicialmente energizado o en el momento que se desee inicializar el sistema, Cuando esta línea

va a su nivel lógico "0", el MPU inicia la secuencia de reset. Recuerde que el vector reset es

recuperado desde las direcciones FFFE16 y FFFF16. Este vector se carga dentro del contador de

programa para que la primera instrucción de la rutina de reset sea buscada desde esa

dirección. Esta capacidad se usa para dirigir el MPU al inicio del programa monitor o de control.

31

DL3155M24HC11

La línea 8)21 pin 18 es básicamente línea de entrada de interrupción no mascarable. Un nivel

lógico 0 aplicado a esta línea, causa que el MPU atienda al vector de interrupción nomascarable en las direcciones FFF416 y FFF516. El vector localizado en estas direcciones está

cargado en el contador del programa para que el MPU inicie la ejecución con la primera

instrucción de la rutina servicio de interrupción. No olvide que una instrucción RTI debe

aparecer al final de la rutina de servicio para volver al MPU, al lugar donde ocurrió la

interrupción.

La línea )21 pin 19 es línea de petición de interrupción mascarable. Recuerde que esta

interrupción se ignora, si la bandera I del registro código de condición (CCR) es 1. Cuando una

señal activa aparece en esta línea, el MPU primero verifica que la bandera I en el CCR sea 1.

Si es así, la interrupción es ignorada. Si la bandera I está limpia(0), el MPU recibe el vector de

interrupción I21 desde las direcciones FFF216-FFF316 y lo cargan dentro del contador de

programa. La ejecución empieza entonces con la primera instrucción de la rutina servicio de

interrupción. Después use una instrucción RTI al final de la rutina, para regresar a donde la

interrupción fue generada. Un punto final sobre I21: puede configurarse como una interrupción

para sensar flanco o nivel (level or edge). Después de restablecerse, el pin I21 se configura

automáticamente como interrupción para sensar el nivel activo bajo. Así, un nivel lógico "0"

aplicado al pin 19 comienza la secuencia de la interrupción. Además, el pin de )21 puede ser

configurado por software como interrupción de flanco negativo disparado. En este modo, un

flanco de alto-a-bajo aplicado al pin 19 comienza la secuencia de interrupción. Esta opción

puede ser seleccionada configurando el bit 5 del Registro interno Option en la dirección

hexadecimal 003916 . Usted encontrará durante sus experimentos que hay aplicaciones tanto

para interrupciones por niveles o por flancos.

Pins 20-25 proporcionan I/O serie y paralelo hacia y desde el 68HC11.

Pin 26 es etiquetado como VDD . Esto es donde la fuente de energía a +5V DC se conecta.

Pins 27-34 provee como propósito general las I/O paralelo y la característica de un timer

interno.

Las 8 líneas superiores del bus de direcciones (A8 - A15) se generan vía los pins 35 - 42. La

línea de dirección A15, se da en el pin 35, A14 en el pin 36, y así sucesivamente, finalizando

con la línea de dirección A8 en el pin 42. Recuerde que las 8 líneas bajas del bus de datos (A0 A7) son multiplexadas con el bus de datos sobre los pines 9-16, respectivamente.

Pins 43 - 50 proporcionan acceso a un convertidor analógico a digital interno. Pueden aplicarse

ocho señales analógicas separadas a esta línea para su conversión interna a un valor digital de

8-bits.

Finalmente, las líneas VRL y VRH en los pins 51 y 52, respectivamente, son usadas para aplicar

un voltaje de la referencia externo para el uso del convertidor analógico-a-digital interno.

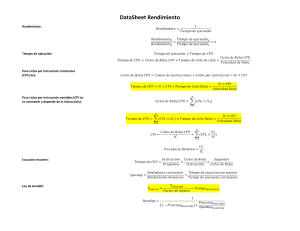

Tiempo de instrucción

Antes de continuar, discutiremos la relación de temporización entre las diversas señales del bus

y de control. Esta discusión inicia con lo más básico en una relación de temporizando: la

temporización por una sola instrucción.

32

DL3155M24HC11

Para ilustrar esto, se describirán los eventos significativos realizados durante la

búsqueda(fetch) y ejecución de la instrucción LDAA #(inmediato), que es una instrucción de 2bytes. El primer byte es el código de instrucción (8616). El segundo byte es el número que será

cargado al acumulador A. Esta instrucción requiere dos ciclos MPU. Durante el primer ciclo, el

código de instrucción es buscado y decodificado. Durante el segundo ciclo, el operando es

recuperado de la memoria y colocado al acumulador A.

Los eventos correspondientes se ilustran en Figura 2-7. Note que los eventos ocurren en el

flanco del pulso de reloj E. Asuma entonces que en la prioridad al tiempo 1 el contador del

programa contiene la dirección de la instrucción LDAA #.

1.09

Microsegundo

s

1.09

Microsegundo

s

Ciclo del MPU

(FETCH,

Búsqueda)

Ciclo del MPU

(EJECUCIÓN)

Fig. 2-7

Temporización de la instrucción LDAA#

Al tiempo 1, la dirección es transferida desde el contador de programa al bus de dirección a

través del registro dirección de memoria. Note que esto ocurre en el filo de caída de la señal E.

Las líneas AS y R/W no están en lógica 1, y deben cambiar a ésta lógica. Un estado lógico 1

en AS indica que una dirección está siendo colocada en el bus de direcciones. El estado lógico

1 en R/W indica a que el MPU desea leer el byte en la dirección indicada.

Al tiempo 2, es el borde de subida del reloj E. En este momento, el contador de programa será

incrementado en uno, a la dirección del siguiente byte en memoria. Sin embargo, este no

cambiará la dirección sobre el bus de dirección. Recuerde que la dirección actual es

conservada dentro del registro dirección de memoria. Así, la dirección de salida aun esta en el

primer byte de la instrucción LDAA #.

Los eventos que ocurren durante el reloj E, comienzan desde dentro del propio MPU. Además,

la señal de reloj E es vista por los circuitos periféricos tal y como el MPU. Así, la RAM, ROM,

etc., son controlados por el reloj E.

El filo de elevación, del reloj E en el tiempo 2, también forza a la memoria a colocar el dato

desde la dirección indicada hacia el bus de datos. Recuerde que este es el código de operación

para la instrucción LDAA #, o 86 16. Observe que la dirección ha tenido estabilidad desde el

tiempo 1 al tiempo 2.

Al tiempo 3 en el borde de caída de la señal, el MPU acepta el byte desde el bus de datos. El

bus de datos tiene estabilidad de tiempo 2 a tiempo 3. El MPU transfiere este byte (8616) al

registro instrucción. Allí, se decodifica e interpreta como el código de operación LDAA #. Esto le

33

DL3155M24HC11

dice al MPU que el próximo byte en memoria, es el operando que será cargado al acumulador

A.

Esto completa el primer ciclo del MPU. Durante este ciclo, el código de operación fue

simplemente leído desde la memoria y decodificado. Esto corresponde a la fase de búsqueda

para nuestro MPU. Observe que un ciclo MPU corresponde a un ciclo del reloj. Ahora veamos

lo que ocurre durante el segundo ciclo, o fase de ejecución de la instrucción.

Al tiempo 3, la dirección del operando también es transferido desde el contador de programa al

bus de direcciones. Al tiempo 4, el contador de programa se incrementa en uno en anticipación

de la siguiente fase de búsqueda.

Continuando, el borde de elevación del reloj E al tiempo 4, causan que él operando sea

transferido desde la memoria al bus de datos. Al tiempo 5, él operando es conservado dentro

del MPU donde este es transferido al acumulador A. Esto completa el segundo ciclo MPU y la

fase de ejecución de la instrucción. El tiempo 5 también representa el inicio de fase de

búsqueda de la próxima instrucción. La ejecución de la instrucción LDAA # requirió dos ciclos

MPU, o dos ciclos del reloj. Asumiendo que el reloj es de 920 kHz, se requiere

aproximadamente 2.18 microsegundos para ejecutar esta instrucción (1.09 por cada byte).

Temporizado de un segmento del programa

Ahora que usted está familiarizado con la temporización de una sola instrucción, podrá

entender el proceso para la ejecución de un programa muestra, donde se agrupan diversas

instrucciones.

Podrá estudiar las relaciones de temporización entre las señales del bus, señales de reloj, la

línea R/W, etc.,

Nuestro segmento de programa muestra se ve en la Figura 2-8. Usando el modo de

direccionamiento inmediato, se carga el 0716 dentro del acumulador A carga y suma 2116. El

resultado se guarda entonces en localidad 0001 16. Note que la primera instrucción reside en la

dirección 001016.

DIRECCION

HEX.

0010

0011

0012

0013

0014

0015

0016

CONTENIDO

HEX.

86

07

8B

21

97

01

….

CONTENIDO HEX/.

MNEMONICO

LDAA #

07

ADDA #

21

STAA

01

…

COMENTARIOS

Carga el acumulador A con el dato inmediato #07

Suma al acumulador A, el dato inmediato # 21

Almacena el resultado en esta dirección

Siguiente instrucción

Fig. 2-8

Segmento de un programa muestra

La figura 2-9 ilustra la relación entre temporizaciones. El pulso de reloj E se muestra en la parte

superior del diagrama. La información que aparece sobre los buses y la línea R/W para cada

periodo del reloj se muestra en la parte de abajo. Este segmento de programa requiere ocho

34

DL3155M24HC11

ciclos de reloj, o ciclos MPU. Éstos están enumerados del uno al ocho. Veamos lo que ocurre

durante cada uno de estos ciclos.

1.09

Microsegundos

Bus de

Direcciones

Bus de

Datos

Línea

R/W

Fig. 2-9

Temporización del segmento del programa muestra.

Ciclo 1. Durante el primer ciclo, la dirección de la instrucción LDAA # (001016) es colocada en el

bus de direcciones. Como resultado, el código de operación 86, es leído desde esa dirección y

buscado por el MPU. Debido a que fue una operación de lectura, la línea R/W está en su

estado lógico 1. El MPU decodifica el código de operación y reconoce que éste es una

instrucción LDAA #. Por consiguiente, sabe que el próximo byte en memoria es él operando que

será cargado en el acumulador. Durante este ciclo, el contador del programa se incrementó a

001116, para que ahora apunte al operando.

Ciclo 2. Ésta es la fase de la ejecución de la instrucción LDAA #. La dirección del código del

operando (001116) es colocada sobre el bus de direcciones. El código de operación (0716) es

leído afuera, sobre el bus de datos y colocado en el acumulador A. En el proceso, el contador

de programa se incrementa a 001216. Esto completa la fase de ejecución de la primera

instrucción.

Ciclo 3. Esta es la fase de búsqueda de la siguiente instrucción. La dirección 0012, es colocada

sobre el bus de direcciones. El código de operación a esa dirección se lee fuera y se coloca en

el bus de datos. El MPU recoge el código de operación, lo decodifica, y descubre que es la

instrucción ADDA #. En el proceso, el contador del programa se incrementa a 001316.

Ciclo 4. Aquí, la dirección 001316 se transfiere al bus de direcciones y la localidad de memoria

seleccionada sé lee. Por tanto, el operando 2116, se pone sobre el bus de datos. El MPU recoge

al operando y lo agrega a los contenidos del acumulador. La suma, 2816, se retiene en el

acumulador A. El contador del programa es incrementado a 001416.

Ciclo 5. Fase de búsqueda para la tercer instrucción. La dirección 001416 se sitúa sobre el bus

de direcciones. El código de operación para STAA se lee y decodifica. El MPU reconoce que es

necesario el modo de direccionamiento directo. Así, interpretará el siguiente byte en memoria

como la dirección donde la suma es acumulada. El contador del programa se incrementa a

0015 16.

Ciclo 6. La dirección 00151 6 se coloca sobre el bus de dirección. Observe que esta localidad es

la dirección donde la suma es almacenada. Así, 01 se lee fuera, hacia el bus de datos donde es

recogido por el MPU. El MPU reconoció que el direccionamiento directo es el indicado y asume

que la dirección donde la suma se guarda es 000116. Esta dirección se guarda en el MPU. El

contador del programa se incrementa a 001616.

35

DL3155M24HC11

Ciclo 7. Durante este ciclo, el MPU se prepara para almacenar la suma. Para ello, debe

transferir la suma desde el acumulador al registro de datos.

Ciclo 8. El MPU está ahora listo para guardar la suma en memoria. La dirección donde guardará

la suma (000116) es colocada sobre el bus de dirección. El dato a almacenar (2816) es situado

sobre el bus de datos. La línea de R/W se cambia a estado bajo, indicando que ésta, es una

operación de almacenaje, y la suma (2816) se guarda en la localidad de memoria 000116.

Por supuesto, la computadora no se pausa aquí. Durante el próximo ciclo, la próxima

instrucción es buscada y decodificada. Sin embargo, los ocho ciclos de la máquina ilustrados en

Figura 2-9 dan la idea general. Posteriormente verá, que las relaciones de temporización, aquí

mostradas, son importantes en las interfaces que realizará el MPU con memorias y circuitos

I/O.

36

DL3155M24HC11

2.3 MODELO DE PROGRAMACIÓN DEL MC68HC11

El 68HC11 es mucho más compleja que nuestra MPU hipotética. Consecuente-mente, un

modelo de programación del 68HC11 supone un buen comienzo. Este se muestra en la Figura

2-10.

7

0 7

A

B

0

15

D

0

Acumulador de 8 bit, A y B, o el

acumulador doble D

15

IX

0

Registro Indexado X

15

IY

0

Registro Indexado Y

15

SP

0

15

PC

0

7

Apuntador de Pila (Stack Pointer)

Contador

Counter)

de

Programa

(Program

0

S X H I N Z V C

Registro de código de condición.

Acarreo o préstamo de MSB

Sobreflujo

Zero

Negativo

Mascara de interrupción- I

Medio acarreo o semiacarreo (del bit

3)

Mascara de interrupción X

Paro deshabilitado

Fig. 2-10. Modelo de programación del MPU 68AC11

Usted notará inmediatamente que el 68HC11 tiene algunos registros adicionales. Sin embargo,

sólo dos de ellos, el registro índice y el apuntador de pila son nuevos para usted.

Veamos las diferencias más significativas entre MPU y nuestro modelo hipotético.

37

DL3155M24HC11

Dos Acumuladores. 68HC11 tiene dos acumuladores en lugar de sólo uno. Son llamados

acumulador A (ACCA) y acumulador B (ACCB). Cada uno de ellos cuenta con su propio grupo

de instrucciones asociadas. Los nombres y mnemónicos de las instrucciones especifican cual

acumulador será usado. Así, hay instrucciones como:

Load Accumulator A, LDAA. (Cargar Acumulador A)

Load Accumulator B, LDAB. (Cargar Acumulador B)

Store Accumulator A, STAA. (Almacenar Acumulador A)

Store Accumulator B, STAB. (Almacenar Acumulador B)

Note que se agrega al nombre y al mnemónico para indicar que acumulador va a usarse.

Por experiencia, usted puede visualizar el valor del segundo acumulador. Por ejemplo,

considere un programa en el cual, MPU cuenta el número de veces que ocurre una operación.

Anteriormente, almacenamos el contenido actual del acumulador, cargamos la cuenta en el

acumulador; incrementamos la cuenta, almacenamos la cuenta y volvemos a cargar el numero

original. Con un segundo acumulador, nada de eso es necesario. Sencillamente mantenemos la

cuenta en el acumulador B mientras trabajamos con el acumulador A. De hecho, podemos

efectuar cualquier operación aritmética o lógica de dos números distintos sin tener que

moverlos hacia delante o atrás en la memoria. Como en otros miembros de la familia 6800, los

acumuladores A y B pueden ser concatenados en un solo acumulador, “D” de 16 bits, para

bytes dobles.

Contador de Programa de 16 Bits. El contador de programa en el 68HC11 tiene 16 bits en vez

de 8. Así, se pueden especificar 65,536 direcciones distintas. Esto significa que una

microcomputadora basada en el 68HC11 puede tener hasta 65,536 bytes de memoria.

Afortunadamente, nosotros podemos usar como mínimo o máximo el Byte 216, muchas

aplicaciones requieren menos memoria de este límite máximo. Ya que el contador de programa

tiene 16 bits, el bus de direcciones también debe ser de 16 bits. Contraste esto con el bus de

direcciones de 8 bits de nuestra máquina hipotética.

Usted puede sorprenderse de cómo especificamos una dirección de 16 bits con un byte. La

respuesta obvia es que son necesarios dos bytes de 8 bits. Recuerde que en el modo de

direccionamiento directo, la dirección fue especificada por un byte. El microcontrolador 68HC11

mantiene ese modo de direccionamiento. Sin embargo, ya que una dirección de 8 bits sólo

puede especificar 256 direcciones, el 68HC11 puede usar este modo sólo si el operando se

halla en los primeros 256 bytes de memoria. Para alcanzar direcciones altas, se debe usar un

nuevo modo de direccionamiento llamado direccionamiento extendido. En el modo de

direccionamiento extendido, se usan dos bytes para representar cada dirección. Este modo de

direccionamiento será discutido con más detalle después. Por ahora, tenga en mente que hay

65,536 posibles direcciones. La dirección más baja es la 000016 y la mayor es FFFF16. Usando

direccionamiento extendido, tendremos acceso a cualquier localidad de memoria, pero se

requiere una dirección de 2 bytes.

Registros de Código de Condición.

El 68HC11 tiene ocho bits de código de condición o

banderas. Cada una de ellas puede ser referida por la posición del bit (0-7) o por su nombre en

el registro de código de condición m, mostrado en la Figura 2-10. Cuatro de ellos son muy

similares, casi idénticos a los discutidos anteriormente. Estos incluyen los códigos de condición

negativo (N), Cero (Z), sobreflujo (V), y acarreo (C). En este momento surge una diferencia, por

haber dos acumuladores en el 68HC11. Así, la bandera de acarreo se pone a uno cuando hay

38

DL3155M24HC11

un acarreo de cualquier acumulador. También, un sobreflujo en cualquier acumulador pondrá a

uno la bandera V.

También se muestran cuatro nuevos códigos de condición en la Figura 2-10. La máscara I de

interrupción se usa para deshabilitar (enmascarar) toda interrupción enmascarable. Cualquiera

de ellas puede ser puesta a uno por hardware o a través de instrucción de programa. La

máscara X de interrupción es similar a la máscara I, sin embargo, es activada sólo por

hardware (Reset o XIRQ) y es borrado sólo por instrucción de programa (TAP o RTI). El uso de

estas será discutido después cuando estudie el uso de interrupciones. Ocupando la posición de

un bit entre las máscaras de interrupción I y X está la bandera de medio acarreo ó semiacarreo

(H). la bandera H es puesta a uno cuando hay un acarreo del bit 3 (al 4) del acumulador. La

MPU usa esta bandera para determinar cuando se implementa una instrucción de ajuste

decimal. Finalmente, el último bit de código de condición es: deshabilita STOP o PARO, su

bandera es S. Esta es puesta a uno bajo control del programa para deshabilitar la instrucción

STOP. Cuando STOP es deshabilitado de esta manera, su ejecución del programa es tratada

como una “no-operación” instrucción NOP. NOP será discutida con más detalle posteriormente.

Puesto que las últimas dos banderas de código de condición (X y S) generalmente no se

afectan por muchas de las instrucciones que se discutirán, consideraremos sólo los efectos

sobre las primeras seis banderas de código de condición.

Registros Indice.

Los registros índice IX e IY son registros de 16 bits de propósito especial

que incrementan grandemente la potencia del microprocesador. Estos registros permiten un

modo de direccionamiento muy poderoso llamado direccionamiento indexado.

Analizaremos dicho modo de direccionamiento en esta unidad. Por ahora, considere a los

registros índice como otros registros de trabajo. El hecho que puedan retener dos bytes en

lugar de uno posibilita su buen uso. La MPU tiene instrucciones que permiten que los registros

índice sean cargados desde dos bytes de memoria contiguos. Otra instrucción nos permite

almacenar el contenido de los registros índice en dos localidades de memoria adyacentes. Esto

posibilita mover datos en grupos de 2 bytes. También, los registros índice pueden

incrementarse o decrementarse. Con esto mantenemos cuentas de 16 bits.

La arquitectura de registro índice dual del 68HC11 significa una mejora en diseño sobre

anteriores miembros de la familia 6800. Aunque ambos registros IX e IY pueden ser usados

similarmente para direccionamiento indexado, conteo, o almacenamiento temporal de datos,

ciertas instrucciones, particularmente aquellas para el registro IY, requieren un byte extra, o un

prebyte, de código máquina. La necesidad del prebyte surge como resultado del conjunto

expandido de instrucciones del 68HC11 al agregar nuevas instrucciones no usadas

previamente en la familia 6800.

La agregar el prebyte a una instrucción también provoca que una instrucción de dos bytes

requiera un ciclo extra de tiempo de ejecución (comparado con un opcode de un byte). Más que

como un byte extra del opcode (con tiempo de ejecución extra de un ciclo de máquina), una

instrucción con prebyte se programa y ejecuta como cualquier instrucción ordinaria (sin

prebyte). Los valores típicos del prebyte en el conjunto de instrucciones del 68HC11 son 1816 y

1A16. Los notará cuando estudie el conjunto de instrucciones del MC68HC11 con detalle, un

poco más adelante. Tenga en mente que, cuando se programan instrucciones que requieren

prebytes, el opcode con prebyte apropiado se programa en una localidad de memoria (M), y el

opcode de la instrucción es programado en la siguiente localidad (M+1), como si se tratara de

dos bytes de datos.

39

DL3155M24HC11

2.4 DIAGRAMA A BLOQUES DE MC68HC11

Ahora que ha visto el modelo de programación de la MPU 68HC11, de un vistazo al diagrama

de bloques. Un diagrama simplificado se muestra en la Figura 2-11.

Se han omitido algunas rutas de datos, muchas líneas de control, y un registro de

almacenamiento temporal a favor de los registros y rutas de datos más importantes.

Fig. 2-11. Diagrama a bloques simplificado del MPU

40

DL3155M24HC11

41

DL3155M24HC11

UNIDAD 3

CONJUNTO DE INSTRUCCIONES

42

DL3155M24HC11

CONTENIDO

3.1 CONJUNTO DE INSTRUCCIONES DE MC68HC11

3.2 MODOS DE DIRECCIONAMIENTO

3.3 EXPLICACION DE INSTRUCCIONES

43

DL3155M24HC11

3.1 CONJUNTO DE INSTRUCCIONES DEL MC68HC11

Esas instrucciones pueden ser agrupadas en siete categorías generales. Aunque algunas de

ellas se superponen, la clasificación general de las instrucciones es: aritméticas, manejo de

datos, prueba de datos lógicos, registro índice y apuntador de pila, salto y bifurcación y código

de condición. En esta unidad discutiremos muchas de esas instrucciones en detalle

En esta sección no nos interesaremos en los modos de direccionamiento. Por lo tanto, no

manejaremos opcodes. Los varios modos de direccionamiento y los opcodes los veremos más

adelante. Por ahora identificaremos las instrucciones por sus nombres, mnemónicos y

operaciones. Verá lo que hace cada instrucción y como son afectados los primeros seis

registros de código de condición.

Instrucciones Aritméticas

La Figura 3-1 muestra las instrucciones aritméticas representativas de la MPU 68HC11. El

nombre de cada instrucción se muestra a la izquierda. La siguiente columna contiene el

mnemónico. La columna central da una explicación abreviada de lo que hace la instrucción. La

columna a la derecha muestra como se afectan los primeros seis registros de código de

condición.

* Después de usar ABA, ADC, y ADD en operaciones aritméticas BCD; cada 8 bytes son

considerados como dos números BCD de 4 bit´s. DAA suma 0110 a la mitad del byte bajo, si el

número menos significativo es >1001, o si la instrucción previa causo un semiacarreo. Suma

0110 a la mitad del byte alto si el número más significativo >1001 o si la instrucción anterior

causo un acarreo. También suma 0110 al medio byte superior, si el número menos significativo

>1001 y el número más significativo es = 9.

* NOTA: Los bits 6 y 7, generalmente no se ven afectados por estas instrucciones.

44

DL3155M24HC11

Fig. 3-1 Instrucciones Aritméticas

Para asegurar que la idea es clara, veamos la primera instrucción en detalle. Esta es la

instrucción de suma. Ya que el 68HC11 tiene dos acumuladores, hay dos instrucciones de

suma. Sus mnemónicos son ADDA y ADDB. La última letra indica el acumulador que se usa. La

representación abreviada de la operación es A+MàA. La nota en la parte de arriba de la

columna, register labels indica que las letras se refieren al contenido de los registros. Así, A

significa el contenido del acumulador y M significa el contenido de la localidad de memoria

afectada. El símbolo à significa “transfiere a”. Por lo tanto, A+MàA significa “suma el

contenido del acumulador A al contenido de la localidad de memoria afectada y transfiere la

suma al acumulador A”.

Para ver como son afectadas las banderas de los códigos de condición, simplemente vea a la

derecha el código de condición deseado. Generalmente, los códigos pueden ser activados

según la operación ó no ser probados o afectados. Si no es afectado el código, se marca con el

símbolo (•). Por ejemplo, ninguna de las instrucciones aritméticas afectan la bandera I. Muchas

de las instrucciones aritméticas prueban los códigos de condición y los ponen a uno si existe la

condición. Por ejemplo, si el resultado de una operación aritmética es cero, la bandera Z es

puesta a uno. Si esta condición no existe, la bandera es limpiada. El símbolo (×) significa

“prueba y pon a uno si es verdad; de otra manera, limpia”. Ocasionalmente se necesita una

nota para describir alguna situación inusual del código de condición. Esto se representa con un

número dentro de un círculo. Las notas se dan abajo del dibujo.

Las instrucciones ADDA y ADDB se comprenden fácilmente. La instrucción ABA suma el

contenido del acumulador A al contenido del acumulador B. Y el resultado lo almacena en el

acumulador A.

Las instrucciones de suma con acarreo son idénticas a las discutidas anteriormente para la

máquina hipotética. Note que el bit de acarreo se integra a la suma.

Ya que en el MPU 68HC11 se usa aritmética de complemento a dos, existen instrucciones que

nos permiten obtener el complemento a dos de un número. La instrucción de negación, resta el

contenido del registro afectado de 00 16. Esto es lo mismo que hacer el complemento a dos del

número. El registro afectado puede ser cualquier localidad de memoria (M) o cualquier

acumulador (A o B). Así, hay tres instrucciones de negación distintas. Tenga en mente que

NEG significa “toma el complemento a dos de la localidad de memoria afectada”; NEGA “toma

el complemento a dos del acumulador A”; etc.

Note que la instrucción NEG nos permite operar sobre un byte en memoria sin buscar primero

el operando. Anteriormente, hemos cargado el operando, llevado a cabo la operación y

almacenado entonces el nuevo operando. Sin embargo, el 68HC11 nos permite llevar a cabo

45

DL3155M24HC11

ciertas operaciones sobre el operando, sin primero buscarlo en memoria. Algunos ejemplos de

esto serán mostrados según progresemos con el conjunto de instrucciones.

La instrucción de ajuste decimal efectúa exactamente lo mismo que nuestra máquina hipotética.

La nota inmediatamente debajo de la tabla describe su operación. Debe apuntarse que dicha

instrucción sólo trabaja con el acumulador A.

Las instrucciones de resta y resta con acarreo se explican por sí mismas. El MPU 68HC11 tiene

una instrucción adicional de resta. La instrucción SBA resta el contenido del acumulador B del

contenido del acumulador A. La diferencia resultante se coloca en el acumulador A.

Instrucciones de Manejo de Datos

La Figura 3-2 contiene un listado de las instrucciones más importantes de manejo de datos,

usadas por la MPU 68HC11. Este es el grupo más grande de instrucciones del 68HC11.

Las instrucciones para limpiar, nos permiten borrar el contenido de una localidad de memoria o

de cualquier acumulador. Anteriormente hemos limpiado bytes de memoria limpiando primero el

acumulador y almacenando luego el dato 0016 resultante en la localidad de memoria apropiada.

Sin embargo, la instrucción CLR nos permite despejar una localidad de memoria con una sola

instrucción. Nótese que aparecen algunas entradas nuevas en la columna de registros de

códigos de condición. R significa que el código de condición está siempre a cero. S significa

que el código está siempre a uno.

La instrucción de decremento nos permite restar 1 de la localidad de memoria o de cualquier

acumulador. La instrucción DEC es especialmente valiosa ya que decrementa un byte en

memoria con una sola instrucción. Previamente hemos cargado el byte, lo hemos

decrementado y lo entonces es almacenado atrás en memoria.

Las instrucciones de incremento son similares excepto porque nos permiten sumar uno a una

localidad de memoria o a alguno de los acumuladores. Note que la instrucción INC nos permite

mantener una cuenta en memoria sin tener que cargarla, incrementarla y volverla a almacenar.

Las instrucciones de carga al acumulador son sencillas de entender y fáciles de usar. Note que

el acumulador puede ser cargado desde la memoria.

46

DL3155M24HC11

Fig. 3-2. Instrucciones de manejo de datos

Las instrucciones de rotación a la izquierda nos permiten desplazar el contenido del acumulador

o de una localidad de memoria sin perder bits del dato. Considere a la instrucción ROLA como

un ejemplo. Cuando se ejecuta esta instrucción, el acumulador A y el bit de acarreo forman un

registro circular de 9 bits. Esto es, forman un lazo cerrado como se muestra en la Figura 3-3A.

Cuando se ejecuta ROLA, el dato es rotado en sentido de las manecillas del reloj. El MSB de A

se desplaza al registro de acarreo. Simultáneamente, el contenido de A es desplazado a la

izquierda. Note que el bit de acarreo no se pierde, sino que es desplazado al LSB del

acumulador.

47

DL3155M24HC11

A.

antes que se ejecute la instrucción ROLA

B.

después de ejecutar ROLA

Fig. 3-3. Ejecución de la instrucción ROLA

Aunque la utilidad de esta instrucción no es tan clara, es una herramienta valiosa. Por ejemplo,

podría ser usada para determinar la paridad. Rotando repetidamente a la izquierda y probando

la bandera C, puede determinar el número de 1´s en el byte. Una vez que lo conoce, puede

generar fácilmente el bit de paridad apropiado.

La instrucción ROL le permite rotar un byte de memoria a la izquierda mientras está en

memoria. ROLB posibilita rotar el acumulador B a la izquierda. En cada caso se usa el registro

C como noveno bit.

Las instrucciones de rotación a la derecha son iguales a las de la izquierda, lo que cambia es la

dirección de rotación. La Figura 3-4 ilustra la ejecución de la instrucción RORA. Esta instrucción

también es valiosa. Suponga, por ejemplo, que se desea saber si el número en el acumulador

es par o impar. Esto se determina con el LSB del número. Si LSB = 1, el número es impar; si

LSB = 0, el número es par. Una manera de determinar esto es, rotar el número a la derecha de

manera que el LSB quede en el registro C. Podemos probar el registro C para ver si está a uno

o a cero. Notese que el número debe ser restaurado a su forma original mediante la instrucción

ROLA.

A. Antes de ejecutar RORA

B.

Después de ejecutar RORA

Fig. 3-4. Ejecutando la instrucción RORA

La instrucción aritmética de rotación a la izquierda fué discutida anteriormente para la MPU

hipotética. La instrucción ASLA se ejecuta exactamente como se describió en la unidad previa.

Sin embargo, note que la MPU 68HC11 también tiene la instrucción ASLB que efectúa la misma

operación con el acumulador B. También tiene una instrucción ASL que permite efectuar esta

operación sobre un byte en memoria. La Figura 3-5 ilustra la ejecución de esta instrucción.

48

DL3155M24HC11

A.

B.

Antes de ejecutar ASL

Después de ejecutar ASL

Fig. 3-5. Ejecutando la instrucción ASL

Mientras sólo haya un tipo de instrucción de rotación a la izquierda, hay dos tipos de

instrucciones de rotación a la derecha. Discutamos primero las instrucciones de rotación a la

derecha.

Cuando se ejecuta una instrucción aritmética de rotación a la derecha, el número en el registro

afectado es desplazado una posición a la derecha. El LSB pasa al registro C. B1 se desplaza a

B0, etc. B7 se desplaza a B6. Sin embargo, B7 permanece sin cambio. La Figura 3-6 ilustra la

ejecución de la instrucción ASRB. Note que también se listan las instrucciones ASRA y ASR en