Metodología de diseño

Diseño y aplicación de circuitos combinacionales SSI

Análisis circuital de circuitos digitales.

El análisis de un circuito digital no sólo conlleva la extracción de su funcionamiento lógico, sino la

medición también de sus parámetros físicos como tiempo de propagación o potencia disipada, ya

sea por la extracción de los datos de las hojas de características o por simulación del circuito.

La potencia disipada por un circuito digital se calcula como la suma de la potencia disipada por

cada uno de los dispositivos que lo forman.

Para obtener el tiempo de propagación de un circuito hay que buscar y encontrar el camino

crítico: el camino que genera el mayor tiempo de propagación.

La obtención del tiempo de propagación máximo es más exacta cuanto mejor será el modelo

temporal que se utiliza para los componentes del circuito. Por ejemplo, un modelo muy sencillo,

pero poco real, es considerar que todas las puertas tienen el mismo tiempo de propagación, el

mayor camino de propagación será el que tiene más puertas lógicas.

Es más fiable utilizar los parámetros de los componentes indicados por el fabricante, donde

normalmente aparecen los tphl y tplh. Por ejemplo, para TTL LS:

Al estudiar el camino crítico hay que tener en cuenta que los tiempos de las puertas son distintos,

e incluso los tiempos tplh y tphl de una misma puerta también pueden ser distintos.

Peligros lógicos

Los peligros lógicos son un fenómeno que se produce en los circuitos digitales debido a los

diferentes tiempos de propagación por caminos entre dos mismos puntos del circuito. En los

circuitos combinacionales no producen un error lógico significativo, salvo el indeseado aumento

del consumo de potencia dinámica debido a la carga y descarga de los condensadores internos del

circuito. En circuitos secuenciales asíncronos pueden producir un mal funcionamiento lógico.

Los peligros generados por los cambios simultáneos de varias entradas (peligros funcionales) no

son evitables, pero sí lo son los producidos por el cambio de una única entrada (peligros lógicos).

Los peligros lógicos pueden ser estáticos: la señal no debe cambiar, pero tiene una transición

indeseada, o dinámicos: la señal debe cambiar, pero lo hace varias veces antes de estabilizarse.

Circuitos tan sencillos como estos pueden presentar peligros, producidos por los diferentes

tiempos de propagación a través del camino con inversor y sin él, lo que hace que

momentáneamente las dos entradas de la puerta AND estén a 1, o que las dos entradas de la

puerta OR estén a 0.

La existencia de peligros en un circuito se estudia mediante un sistema algebraico en que X y X son

variables distintas. La conclusión que se obtiene es que para realizar un circuito libre de peligros

lógicos estáticos y dinámicos, todo par de 1s (en SOP o 0s en POS) de la función adyacentes en un

Mapa de Karnaugh deben ser cubiertos por un implicante primo común.

Implementaciones en dos niveles

Las implementaciones en dos niveles pueden realizarse utilizando sólo puertas NAND, sólo puertas

NOR o algunas combinaciones de puertas en primer nivel/segundo nivel que se pueden comportar

como AND/OR (SOP) u OR/AND (POS). Las combinaciones NAND/NAND y NOR/NOR generan

circuitos SOP y POS.

Para comprobar si una relación concreta de puertas en primer nivel/segundo nivel se puede usar

para implementar formas SOP o POS hay que representar las puertas de forma que entre el primer

y el segundo nivel coincida la polaridad. Si al hacerlo en un nivel las puertas son OR y en el otro

AND sí se puede, si los dos niveles son AND u OR no se puede.

Implementaciones multinivel

Las expresiones factorizadas están formadas por un conjunto de niveles AND/OR/AND/OR/…. Las

puertas NAND pueden realizar las operaciones AND y OR, de tal forma que entre nivel y nivel las

polaridades de las señales coinciden por lo que las operaciones se realizan de forma natural. Lo

mismo ocurre con las puertas NOR. Una vez realizadas las operaciones lógicas con las puertas

lógicas adecuadas se finaliza el circuito aplicando las entradas (complementadas o no) a las líneas

correspondientes, y obteniendo la salida con la polaridad correcta.

Diseño y aplicación de circuitos combinacionales MSI

Decodificadores

Un decodificador es un circuito lógico con n entradas y 2 n salidas, tal que para cada combinación

de entradas se activa al menos una salida. Si sólo se activa una salida se denomina decodificador

completo. Por ejemplo, este es un circuito decodificador completo de 3 a 8 líneas, permitiría la

activación de un dispositivo al proporcionarle la dirección de dicho dispositivo. Dispone de una

entrada de habilitación (enable) que conecta o desconecta el dispositivo, en este caso dicha

entrada es activa a nivel bajo, ya que el dispositivo se activa cuando dicha entrada recibe un ‘0’

lógico.

Los decodificadores pueden dividirse en diferentes tipos:

EXCITADORES (DRIVERS) que controlan algún dispositivo.

NO EXCITADORES, los que no se usan para dicho fin.

Tanto las entradas como las salidas, principalmente estas últimas, pueden ser:

ACTIVAS A NIVEL ALTO: la salida activa es 1 y la no activa 0.

ACTIVAS A NIVEL BAJO: la salida activa es 0 y la no activa 1.

Además, el número de entradas de Habilitación puede ser de una o más, y pueden estar activas a

nivel alto o bajo. Podemos encontrar decodificadores de muy diversos “tamaños”:

De 2 a 4 líneas

De 3 a 8 líneas (bin a oct)

De 4 a 16 líneas (bin a hex)

Convertidores de códigos: BCD/decimal y BCD/7-seg

Realización de funciones con decodificadores

Un circuito decodificador completo genera todos los productos fundamentales (minitérminos) de

las variables de entrada. Cuando las salidas del decodificador son activas a nivel bajo, para realizar

la función en suma de productos basta con conectar las salidas correspondientes a los

minitérminos de la función usando puertas NAND:

A veces puede ocurrir que necesitemos decodificar más líneas de las que nos permite nuestro

circuito, se bebe entonces construir un decodificador de mayor tamaño usando decodificadores de

menor tamaño:

Convertidores de códigos

Son circuitos Codificadores/Decodificadores que convierten los datos de un código a otro.

Codificadores

Son los dispositivos MSI que realizan la operación inversa a la realizada por los decodificadores.

Generalmente, poseen 2 n entradas y n salidas. Cuando solo una de las entradas está activa para

cada combinación de salida, se le denomina codificador completo. Por ejemplo, el siguiente

circuito proporciona a la salida la combinación binaria de la entrada que se encuentra activada. En

este caso se trata de un codificador completo de 8 bits, o también llamado codificador de 8 a 3

líneas:

Las salidas codificadas, generalmente se usan para controlar un conjunto de 2n dispositivos,

suponiendo claro está que sólo uno de ellos está activo en cualquier momento. Sin embargo,

cuando nos encontremos con que se deben controlar dispositivos que pueden estar activos al

mismo tiempo, problema que se suelen encontrar los sistemas microprocesadores, es preciso usar

un dispositivo que nos proporcione a la salida el código del dispositivo que tenga más alta

prioridad.

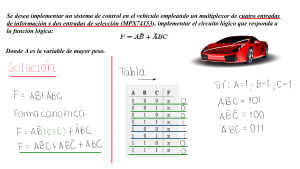

Multiplexores

Multiplexar es pasar información de “muchos” canales o líneas a “pocos” canales o líneas. Un

multiplexor (MUX) es un circuito combinacional que selecciona una entrada y la transfiere a la

salida. La selección de la entrada, o dato, se realiza según un conjunto de valores de las variables

de control. Poseen, por tanto, n entradas de selección, para 2 n entrada de datos, proporcionando

dos salidas: una para el dato directo y otra para el dato negado. A continuación, se presenta la

tabla de funcionamiento y el Símbolo lógico estándar para un multiplexor de 8 a 1 líneas. Se trata

del circuito 74X151, con entrada de habilitación activa a nivel bajo.

Existen en el mercado diferentes multiplexores. El siguiente corresponde al 74153, que es un

circuito MSI con dos Mux de 4 a 1 líneas. A los Mux se les suele llamar también selectores de

datos. Así este sería un selector de datos 1-de- 4 (ya que selecciona un dato de cuatro

disponibles).

El diagrama lógico sobre estas líneas corresponde a la configuración interior del dispositivo arriba

descrito, lo que nos puede dar una idea de la diferencia entre los circuitos SSI y los MSI.

FLIP-FLOP JK, SR, D, T

Diseño y aplicación de circuitos secuenciales con MSI

Conclusión

Fuentes

https://personales.unican.es/manzanom/Planantiguo/EDigitalI/Tema_IV.pdf

https://es.slideshare.net/eddnewoscar/unidad-3-70005095

https://es.wikipedia.org/wiki/Integración_a_baja_escala

https://sites.google.com/site/logicadigitalweb/home/unidad-v/circuitos-combinacionales-msi-y-lsi

http://paginas.fisica.uson.mx/horacio.munguia/aula_virtual/Recursos/Combinacionales%20MSI.p

df

0

0