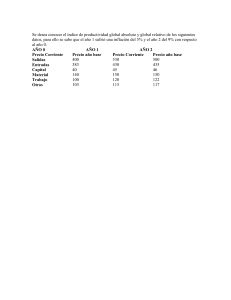

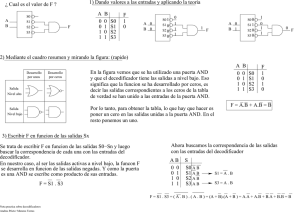

INSTITUTO TECNOLOGICO DE SAN LUIS POTOSI INGENIERIA MECATRONICA ELECTRONICA DIGITAL “PROBLEMAS DE ELECTRONICA COMBINACIONAL 1-10” ALUMNO Arturo Zavala Ortega MAESTRO Vázquez Rivera José Álvaro Soledad de graciano Sánchez, SLP. 30 abril 2020 INTRODUCCION. Los circuitos combi nacionales son, como su nombre lo sugiere, circuitos cuya salida depende solamente de la “combinación” de sus entradas en el momento que se está realizando la medición en la salida. Analizando el circuito con compuertas digitales que se muestra, se ve que la salida de cada una de las compuertas que se muestran en el circuito, depende únicamente de sus entradas (A y B), ya sea que estén negadas o sin negar. La salida F (salida final o total del circuito) variará si alguna de las entradas A o B o las dos a la vez cambian. Los circuitos de lógica combi nacional son hechos a partir de las compuertas básicas: compuerta AND, compuerta OR, compuerta NOT. También pueden ser construidos con compuertas NAND, compuertas NOR, compuerta XOR, que son una combinación de las tres compuertas básicas. La operación de los circuitos combi nacionales se entienden escribiendo las ecuaciones booleanas y sus respectivas tablas de verdad. En este ejemplo la ecuación booleana es: F = A.B’+A’.B Dónde: A’ es “A negado” y B’ es “B negado” Se puede observar de la tabla de verdad que la última columna “Salida F” sólo depende de las entradas A y B actuales. Este diagrama y su respectiva tabla de verdad son un ejemplo específico. Otros diagramas pueden tener más entradas (A, B, C,…etc.), más salidas (F1, F2, F3,…, etc.) y habría que obtener la tabla de verdad para cada salida en función de las entradas existentes. Nota: Las salidas en otros circuitos combi nacionales pueden estar en cualquier parte dentro del diagrama del circuito. Problema 1: Diseña un sistema combinacional operable para multiplicar dos números binarios de 2 Bits cada uno de ellos. El resultado se mostrará en un número de 4 Bits. Para este ejercicio se realizará primero la tabla de la verdad, luego los mapas de karnaugh y finalmente el circuito. Desarrollo Se realizara el circuito de un multiplicador de dos números de 2 bits, que mostrará el resultado en un display 7. Haciendo uso exclusivamente de compuertas lógicas. Máximo resultado 9 Mínimo resultado 0 = No negado 1 = Negación La multiplicación se realiza mediante una tabla de verdad as entradas son los dos números a multiplicar y la salida el resultado. Así es como se ve terminado el circuito realizando un correcto funcionamiento. Problema 2: Diseñe un sistema combinacional con la posibilidad de sumar cuatro números binarios de un solo bit cada número. El resultado se mostrará en un número de 3bits. Desarrollo. Para este ejercicio, al igual que el número 1, se realizará primero la tabla de la verdad, luego los mapas de karnaugh y finalmente el circuito. Los números binarios corresponden a A, B, C y D. Las salidas X, Y, Z. A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 X 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 Y 0 0 0 1 0 1 1 1 0 1 1 1 1 1 1 0 Z 0 1 1 0 1 0 0 1 1 0 0 1 0 1 1 0 Mapa de Karnaugh. X = ABCD AB A𝐵̅ 𝐴̅𝐵̅ 𝐴̅𝐵 X=ABCD CD 1 0 0 0 ̅ C𝐷 0 0 0 0 ̅ 𝐶̅ 𝐷 0 0 0 0 𝐶̅ 𝐷 0 0 0 0 Para Y Y AB A𝐵̅ 𝐴̅𝐵̅ 𝐴̅𝐵 CD 0 1 1 1 ̅ C𝐷 1 1 0 1 ̅ 𝐶̅ 𝐷 1 0 0 0 𝐶̅ 𝐷 1 1 0 1 ̅ 𝐶̅ 𝐷 0 1 0 1 𝐶̅ 𝐷 1 0 1 0 6 grupos. ̅ + 𝐵̅𝐶 (𝐴 + 𝐷) + 𝐶̅ 𝐷(𝐴 + 𝐵) + 𝐴̅𝐵𝐶 Ecuacion 𝑌 = 𝐴𝐵𝐷 Par a Z Z AB A𝐵̅ 𝐴̅𝐵̅ 𝐴̅𝐵 - CD 0 1 0 1 ̅ C𝐷 1 0 1 0 No hay grupos. ̅ ) + (𝐴𝐵 + 𝐴̅𝐵̅)(𝐶𝐷 ̅ + 𝐶̅ 𝐷) 𝑍 = (𝐴𝐵̅ + 𝐴̅𝐵)(𝐶𝐷 + 𝐶̅ 𝐷 SIMULACION PROTEUS. PROBLEMA 3. Diseñe un sistema combinacional operable para restar dos números binarios de dos bits cada número, tomando en cuenta una salida S adicional al resultado, que indique con 0 cuando la salida sea positiva o nula (S = 0), y con 1 cuando la diferencia sea negativa (S = 1). Desarrollo. W X Y Z F S 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 -1 -1 -1 1 0 -1 -1 1 1 0 -1 1 1 1 0 0 1 1 1 0 0 1 1 0 0 0 1 0 0 0 0 Ahora realizaremos el Mapa de Karnaugh para poder conocer las ecuaciones que nos dará el circuito. Por medio de mapas de Karnaugh se resolvió para obtener la función de suma de productos. PARA F F WX* WX* W*X* W*X YZ 0 0 0 0 Y Z* 1 0 0 0 Y*Z* 1 1 0 1 Y*Z 1 1 0 0 F= W.X.Z*+X.Y*.Z*+W.Y* F=X.Z*(W.y*) Para la función de “S”, tomamos el siguiente mapa tomando los 1’s para la función expresada en minitérminos PARA S S YZ YZ* Y*Z* Y*Z WX WX* W*X* W*X 0 1 1 1 0 0 1 1 0 0 0 0 0 0 1 0 S=W*.X*.Z+X*.Y.Z+W*.Y S=X*.Z.(W*+Y)+W*.Y* Simulación del circuito. Comprobando la tabla de verdad Simulacion. PROBLEMA 4 Diseñe un sistema multiplexor (selector datos) de 4 a 1 líneas. Como entradas de datos: L0, L1, L2, L3. Como entradas de control: A y B. y como salida: Y Desarrollo. L0 L1 L2 L3 A B Y 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 1 1 0 1 0 1 LO L1 L2 L3 Y=LOB´A´+LIBA´+L2B´+L3BA Diagrama Debido a que son muchas entradas se simulo en logisim. PROBLEMA 5. Diseñe un sistema combinacional capaz de indicar la decisión de aceptada o rechazada de una propuesta, cuando el porcentaje de las acciones a favor sea mayor o igual al 60 por ciento. Tomando en cuenta que la empresa tiene cuatro accionistas y donde el accionista A tiene el 40%, el B el 30%, el C el 20% y el D el 10%, en función de la votación de cada uno de los accionistas a favor = 1 o en contra = 0, el sistema deberá indicar con un uno (Y = 1) en la salida Y si cumple con el 60% o más, de lo contrario notificará con un cero (Y = 0). En este programa como son 4 entradas se obtienen 16 combinaciones. Para poder llenar la tabla de verdad se tomará en cuenta el valor de cada accionista se realizará la suma para saber con cual combinación se obtiene un 1 y se encenderá el led en los demás casos el led permanecerá apagado, cuando el accionista A y B estén de acuerdo, cuando B, C, y D estén de acuerdo A y C estén de acuerdo y en el caso que todos estén de acuerdo, en todos los demás casos estará el led apagado. Tabla de verdad: Ecuación booleana: Se utilizara OK para saber si es aceptada la propuesta por el 60% de los accionistas. En el siguiente diagrama realizado en el programa PROTEUS se muestra la conexión para comprobar el funcionamiento del problema planteado. PROBLEMA 6. Un sistema de alarma contra incendios se conectará a cuatro conmutadores X1, X2, X3 y X4. Si se activa uno de estos conmutadores deberá encenderse una sirena S1. Si se activan dos o más conmutadores en forma simultánea deberán dar aviso la sirena S1 y una segunda sirena S2. Desarrollo. Se tienen 4 entradas por lo que tendremos 16 posibles variaciones. Cada que se active un conmutador se encenderá 1 alarma cada que se activen 2 o más conmutadores se activaran las dos alarmas. Tabla de verdad: Expresiones boolenas: Para la alarma 1 o salida 1 (D1). Para la alarma 2 o salida 2 (D2). En la siguiente figura se muestra el diagrama que soluciona el problema y obtenido con las expresiones booleanas. PROBLEMA 7. (ENCODER) Diseñe un sistema combinacional que contenga cinco entradas llamadas L5, L4, L3, L2 y L1 capaz de indicar (mediante un código binario S2, S1, S0) cuál entrada tiene valor 1. En caso de que se presenten dos o más unos (1) en la entrada, la salida tomará el valor de la línea de mayor peso, (considere L5 la más significativa). Desarrollo. En este programa se tienen 5 entradas por lo tanto tenemos 32 combinaciones. En este programa se realizará una comparación de número mayor o menor y a la vez se convertirá de numero base 10 a número de base 2, si se escogen dos o más líneas en la salida se representará en número binario la de mayor valor, por ejemplo, si se escogen L1 y L4 en la salida se observará 4 en binario (100). Tabla de verdad: Con la tabla de verdad anterior se encuentran las siguientes expresiones booleanas Para S1 (D1): Para S2 (D2): Para S3 (D3): En la siguiente figura se muestra el diagrama que se formó con las expresiones booleanas: PROBLEMA 8. (DECODER) Diseñe un sistema combinacional de tres entradas llamadas A, B y C con ocho salidas llamadas S7, S6, S5, S4, S3, S2, S1, S0, de manera que cuando la entrada sea igual a A = 0, B = 0 y C = 0, sólo la salida S0 sea igual a 1. Si la entrada es igual a A = 0, B = 0 y C = 1, sólo la salida S1 sea igual a 1 y así sucesivamente, hasta que la entrada sea A = 1, B = 1 y C = 1; entonces sólo la salida S7 será igual a 1. Desarrollo. Decodificador de 3 a 8 En esta sección, implementemos de 3 a 8 decodificadores tiene tres entradas A 2 , A 1 y A 0 y ocho salidas, Y 7 a Y 0 Podemos encontrar el número de decodificadores de orden inferior necesarios para implementar el decodificador de orden superior utilizando la siguiente fórmula. Por lo tanto, requerimos dos decodificadores de 2 a 4 para implementar un decodificador de 3 a 8. El diagrama de bloques del decodificador de 3 a 8 que usa de 2 a 4 decodificadores se muestra en la siguiente figura. Las entradas paralelas A 1 y A 0 se aplican a cada decodificador de 2 a 4. El complemento de la entrada A 2 está conectado a Enable, E del decodificador inferior de 2 a 4 para obtener las salidas, Y 3 a Y 0 . Estos son los términos inferiores de cuatro minutos . La entrada, A 2 está directamente conectada a Habilitar, E del decodificador superior de 2 a 4 para obtener las salidas, Y 7 a Y 4 . Estos son los términos superiores de cuatro minutos simulacion PROBLEMA 9. (DEMULTIPLEXOR) Diseñe un sistema combinacional que contenga una entrada de dato D0, dos entradas de control C1, C0 y cuatro señales de salida llamadas Y0, Y1, Y2 y Y3, de manera que si la entrada de control es C1= 0, C0 = 0, la salida Y0 tomará el valor del D0 y las demás salidas tomarán el valor de 0. Si la entrada de control es C1 = 0, C0 = 1, la salida Y1 tendrá el valor del D0 y las demás salidas el valor de 0. Si la entrada de control es C1 = 1, C0 = 0, la salida Y2 tomará el valor del D0 y las demás salidas el valor de 0. Si la entrada de control es C1=1, C0=1, la salida Y3 tendrá el valor del D0 y las demás salidas el valor de 0. Desarrollo. Siguiendo la definición La función del demultiplexor será cambiar una línea de entrada de datos común a cualquiera de las 4 líneas de datos de salida A a D en nuestro ejemplo anterior. Al igual que con el multiplexor, los interruptores de estado sólido individuales se seleccionan mediante el código de dirección de entrada binaria en los pines de selección de salida " a " y " b " como se muestra. Selección de línea de salida del demultiplexor Al igual que con el circuito multiplexor anterior, al agregar más entradas de línea de dirección, es posible cambiar más salidas dando una salida de línea de datos de 1 a 2 n. Algunos IC demultiplexores estándar también tienen un pin adicional de "habilitar salida" que deshabilita o evita que la entrada pase a la salida seleccionada. También algunos tienen pestillos incorporados en sus salidas para mantener el nivel lógico de salida después de que se hayan cambiado las entradas de dirección. Sin embargo, en los circuitos de tipo de decodificador estándar, la entrada de dirección determinará qué salida de datos individuales tendrá el mismo valor que la entrada de datos, mientras que todas las demás salidas de datos tienen el valor lógico "0". La implementación de la expresión booleana anterior utilizando puertas lógicas individuales requeriría el uso de seis puertas individuales que consisten en puertas AND y NOT , como se muestra. Simulación PROBLEMA 10. Diseñe un sistema combinacional de 5 entradas E4, E3, E2, E1, E0 que contenga 3 salidas, de manera que la primera S2, señale un 1 las combinaciones de entrada que sean números primos, la segunda S1 que indique de la misma forma las combinaciones pares, y la última salida S0, las combinaciones impares. Desarrollo. Como se tienen 5 entradas, tenemos un número máximo de 32 combinaciones (por que 2 =32) cuyos valores van del 0 al 31 en binario, ahora se identifica cuales números tienen la propiedad de ser, par, impar y primo. 5 Se define como número par, un número natural que es divisible entre dos. Se trata de un número entero que se puede escribir de la forma: 2k (donde k es un entero). En nuestra combinación de números, identificamos como números pares: 0,2,4,6,8,10,12,14,16,18,20,22,24,26,28,30. Se define como número impar, un número natural que no es divisible entre dos y pueden escribirse de la forma 2k+1 (donde k es un entero). En nuestra combinación de números, identificamos como números impares: 1,3,5,7,9,11,13,15,17,19,21,23,25,27,29,31. Se define como número primo, un número natural mayor que 1 que tiene únicamente dos divisores distintos: él mismo y el 1. En nuestra combinación de números, identificamos como números primos: 2,3,5,7,11,13,17,19,23,29,31. Una vez identificados los números y sus propiedades se dibuja una tabla de verdad con 3 salidas, S2, S1, S0 donde S2 tendrá un 1 cuando la combinación de entrada tenga un número primo, S1 tendrá un 1 cuando la combinación de entrada tenga un número par y S0 tendrá un 1 cuando la combinación de entrada tenga un número impar. ENTRADAS SALIDAS E4 E3 E2 E1 E0 S2 S1 S0 0 0 0 0 0 0 0 1 0 1 0 0 0 0 1 0 0 1 2 0 0 0 1 0 1 1 0 3 0 0 0 1 1 1 0 1 4 0 0 1 0 0 0 1 0 5 0 0 1 0 1 1 0 1 6 0 0 1 1 0 0 1 0 7 0 0 1 1 1 1 0 1 8 0 1 0 0 0 0 1 0 9 0 1 0 0 1 0 0 1 10 0 1 0 1 0 0 1 0 11 0 1 0 1 1 1 0 1 12 0 1 1 0 0 0 1 0 13 0 1 1 0 1 1 0 1 14 0 1 1 1 0 0 1 0 15 0 1 1 1 1 0 0 1 16 1 0 0 0 0 0 1 0 17 1 0 0 0 1 1 0 1 18 1 0 0 1 0 0 1 0 19 1 0 0 1 1 1 0 1 20 1 0 1 0 0 0 1 0 21 1 0 1 0 1 0 0 1 22 1 0 1 1 0 0 1 0 23 1 0 1 1 1 1 0 1 24 1 1 0 0 0 0 1 0 25 1 1 0 0 1 0 0 1 26 1 1 0 1 0 0 1 0 27 1 1 0 1 1 0 0 1 28 1 1 1 0 0 0 1 0 29 1 1 1 0 1 1 0 1 30 1 1 1 1 0 0 1 0 31 1 1 1 1 1 1 0 1 Ahora se obtienen las ecuaciones booleanas. Al tener mas de 5 entradas el método de mapa de Karnaugh deja de ser práctico, por que lo que se puede recurrir al método QuineMcCluskey o por software. En este caso se utiliza el software Logisim. Una vez introducidos los datos nos entrega los siguientes resultados. Para S2 Para S1 Para S0 Se arma el circuito en el simulador y se comprueba su funcionamiento. En la figura siguiente se comprueba la combinación del número 19 con la que esperamos se active S2 (primo) y S0 (impar). SIMULACION