registros de control y estado

Anuncio

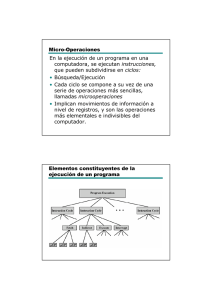

UCLV 1 Mapas conceptuales para la enseñanza de Arquitectura de Computadoras REGISTROS DE CONTROL Y ESTADO Hay diversos registros de la CPU que se emplean para controlar su funcionamiento, la mayoría de ellos, en muchas máquinas, no son visibles por el usuario. Algunos de ellos pueden ser visibles a instrucciones de máquina ejecutadas en un modo de control o de SO. Naturalmente máquinas diferentes tendrán diferentes organizaciones de registros y usarán distinta terminología. Son esenciales cuatro registros para la ejecución de una instrucción: Contador de programa (PC) contiene la dirección de la instrucción a captar. Registro de instrucción (IR) contiene la instrucción captada más recientemente. Registro de dirección de memoria (MAR) contiene la dirección de una posición de memoria. Registro intermedio de memoria (MBR) contiene la palabra de datos a escribir en memoria, o la palabra leída más recientemente. Normalmente, la CPU actualiza el contador de programa después de cada captación de instrucción, de manera que siempre apunta a la siguiente instrucción a ejecutar. Una instrucción de bifurcación o salto también codificará el contenido de PC. La instrucción captada se carga en IR, donde se analiza el código de operación y los campos del operando. Se intercambian datos con la memoria por medio de MAR y de MBR, en un sistema con organización de bus, MAR se conecta directamente al bus de direcciones y MBR directamente al bus de datos. Los registros visibles por el usuario intercambian repetidamente datos con MBR. Los cuatro registros mencionados se usan para la transferencia de datos entre la CPU y la memoria. Dentro de la CPU, los datos tienen que ofrecerse a la ALU para su procesamiento, la ALU puede tener acceso directo a MBR y a los registros visibles para el usuario. Como alternativa, puede haber registros intermedios adicionales en torno a la ALU, estos sirven como registros de I/O de la ALU, e intercambian datos con MBR y los registros visibles. Todos los diseños de la CPU incluyen un registro o conjunto de registros, conocidos a menudo como palabra de estado del programa (PSW), que contiene información de estado. PSW contiene normalmente códigos de condición, además de otra información de estado. Entre los campos o indicadores se incluyen los siguientes: Signo: contiene el bit de signo del resultado de la última operación aritmética. Cero: puesto a uno cuando el resultado es 0. Acarreo: puesto a uno si una operación da lugar a un acarreo (suma) o a un adeudo (resta) del bit más significativo. Se usa en operaciones aritméticas multipalabras. Igual: puesto a uno si el resultado de una comparación lógica es igualdad. Desbordamiento: usado para indicar un desbordamiento aritmético. UCLV 2 Mapas conceptuales para la enseñanza de Arquitectura de Computadoras Interrupciones habilitadas/inhabilitadas: usado para permitir o inhabilitar interrupciones. Supervisor: indica si la CPU funciona en modo supervisor o usuario, únicamente en modo supervisor se pueden ejecutar ciertas instrucciones privilegiadas y se puede acceder a ciertas áreas de memoria. En algún diseño concreto de la CPU es posible encontrar otros registros relativos a estado y control. Además de PSW, puede existir un puntero a un bloque de memoria que contenga información de estado adicional (por ejemplo, bloques de control de procesos). En las máquinas que usan interrupciones vectorizadas puede existir un registro de vector de interrupción. Si se utiliza una pila, para llevar a cabo ciertas funciones (llamada a subrutina), se necesita un puntero de pila de sistema. En un sistema de memoria virtual se usa un puntero a la tabla de páginas, por último, pueden utilizarse registros para el control de operaciones de E/S. En el diseño de la organización de los registros de control y estado entran en juego varios factores, una cuestión importante es el soporte el SO. Algunos tipos de información de control son de utilidad específica para el SO. Si el diseñador de la CPU posee una comprensión funcional del SO que se va a utilizar, la organización de los registros puede adaptarse, hasta cierto punto, a ese SO. Otra decisión clave en el diseño, es la distribución de la información de control entre registros y memoria, es frecuente dedicar los primeros (más bajos) pocos cientos o miles de palabras de memorias para fines de control, el diseñador debe decidir cuánta información de control debiera estar en registros y cuánta en memoria. Surge el habitual compromiso entre coste y velocidad.